MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-14 Freescale Semiconductor

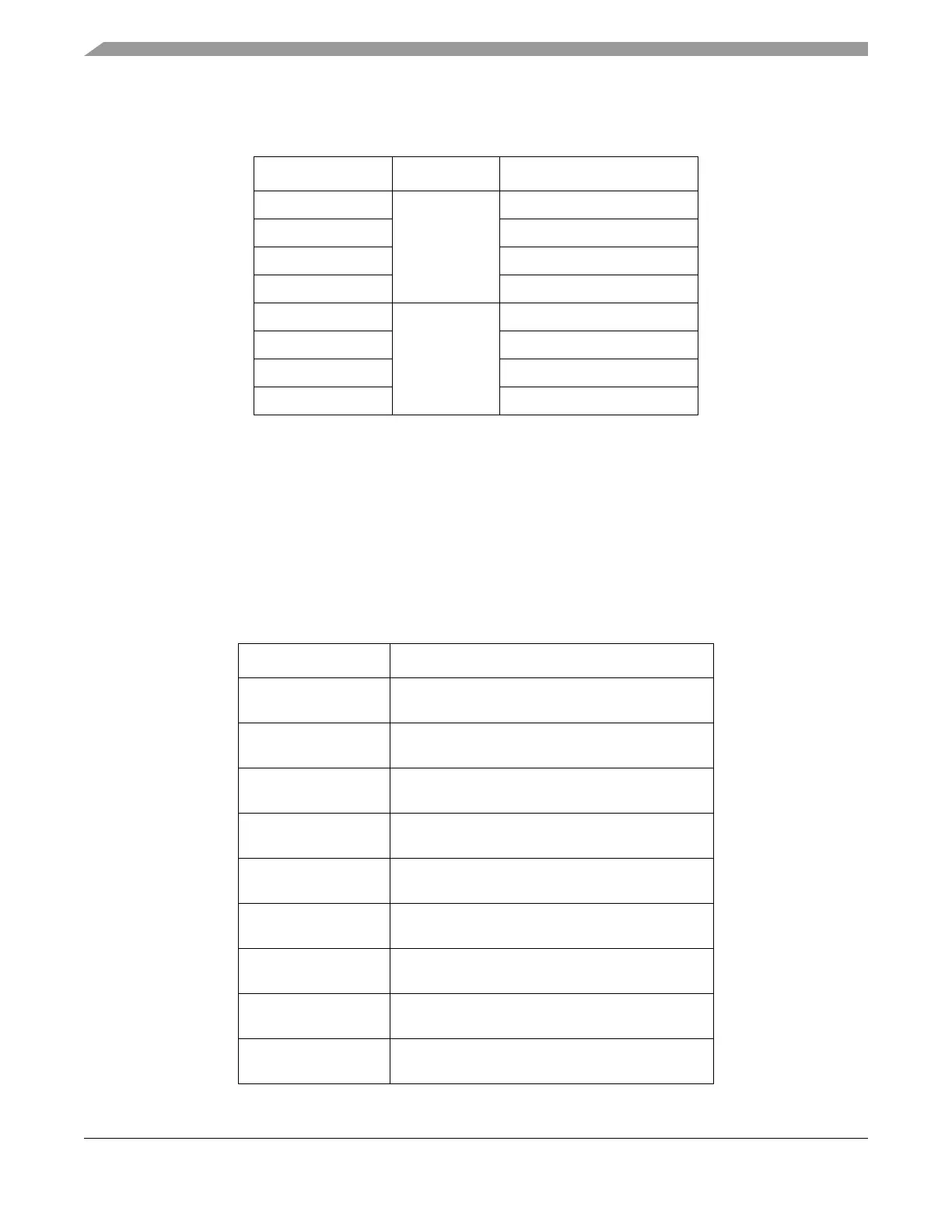

The output disable channel groups are defined in Table 18-4.

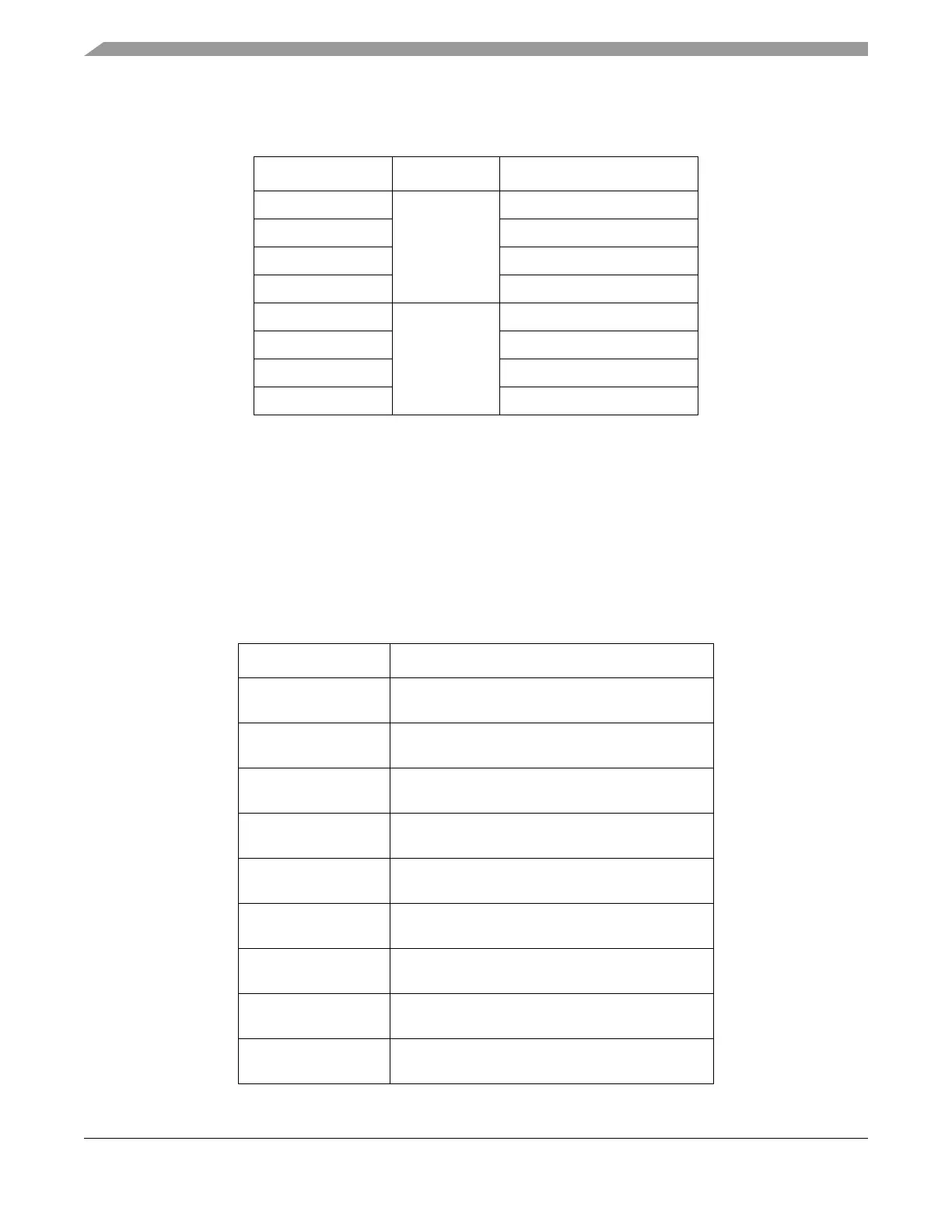

18.4 Memory Map/Register Definition

18.4.1 Memory Map

The eTPU system simplified memory map is shown in Table 18-5. The base address for the eTPU module

is listed as BASE. Each of the register areas shown may have their own reserved address areas.

Table 18-5 shows a detailed memory map.

Table 18-4. Output Disable Channel Groups

eMIOS Channel Engine eTPU Channels Disabled

11

A

0–7

10 8–15

9 16–23

8 24–31

20

B

0–7

21 8–15

22 16–23

23 24–31

Table 18-5. eTPU High-Level Memory Map

Address Register Description

Base–

Base + 0x0_001F

eTPU system module configuration registers

Base + 0x0_0020–

Base + 0x0_002F

eTPU A time base registers

Base + 0x0_0030–

Base + 0x0_003F

Reserved

Base + 0x0_0040–

Base + 0x0_004F

eTPU B time base registers

Base + 0x0_0050–

Base + 0x0_01FF

Reserved

Base + 0x0_0200–

Base + 0x0_02FF

eTPU[A:B] global channel registers

Base + 0x0_0300–

Base + 0x0_03FF

Reserved

Base + 0x0_0400–

Base + 0x0_07FF

eTPU A channel registers

Base + 0x0_0800–

Base + 0x0_0BFF

eTPU B channel registers

Loading...

Loading...