MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 3-13

3.3 Functional Description

The following sections describe the function of the various blocks within the e200z6 core.

3.3.1 Memory Management Unit (MMU)

The memory management unit (MMU) is an implementation built on the Power Architecture embedded

category with a 32-entry fully associative translation lookaside buffer (TLB). The Power Architecture

divides the effective and real address space into pages. The page represents the granularity of effective

address translation, permission control, and memory/cache attributes. The e200z6 MMU supports the

following nine page sizes: 4K, 16K, 64K, 256K, 1M, 4M, 16M, 64M, and 256M.

3.3.1.1 Translation Lookaside Buffer (TLB)

The TLB consists of a 32-entry, fully associative content addressable memory (CAM) array. To perform a

lookup, the CAM is searched in parallel for a matching TLB entry. The contents of this TLB entry are then

concatenated with the page offset of the original effective address. The result constitutes the real (physical)

address of the access. Table 3-2 shows the TLB entry bit definitions.

The TLB is accessed indirectly through several MMU assist (MAS) registers; refer to Section 3.3.1.5,

“MMU Assist Registers (MAS0–MAS4, MAS6) and the e200z6 PowerPC

TM

Core Reference Manual for

more details. Software can write and read the MMU Assist registers with mtspr (move to SPR) and mfspr

(move from SPR) instructions. These registers contain information related to reading and writing a given

entry within the TLB. Data is read from the TLB into the MAS registers with a tlbre (TLB read entry)

instruction. Data is written to the TLB from the MAS registers with a tlbwe (TLB write entry) instruction.

3.3.1.2 Translation Flow

The effective address, concatenated with the address space value of the corresponding MSR bit (MSR[IS]

or MSR[DS], is compared to the appropriate number of bits of the EPN field and the TS field of TLB

entries. If the contents of the effective address plus the address space bit matches the EPN field and TS bit

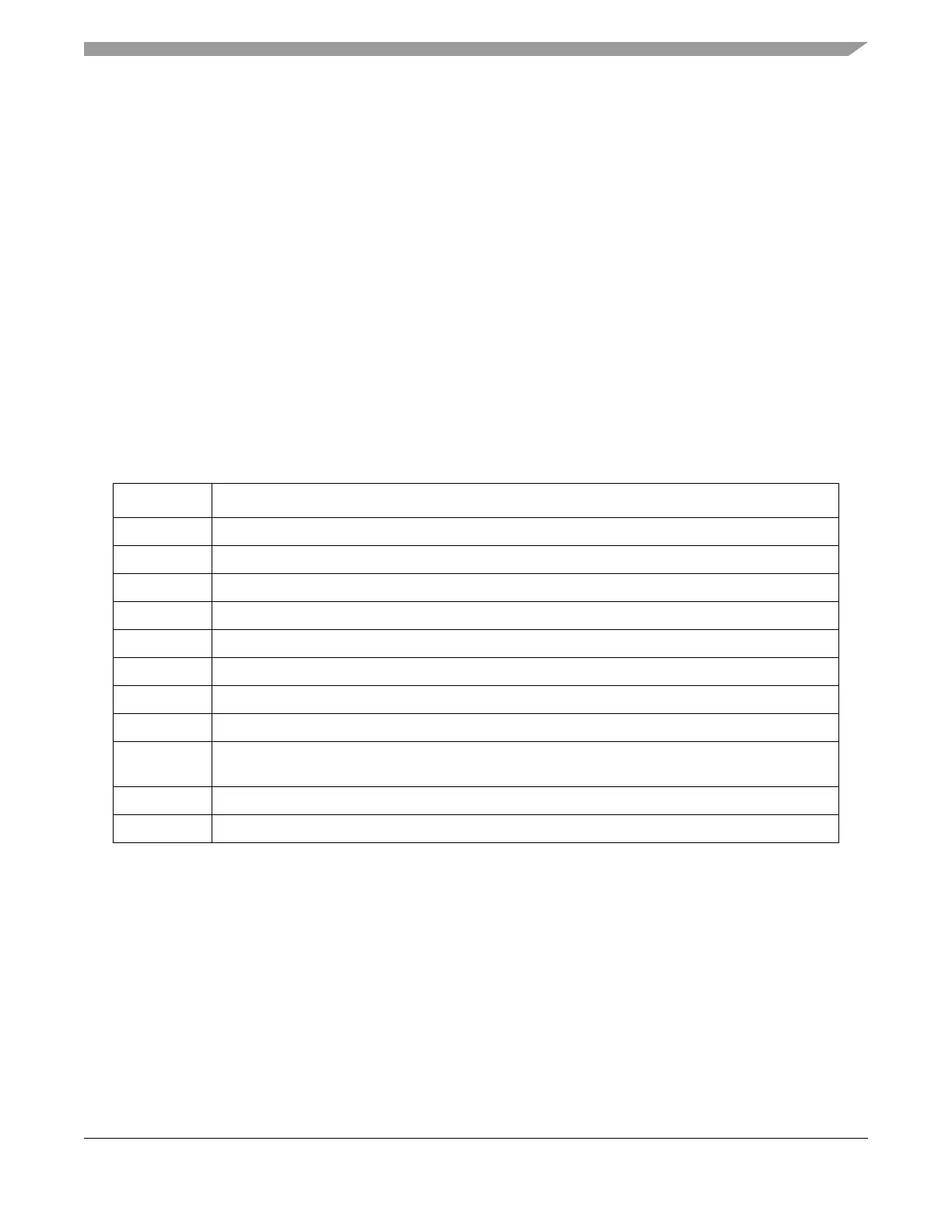

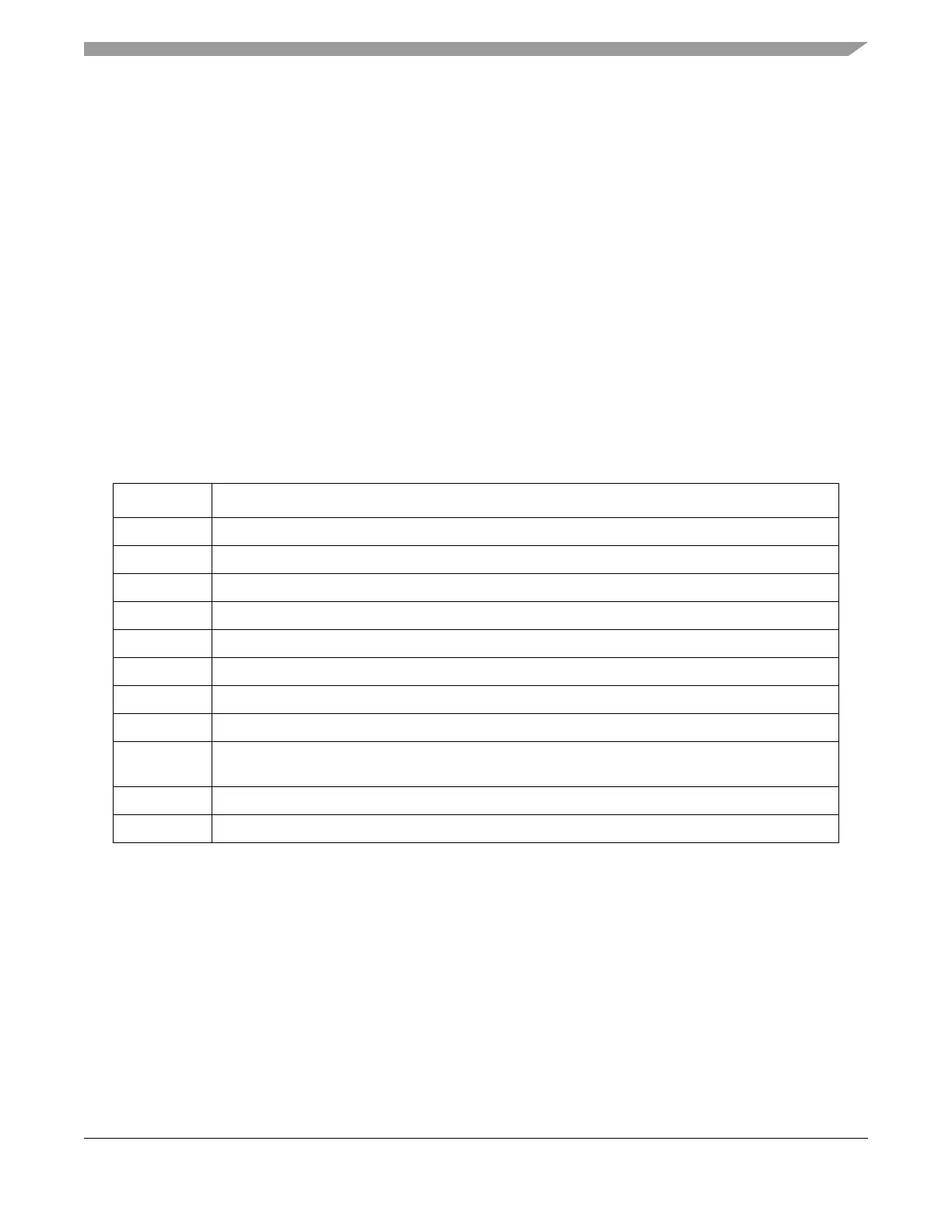

Table 3-2. TLB Entry Bit Definitions

Field Comments

V Valid bit for entry

TS Translation address space (compared against AS bit)

TID[0:7] Translation ID (compared against PID0 or ‘0’)

EPN[0:19] Effective page number (compared against effective address)

RPN[0:19] Real page number (translated address)

SIZE[0-3] Page size (4K/16K/64K/256K/1M/4M/16M/64M/256Mbytes)

SX, SW, SR Supervisor execute, write, and read permission bits

UX, UW, UR User execute, write, and read permission bits

WIMGE Translation attributes (Write-through required, cache-Inhibited, Memory coherence required,

Guarded, Endian)

U0-U3 User bits -- used only by software

IPROT Invalidation protect

Loading...

Loading...