MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-14 Freescale Semiconductor

of the TLB entry, that TLB entry is a candidate for a possible translation match. In addition to a match in

the EPN field and TS, a matching TLB entry must match with the current process ID of the access (in

PID0), or have a TID value of 0, indicating the entry is globally shared among all processes.

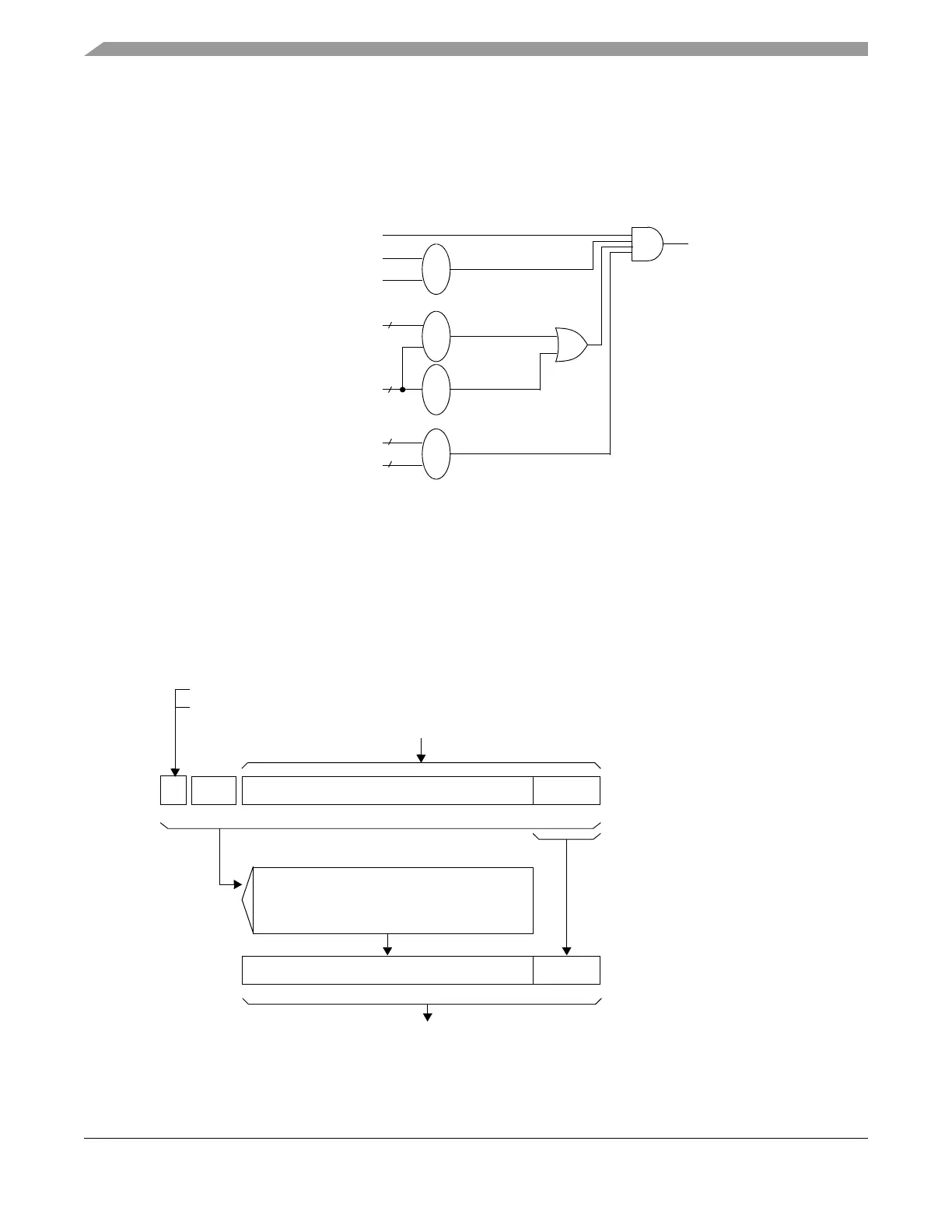

Figure 3-4 shows the translation match logic for the effective address plus its attributes, collectively called

the virtual address, and how it is compared with the corresponding fields in the TLB entries.

Figure 3-4. Virtual Address and TLB-Entry Compare Process

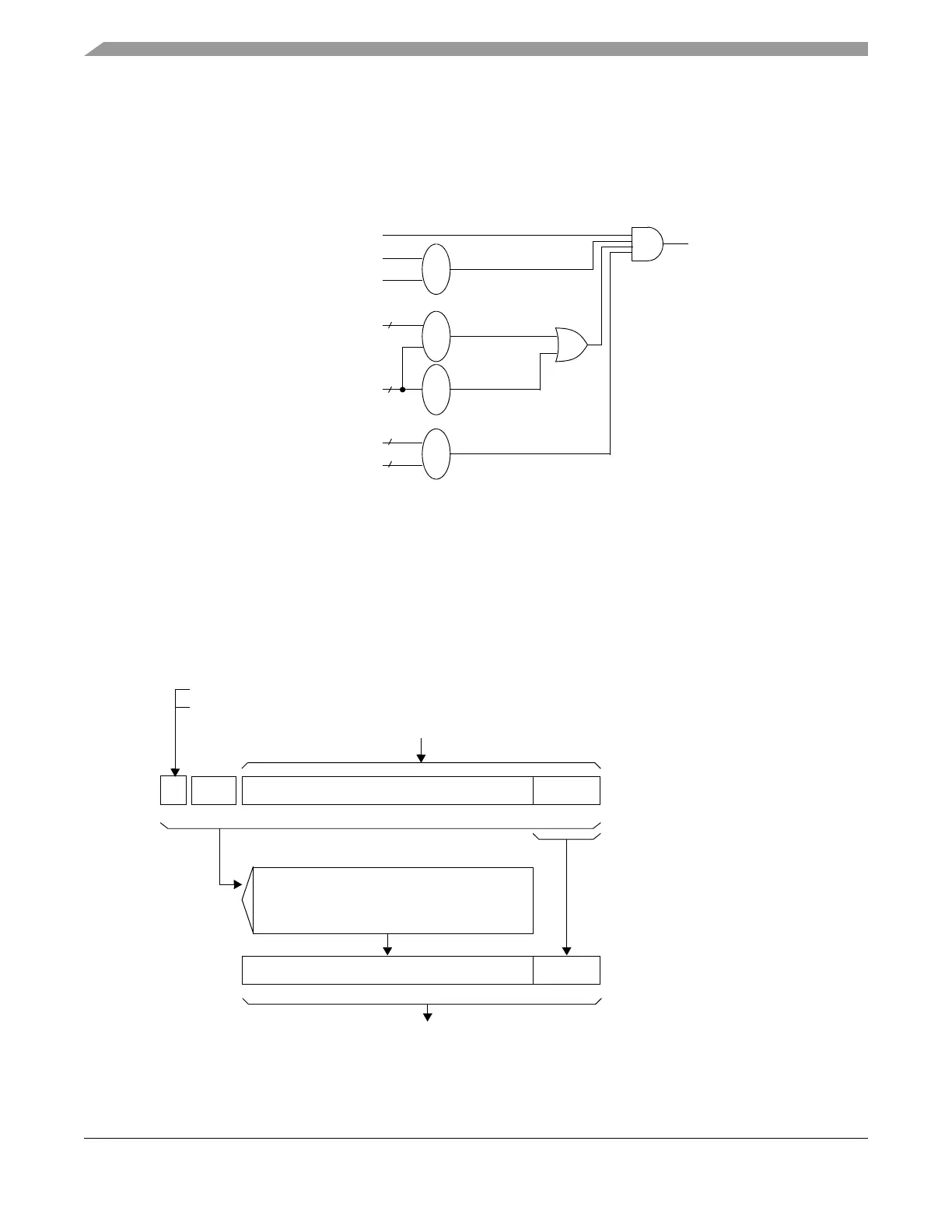

3.3.1.3 Effective to Real Address Translation

Instruction accesses are generated by sequential instruction fetches or due to a change in program flow

(branches and interrupts). Data accesses are generated by load, store, and cache management instructions.

The instruction fetch, branch, and load/store units generate 32-bit effective addresses. The MMU translates

this effective address to a 32-bit real address which is then used for memory accesses. Figure 3-5 shows

the effective to real address translation flow.

Figure 3-5. Effective to Real Address Translation Flow

TLB entry Hit

=0?

private page

shared page

=?

=?

TLB_entry[V]

TLB_entry[TS]

AS (from MSR[IS] or MSR[DS])

Process ID

TLB_entry[TID]

TLB_entry[EPN]

EA page number bits

=?

32-bit Effective Address

32-bit Real Address

Virtual Address

PID Effective Page Address Offset

031

TLB

multiple-entry

MSR[IS] for instruction fetch

AS

MSR[DS] for data access

RPN field of matching entry

n–1 n

Real Page Number Offset

031

NOTE: n = 32–log

2

(page size)

n 20

n = 20 for 4-Kbyte page size.

n–1 n

Loading...

Loading...