MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 3-15

3.3.1.4 Permissions

The application software may restrict access to virtual pages by selectively granting permissions for user

mode read, write, and execute, and supervisor mode read, write, and execute on a per page basis. For

example, program code might be execute-only and data structures may be mapped as

read/write/no-execute.

The UX, SX, UW, SW, UR, and SR access control bits are provided to support selective permissions

(access control):

• SR—Supervisor read permission. Allows loads and load-type cache management instructions to

access the page while in supervisor mode.

• SW—Supervisor write permission. Allows stores and store-type cache management instructions to

access the page while in supervisor mode.

• SX—Supervisor execute permission. Allows instruction fetches to access the page and instructions

to be executed from the page while in supervisor mode.

• UR—User read permission. Allows loads and load-type cache management instructions to access

the page while in user mode.

• UW—User write permission. Allows stores and store-type cache management instructions to

access the page while in user mode.

• UX—User execute permission. Allows instruction fetches to access the page and instructions to be

executed from the page while in user mode.

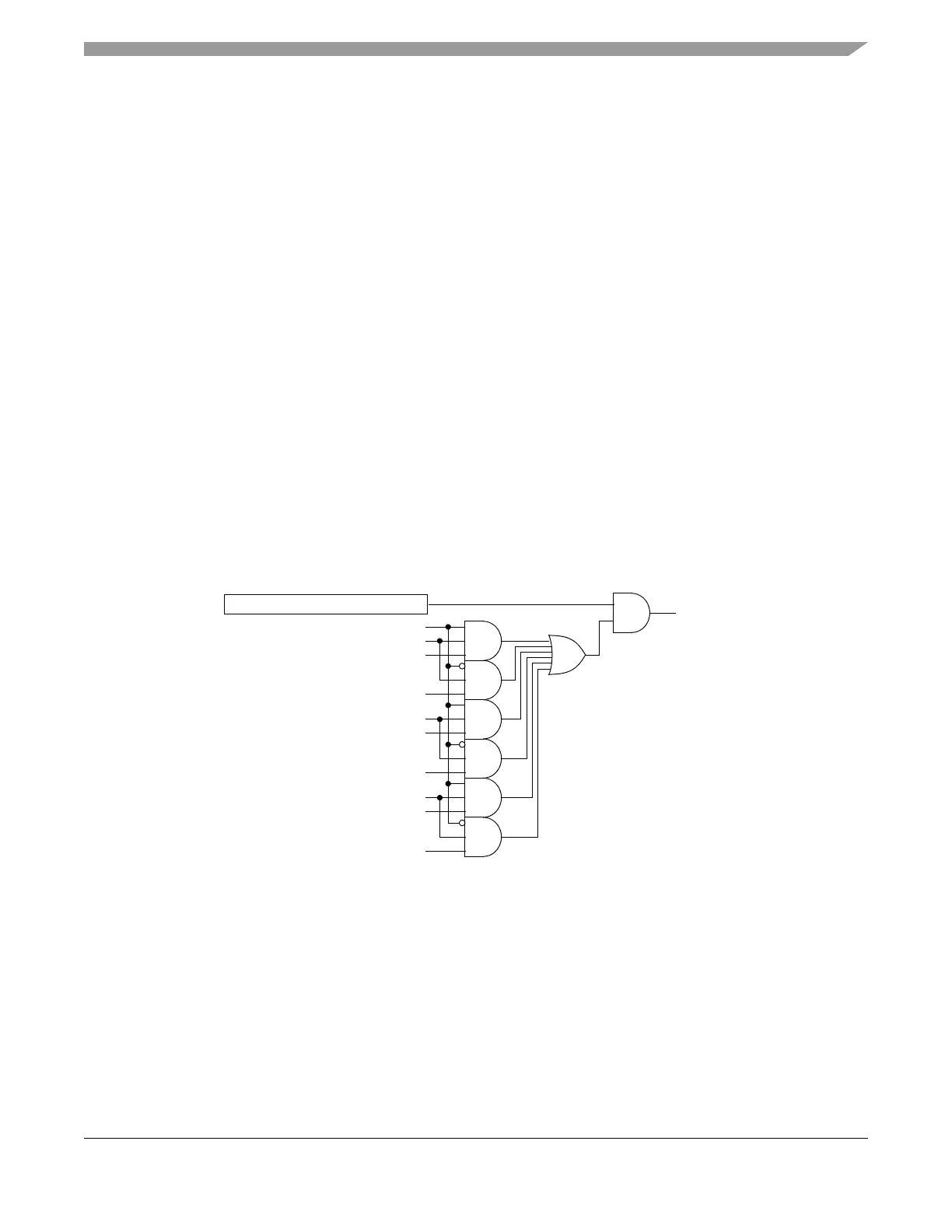

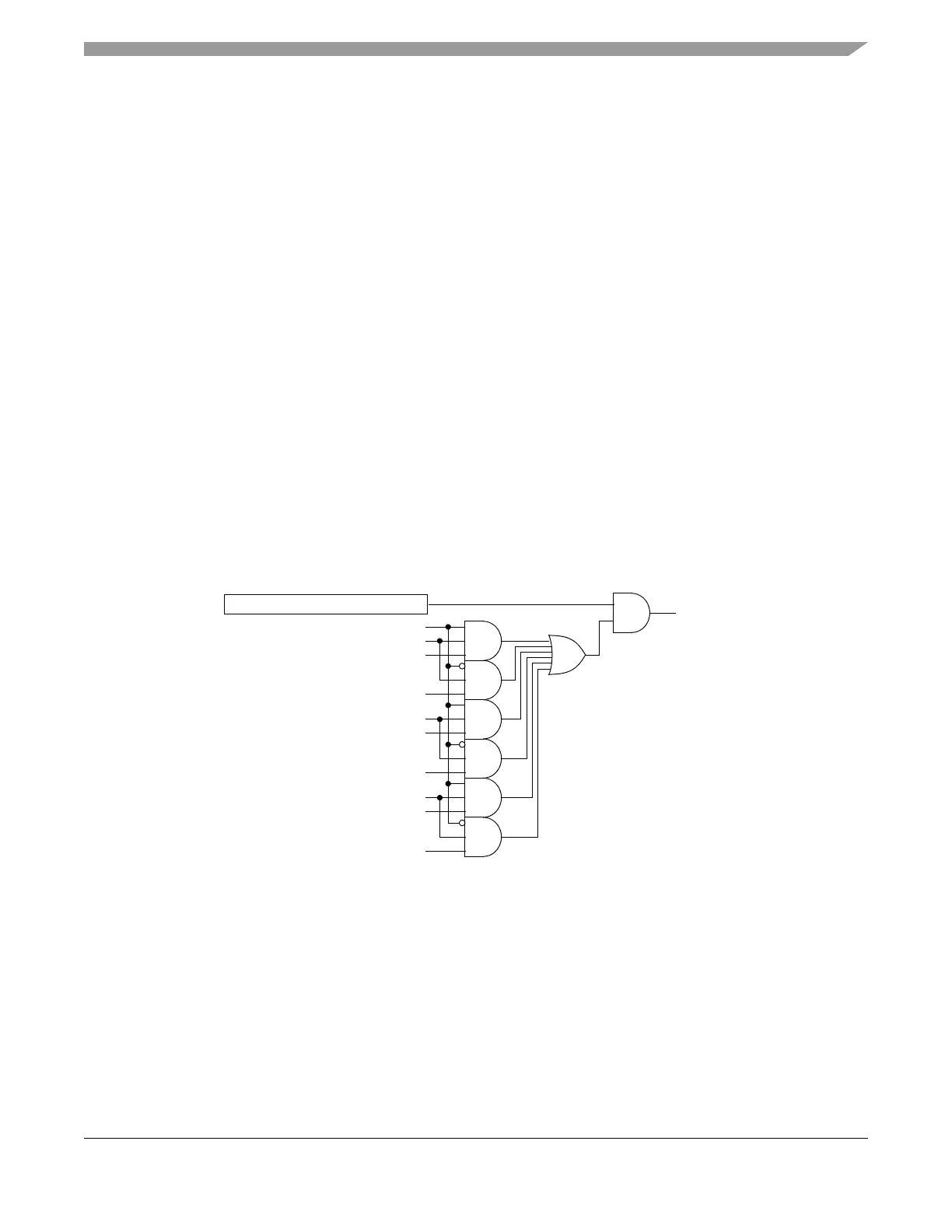

If the translation match was successful, the permission bits are checked as shown in Figure 3-6. If the

access is not allowed by the access permission mechanism, the processor generates an instruction or data

storage interrupt (ISI or DSI).

Figure 3-6. Granting of Access Permission

Access Granted

Instruction Fetch

MSR[PR]

TLB_entry[UX]

TLB_entry[SX]

Load-class Data Access

TLB_entry[UR]

TLB_entry[SR]

Store-class Data Access

TLB_entry[UW]

TLB_entry[SW]

TLB

Loading...

Loading...