System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-7

6.2.1.6.2 DMA Transfers

The IRQ[n] pins map to 16 independent DMA request outputs from the SIU. A DMA request is asserted

when the corresponding IRQ flag bit is set in SIU_EISR, with the corresponding DMA/interrupt request

enable bit set in SIU_DIRER, and the corresponding DMA/interrupt select bit set in SIU_DIRSR. A DMA

done signal is input to the SIU for each DMA request output. The assertion of a DMA done signal clears

the corresponding IRQ flag bit.

6.2.1.6.3 Overruns

An overrun interrupt request exists for each overrun flag in the SIU. An overrun occurs if an edge-triggered

event occurs on an IRQ[n] pin while the corresponding IRQ flag bit is set in SIU_EISR. An overrun

interrupt request is asserted if any of the same bit locations are set in the overrun status register

(SIU_OSR), and the overrun request enable register (SIU_ORER). The SIU outputs one overrun interrupt

request that is the logical OR of all of the overrun interrupt requests.

6.2.1.6.4 Edge Detects

The IRQ[n] pins can be used as edge-detect pins. Edge-detect operation is enabled by selecting rising- or

falling-edge events in the IRQ rising-edge event enable register (SIU_IREER), with DMA/interrupt

requests disabled. The external IRQ status register reflects whether the desired edge has been captured on

each pin.

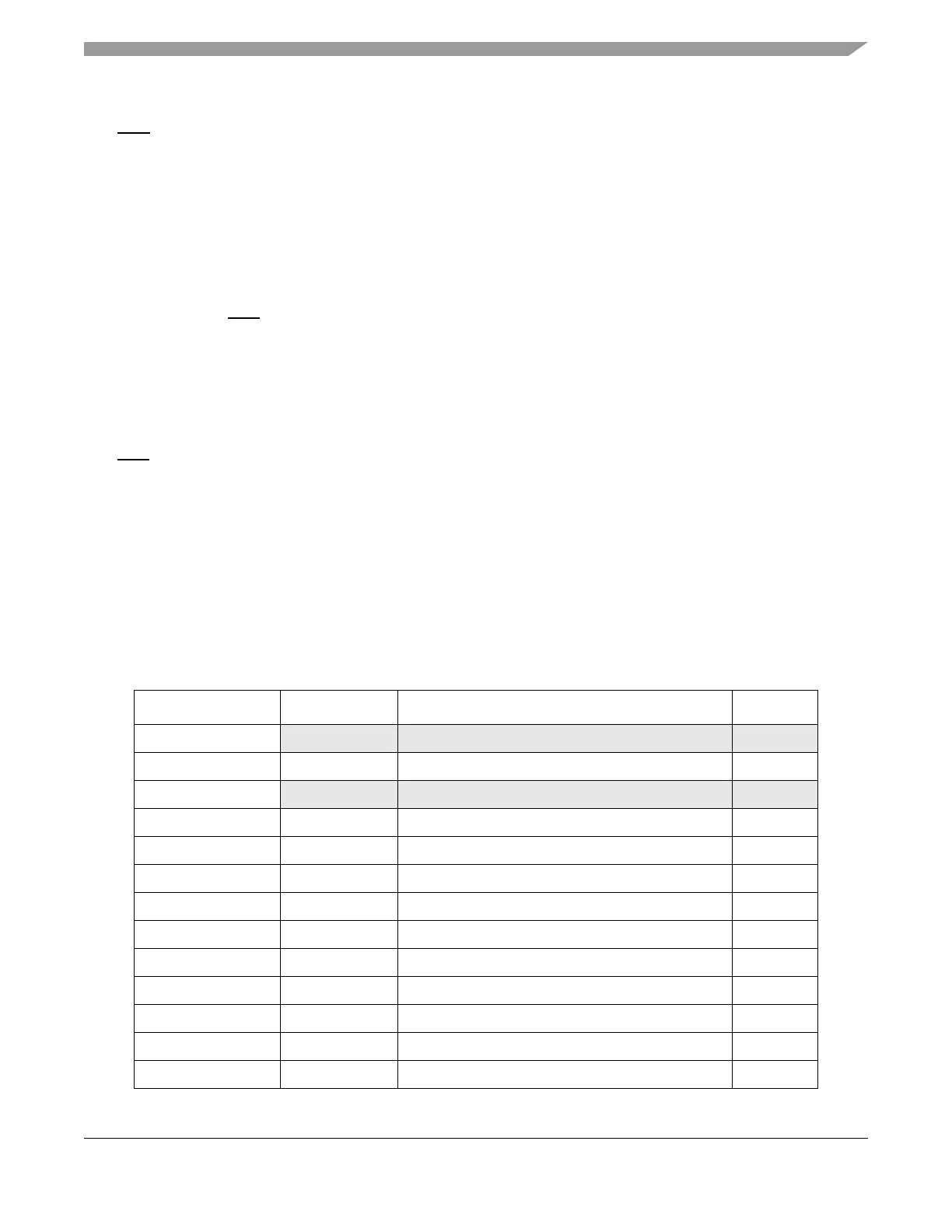

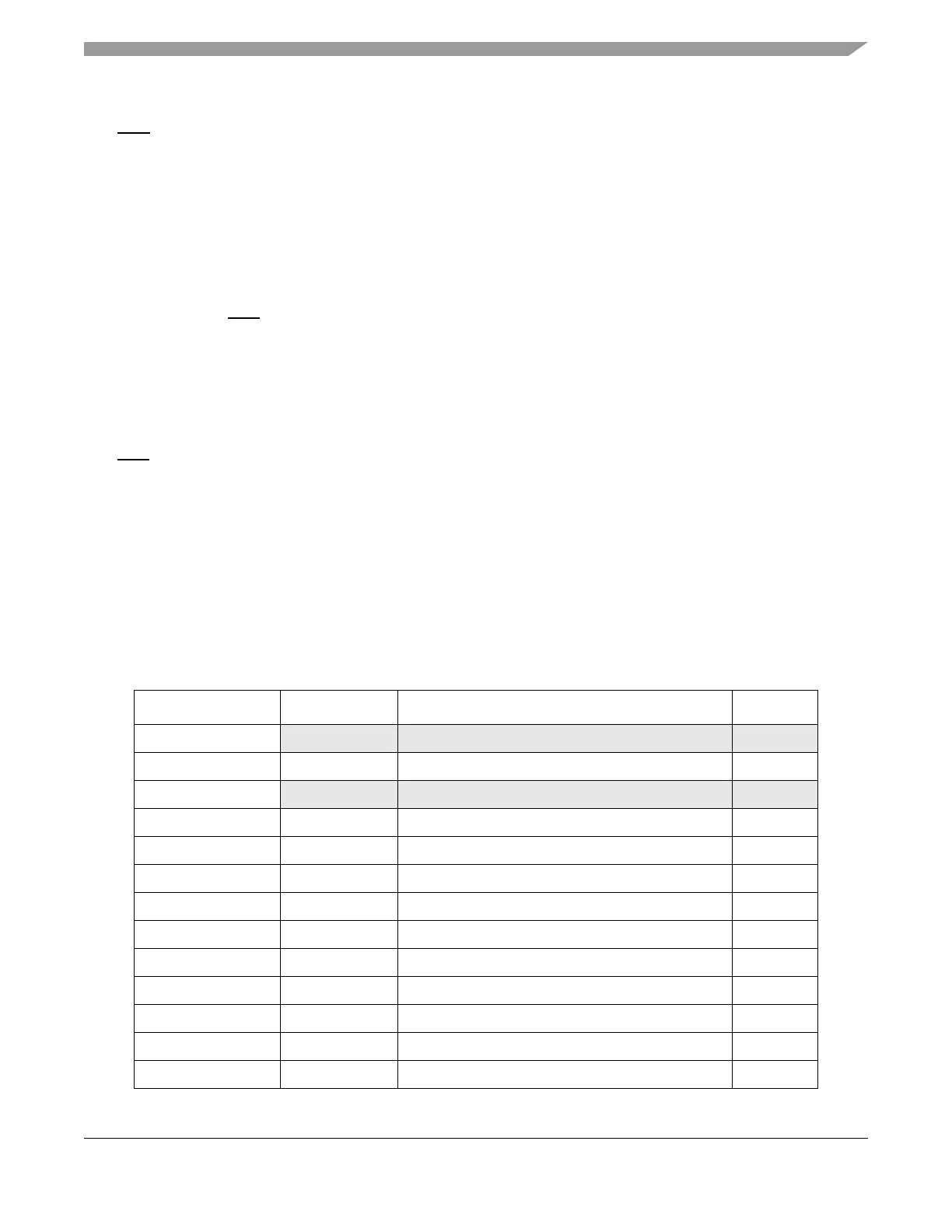

6.3 Memory Map/Register Definition

Table 6-3 is the address map for the SIU registers. All register addresses are given as an offset of the SIU

base address.

Table 6-3. SIU Address Map

Address Register Name Register Description Bits

Base (0xC3F9_0000) — Reserved —

Base + 0x0004 SIU_MIDR MCU ID register 32

Base + 0x0008 — Reserved —

Base + 0x000C SIU_RSR Reset status register 32

Base + 0x0010 SIU_SRCR System reset control register 32

Base + 0x0014 SIU_EISR SIU external interrupt status register 32

Base + 0x0018 SIU_DIRER DMA/interrupt request enable register 32

Base + 0x001C SIU_DIRSR DMA/interrupt request select register 32

Base + 0x0020 SIU_OSR Overrun status register 32

Base + 0x0024 SIU_ORER Overrun request enable register 32

Base + 0x0028 SIU_IREER IRQ rising-edge event enable register 32

Base + 0x002C SIU_IFEER IRQ falling-edge event enable register 32

Base + 0x0030 SIU_IDFR IRQ digital filter register 32

Loading...

Loading...