MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

7-4 Freescale Semiconductor

7.2.1 Register Descriptions

There are two registers for each slave port of the XBAR. The registers can only be accessed in supervisor

mode using 32-bit accesses.

The slave SGPCR also features a bit (RO), which when written with a 1, will prevent all slave registers for

that port from being written to again until a reset occurs. The registers will still be readable, but future write

attempts will have no effect on the registers and will be terminated with an error response.

Please note the difference in numerical values of XBAR Master Port and Master ID as shown in Table 7-1.

7.2.1.1 Master Priority Registers (XBAR_MPRn)

The XBAR_MPR for a slave port sets the priority of each master port when operating in fixed priority

mode. They are ignored in round-robin priority mode unless more than one master has been assigned high

priority by a slave.

NOTE

Masters must be assigned unique priority levels.

The master priority register can only be accessed in supervisor mode with 32-bit accesses. After the RO

(read only) bit has been set in the slave general-purpose control register, the master priority register can

only be read. Attempts to write to it will have no effect on the MPR and will result in an error response.

NOTE

XBAR_MPR should be written with a read/modify/write for code

compatibility.

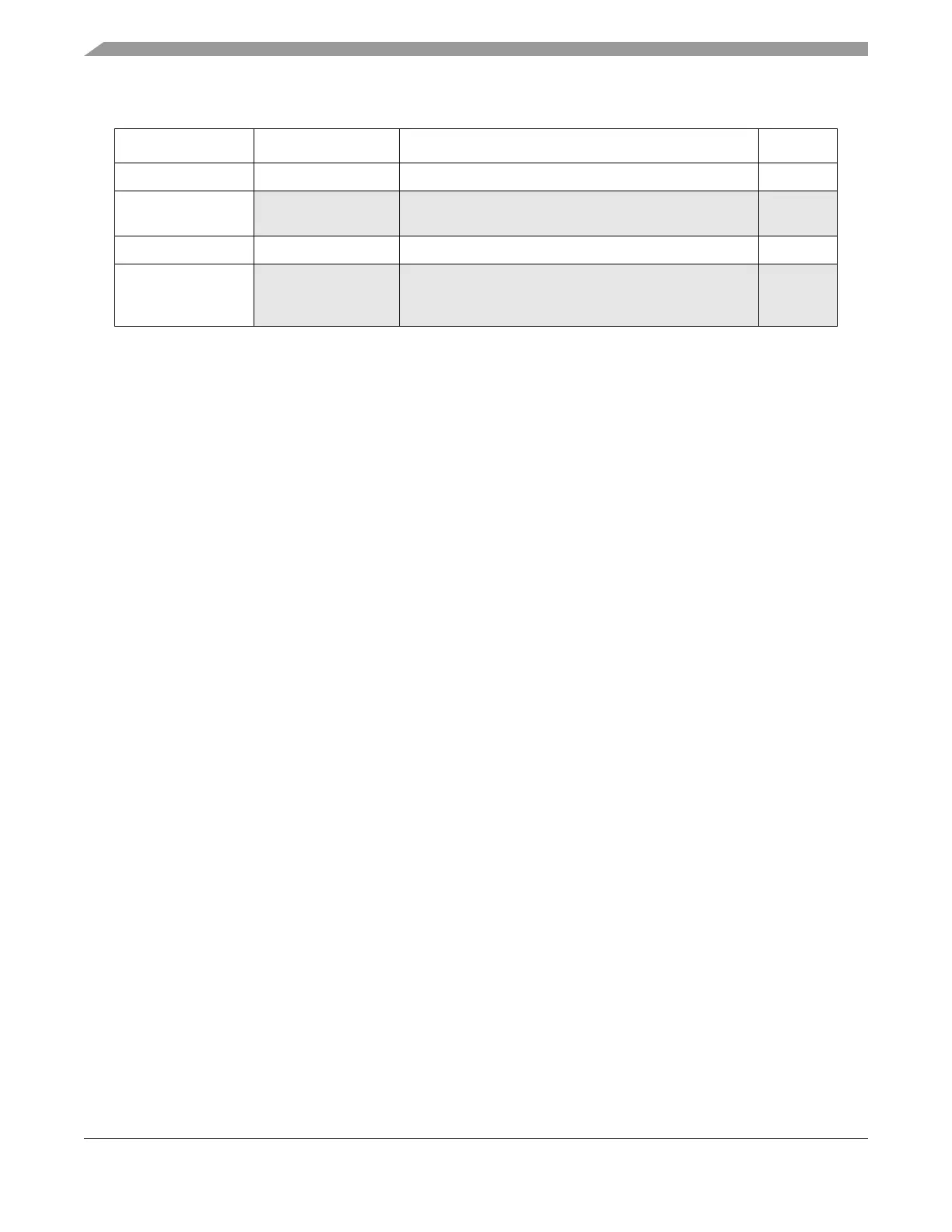

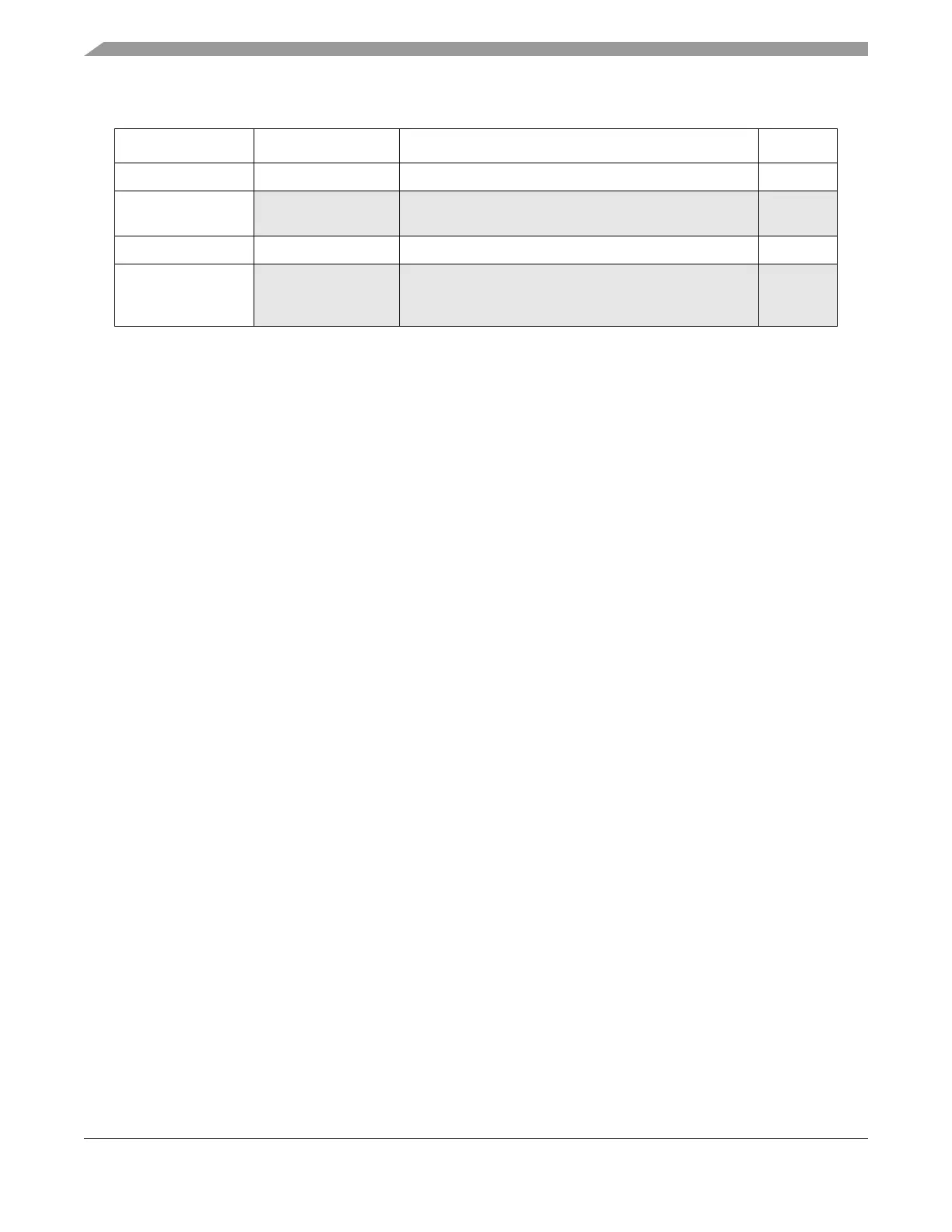

Base + 0x0700 XBAR_MPR7 Master priority register for slave port 7 32

Base + 0x0704–

Base + 0x070F

— Reserved —

Base + 0x0710 XBAR_SGPCR7 General-purpose control register for slave port 7 32

Base + 0x0714–

Base +

0x0003_FFFF

— Reserved —

Table 7-2. XBAR Register Memory Map (Continued)

Address Register Name Register Description Size (bits)

Loading...

Loading...