MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

22-30 Freescale Semiconductor

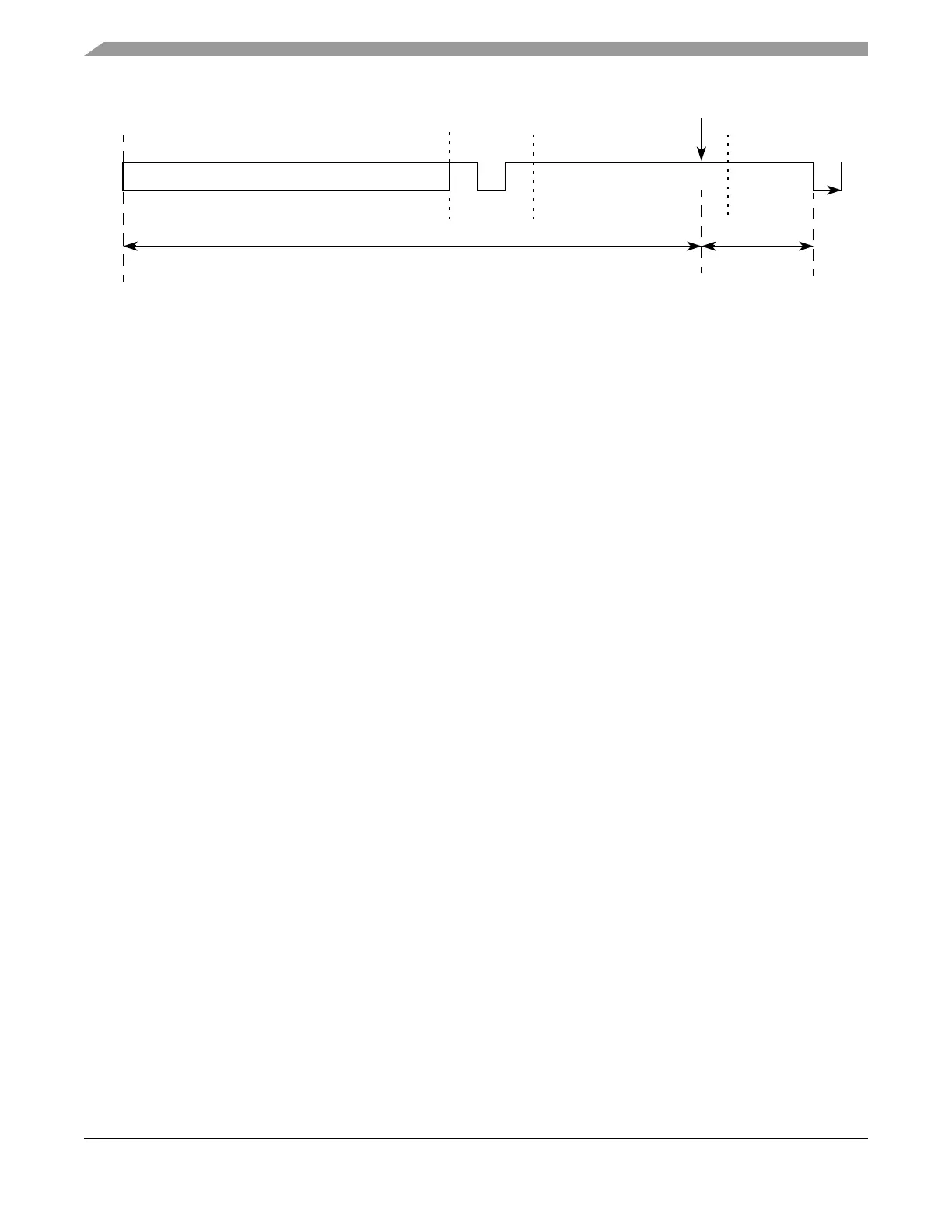

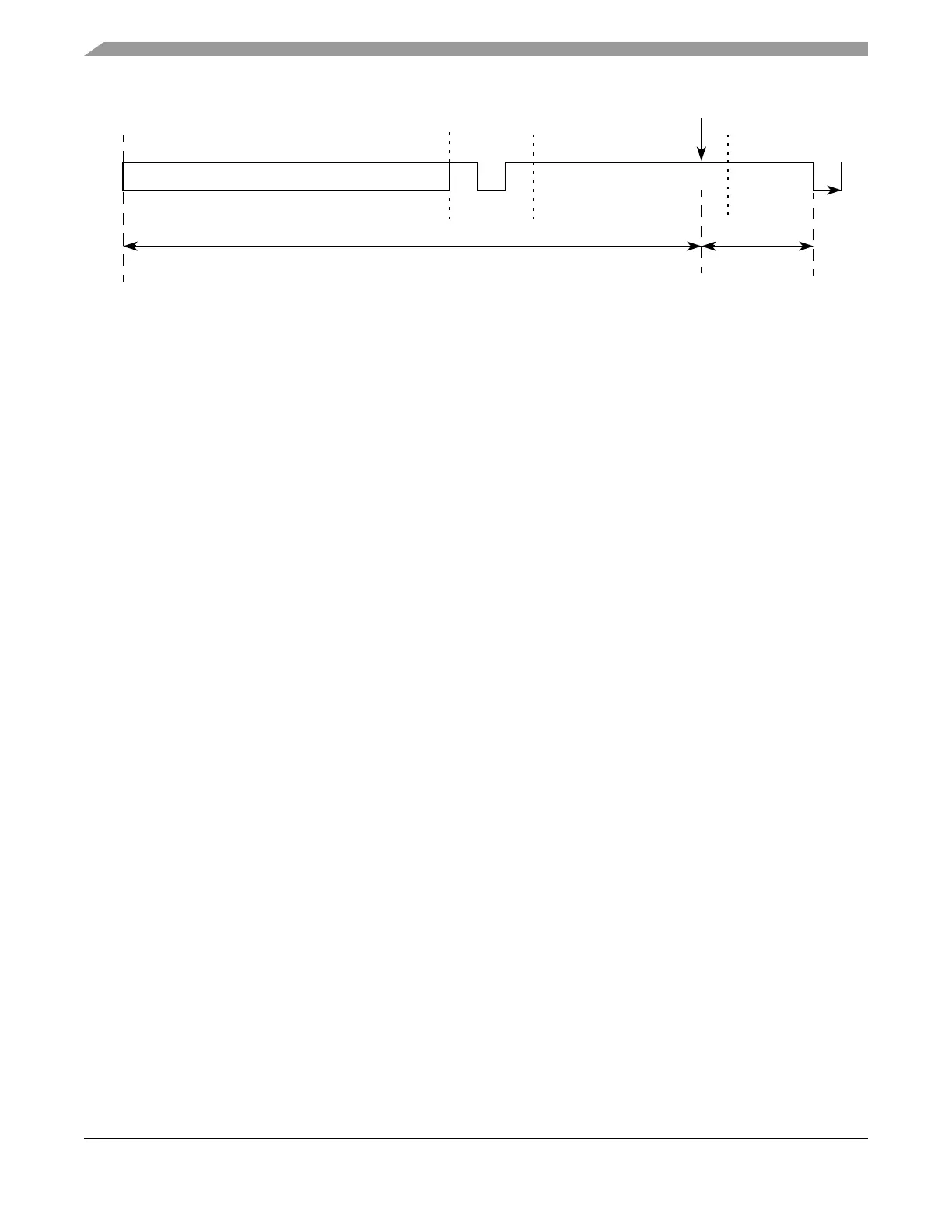

Figure 22-14. Arbitration, Match and Move Time Windows

22.4.6 Modes of Operation Details

22.4.6.1 Freeze Mode

This mode is entered by asserting the HALT bit in the CANx_MCR or when the MCU is put into debug

mode. In both cases it is also necessary that the FRZ bit is asserted in the CANx_MCR. When freeze mode

is requested during transmission or reception, FlexCAN2 does the following:

• Waits to be in either intermission, passive error, bus off or idle state

• Waits for all internal activities like move in or move out to finish

• Ignores the RX input pin and drives the TX pin as recessive

• Stops the prescaler, thus halting all CAN protocol activities

• Grants write access to the CANx_ECR, which is read-only in other modes

• Sets the NOTRDY and FRZACK bits in CANx_MCR

After requesting freeze mode, the user must wait for the FRZACK bit to be asserted in CANx_MCR before

executing any other action, otherwise FlexCAN2 can operate in an unpredictable way. In freeze mode, all

memory mapped registers are accessible.

Exiting freeze mode is done in one of the following ways:

• CPU negates the FRZ bit in the CANx_MCR.

• The MCU exits debug mode and/or the HALT bit is negated.

After it is out of freeze mode, FlexCAN2 tries to re-synchronize to the CAN bus by waiting for 11

consecutive recessive bits.

22.4.6.2 Module Disabled Mode

This low power mode is entered when the CANx_MCR[MDIS] bit is asserted. If the module is disabled

during freeze mode, it shuts down the clocks to the CPI and MBM sub-modules, sets the

CANx_MCR[MDISACK] bit and negates the CANx_MCR[FRZACK] bit. If the module is disabled

during transmission or reception, FlexCAN2 does the following:

• Waits to be in either idle or bus off state, or else waits for the third bit of intermission and then

checks it to be recessive

• Waits for all internal activities like move in or move out to finish

• Ignores its RX input pin and drives its TX pin as recessive

• Shuts down the clocks to the CPI and MBM sub-modules

• Sets the NOTRDY and MDISACK bits in CANx_MCR

CRC (15) EOF (7)

Interim

Start Move

Matching/Arbitration Window (24 bits)

Move

(bit 6)

Window

Loading...

Loading...