MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

14-36 Freescale Semiconductor

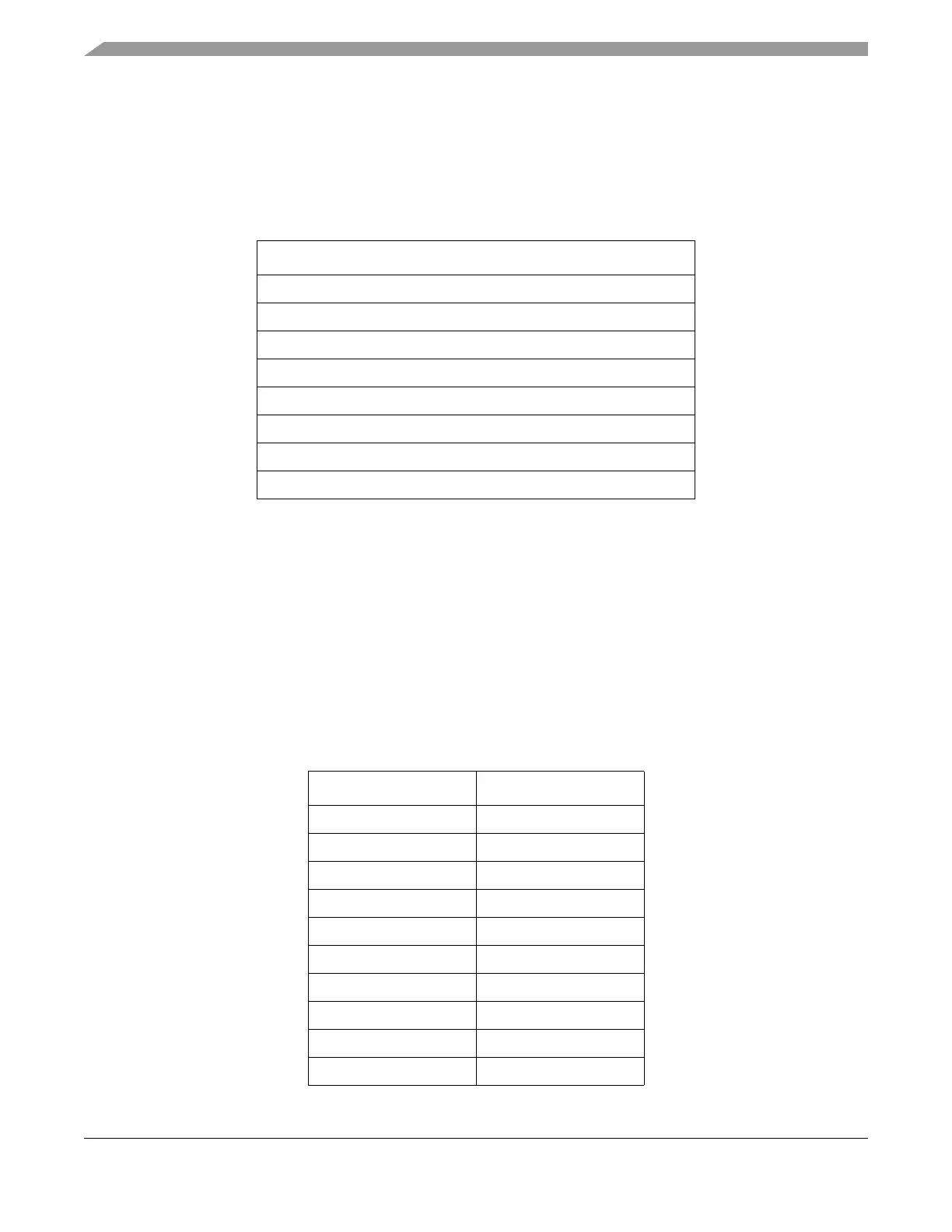

14.4.3 Microcontroller Initialization

In the FEC, the descriptor control RISC initializes some registers after ECR[ETHER_EN] is asserted.

After the microcontroller initialization sequence is complete, the hardware is ready for operation.

Table 14-32 shows microcontroller initialization operations.

14.4.4 User Initialization (After Asserting ECR[ETHER_EN])

After asserting ECR[ETHER_EN], the user can set up the buffer/frame descriptors and write to the TDAR

and RDAR. Refer to Section 14.5, “Buffer Descriptors” for more details.

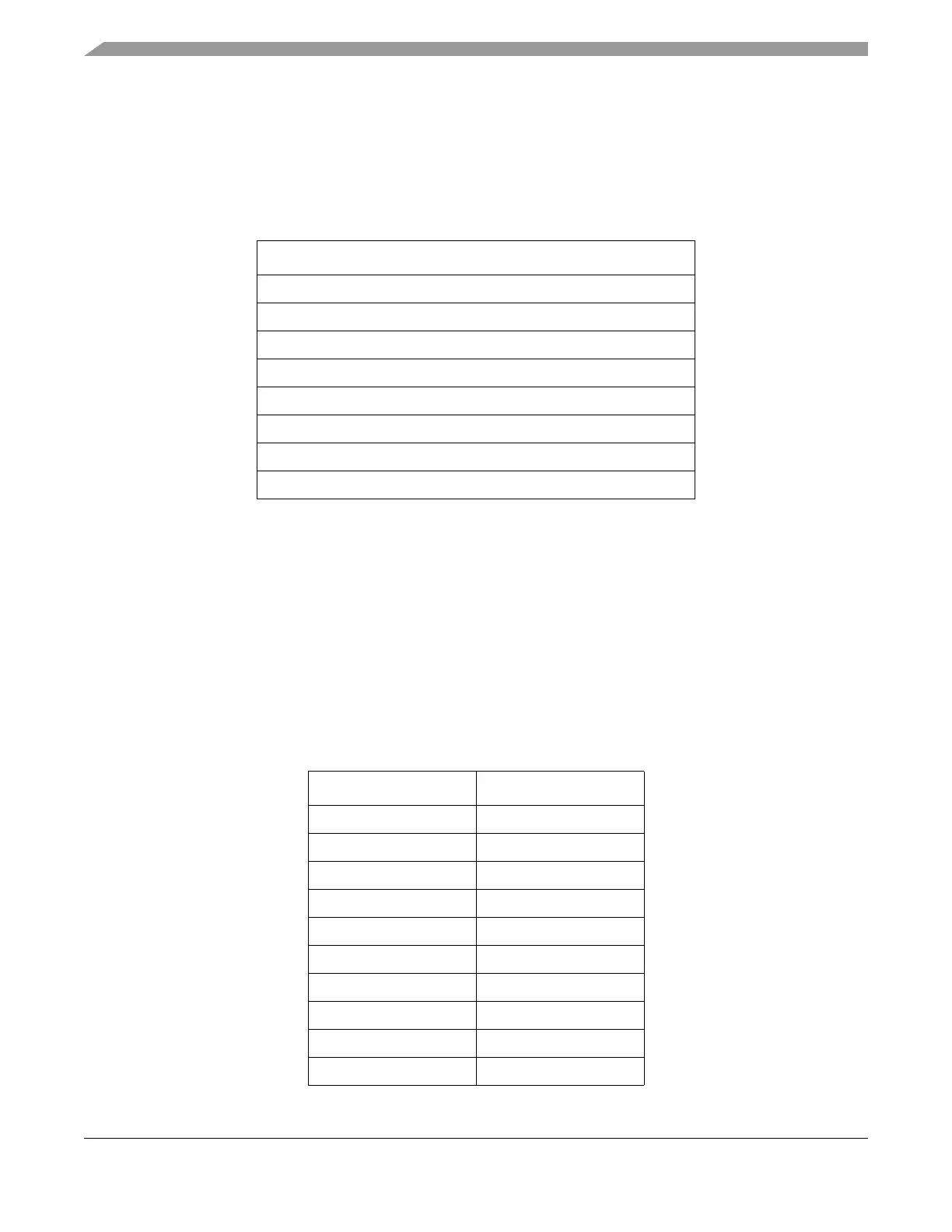

14.4.5 Network Interface Options

The FEC supports both an MII interface for 10/100 Mbps Ethernet and a 7-wire serial interface for 10

Mbps Ethernet. The interface mode is selected by the RCR[MII_MODE] bit. In MII mode

(RCR[MII_MODE] = 1), there are 18 signals defined by the IEEE 802.3 standard and supported by the

EMAC. These signals are shown in Table 14-33 below.

Table 14-32. Microcontroller Initialization

Description

Initialize BackOff Random Number Seed

Activate Receiver

Activate Transmitter

Clear Transmit FIFO

Clear Receive FIFO

Initialize Transmit Ring Pointer

Initialize Receive Ring Pointer

Initialize FIFO Count Registers

Table 14-33. MII Mode

Signal Description EMAC Signal

Transmit Clock FEC_CLK

Transmit Enable FEC_TX_EN

Transmit Data FEC_TXD[3:0]

Transmit Error FEC_TX_ER

Collision FEC_COL

Carrier Sense FEC_CRS

Receive Clock FEC_RX_CLK

Receive Data Valid FEC_RX_DV

Receive Data FEC_RX_D[3:0]

Receive Error FEC_RX_ER

Loading...

Loading...