MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-82 Freescale Semiconductor

Reading/writing of a Nexus register then requires two (2) passes through the data-scan (DR) path of the

JTAG state machine (see Chapter 24, “IEEE 1149.1 Test Access Port Controller (JTAGC)”).

1. The first pass through the DR selects the Nexus register to be accessed by providing an index (see

Table 25-45), and the direction (read/write). This is achieved by loading an 8-bit value into the

JTAG data register (DR). This register has the following format:

2. The second pass through the DR then shifts the data in or out of the JTAG port, lsb first.

a) During a read access, data is latched from the selected Nexus register when the JTAG state

machine passes through the capture-DR state.

b) During a write access, data is latched into the selected Nexus register when the JTAG state

machine passes through the update-DR state.

25.14.3 Functional Description

25.14.4 Enabling NXDM Operation

The NXDM module is enabled by loading a single instruction (ACCESS_AUX_TAP_DMAN3, as shown

in Table 25-4) into the JTAG instruction register (IR), and then loading the corresponding OnCE OCMD

register with the NEXUS_ACCESS instruction (refer to Table 25-5). After it is enabled, the module will

be ready to accept control input via the JTAG pins.

The Nexus module is disabled when the JTAG state machine reaches the test-logic-reset state. This state

can be reached by the assertion of the JCOMP pin or by cycling through the state machine using the TMS

pin. The Nexus module will also be disabled if a power-on reset (POR) event occurs.

If the NXDM module is disabled, no trace output will be provided, and the module will disable (drive

inactive) auxiliary port output pins (MDO[11:0], MSEO[1:0], MCKO). Nexus registers will not be

available for reads or writes.

25.14.5 TCODEs Supported by NXDM

The NXDM pins allow for flexible transfer operations via public messages. A TCODE defines the transfer

format, the number and/or size of the packets to be transferred, and the purpose of each packet. The

IEEE-ISTO 5001-2003 standard defines a set of public messages. The NXDM block currently supports

the public TCODEs seen in Table 25-55.

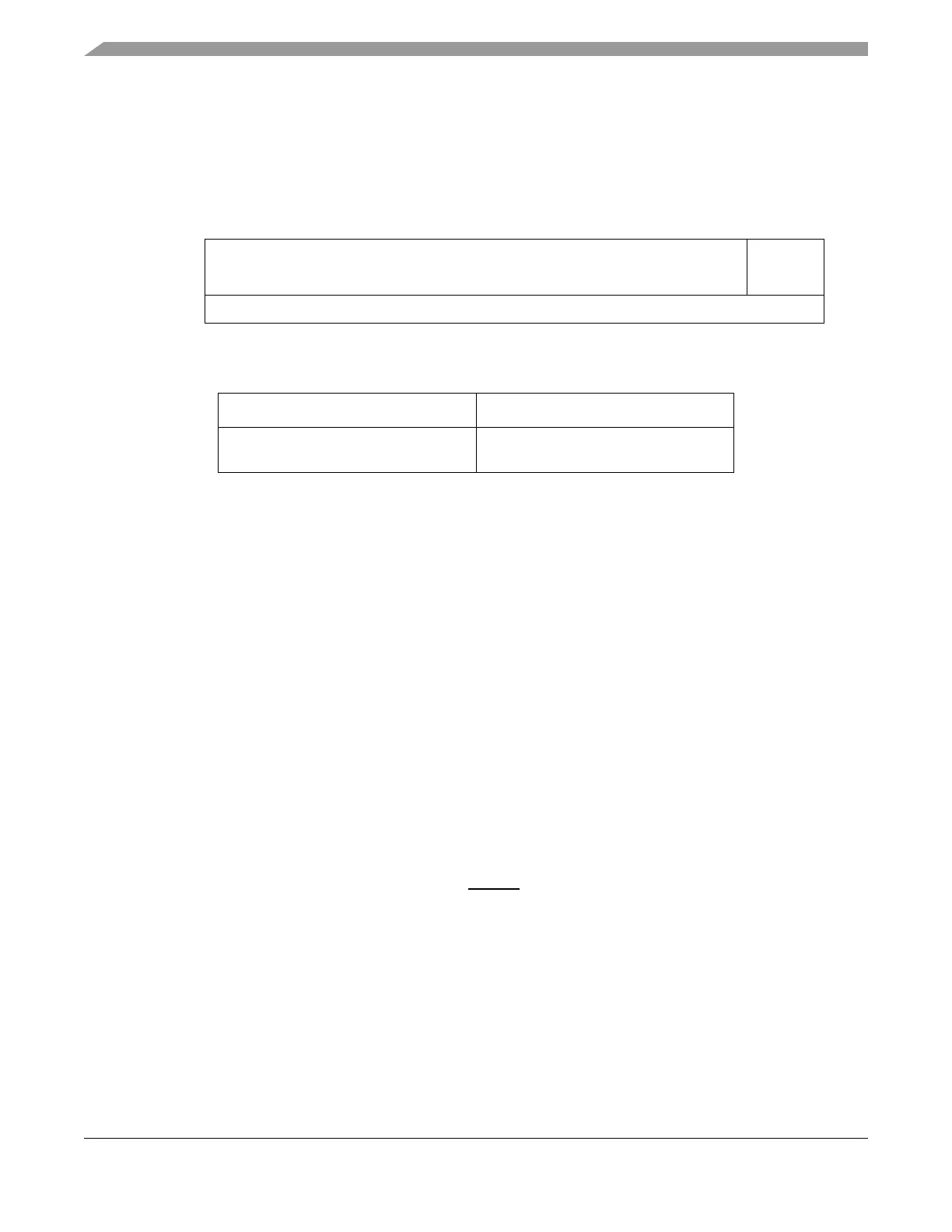

76543210

R Nexus Register Index R/W

W

Reset

Figure 25-63. JTAG DR for NEXUS Register Access

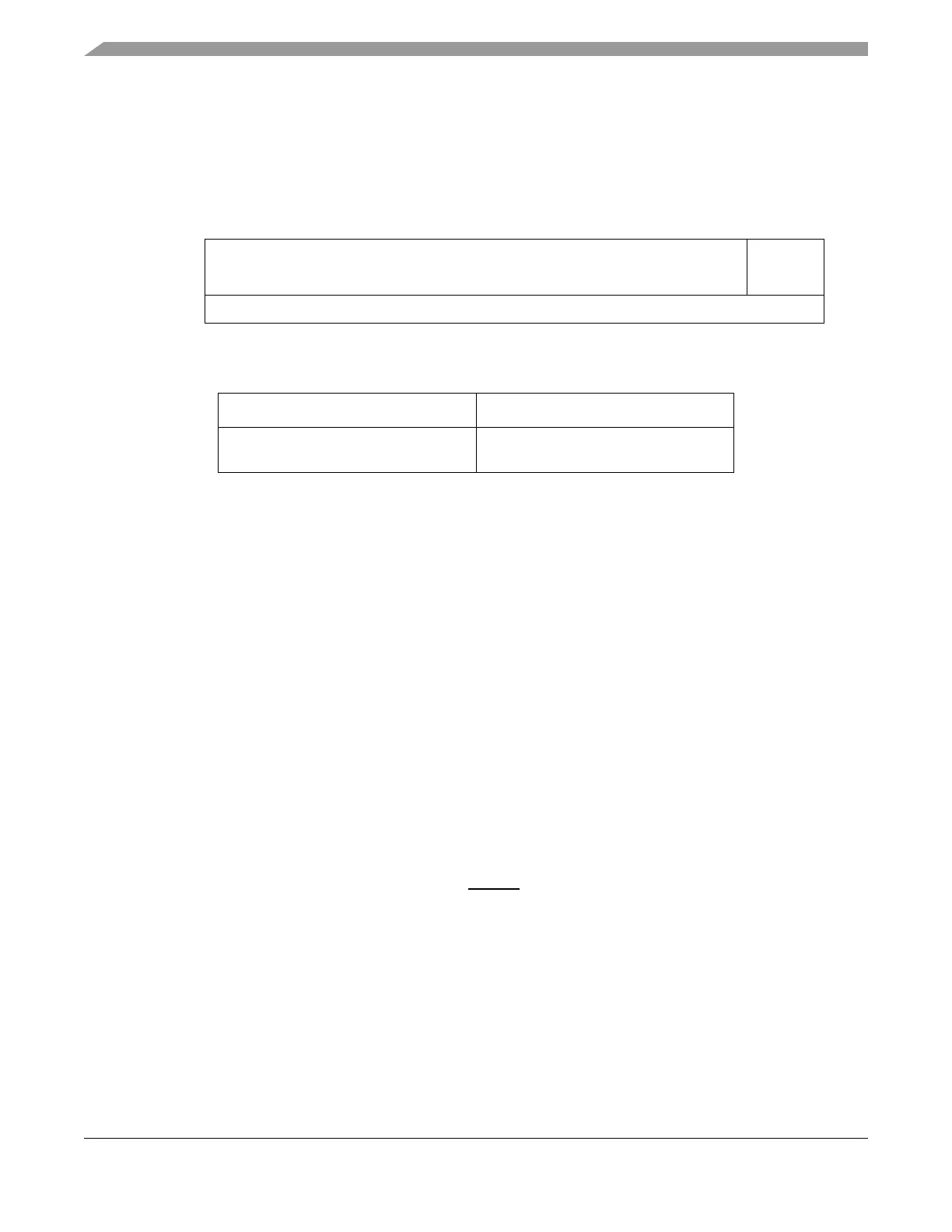

Table 25-54. DR Read/Write Encoding

Nexus Register Index Selected from Values in Table 3-1

Read/Write (R/W) 0 Read

1Write

Loading...

Loading...