MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 25-81

25.14.2.11.1 NXDM JTAG ID Register

This JTAG ID register that is included in the NXDM module provides key development attributes to the

development tool concerning the NXDM block. The register is accessed through the standard JTAG IR/DR

paths. See Chapter 23, “Voltage Regulator Controller (VRC) and POR Module.”

25.14.2.11.2 Enabling the NXDM TAP Controller

Assertion of a power-on-reset signal or assertion of the JCOMP pin resets all TAP controllers on the

MPC5553/MPC5554 device. Upon exit from the test-logic-reset state, the IR value is loaded with the

JTAG ID. When the NXDM TAP is accessed, this information will help the development tool obtain

information about the Nexus module it is accessing, such as version, sequence, feature set, etc.

25.14.2.11.3 NXDM Register Access via JTAG

Access to Nexus register resources is enabled by loading a single instruction (NEXUS_ACCESS) into the

JTAG Instruction Register (IR). This IR is part of the IEEE 1149.1 TAP controller within the NXDM

module. See Section 24.4.4, “JTAGC Instructions.”

After the JTAG NEXUS_ACCESS instruction has been loaded, the JTAG port allows tool/target

communications with all Nexus registers according to the map in Table 25-45.

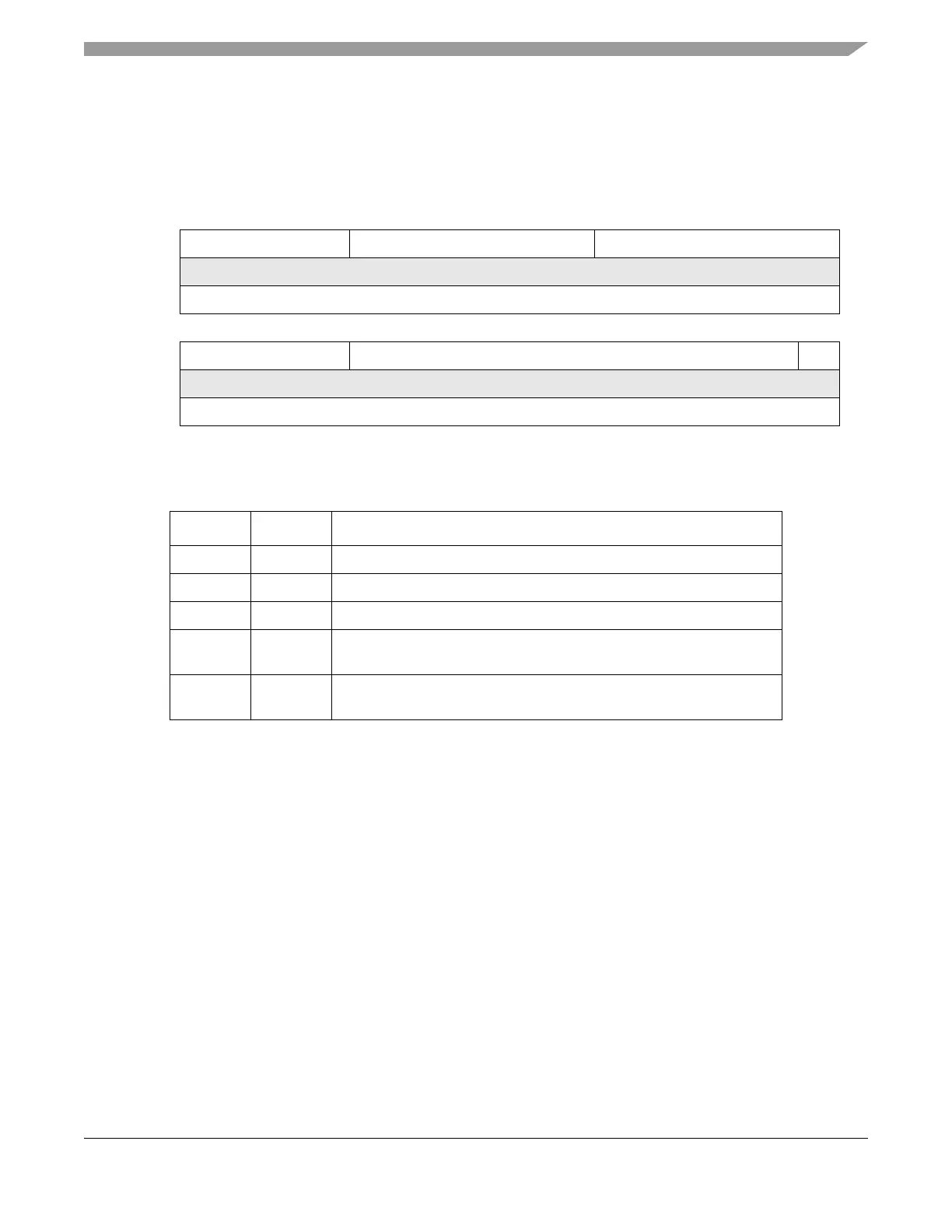

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

R PRN DC PIN

W

Reset0 000011111000110

1514131211109876543210

RPIN MIC 1

W

Reset0 000000000011101

Figure 25-62. NXDM JTAG ID Register

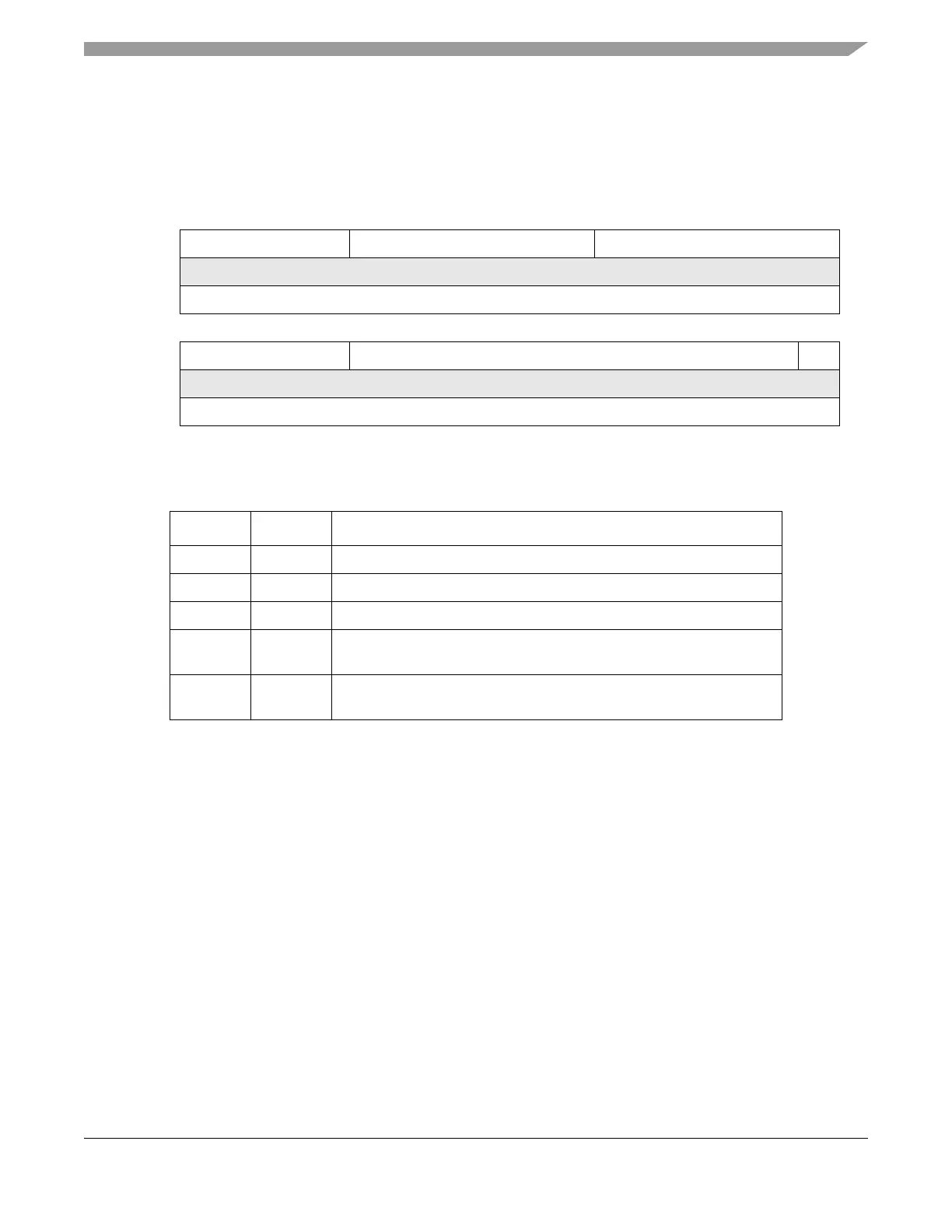

Table 25-53. NXDM JTAG ID Field Descriptions

Bit Name Description

31–28 PRN

1

1

The revision number is initially 0 and could change in the future.

Embedded part revision number (0x0)

27–22 DC Freescale design center ID number (0x1F)

21–12 PIN NXDM module part identification number, defines the features set. (0x60)

11–1 MIC Manufacturer identity code

0x00E Freescale

0 — Fixed per JTAG 1149.1

1 Always set

Loading...

Loading...