MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

9-4 Freescale Semiconductor

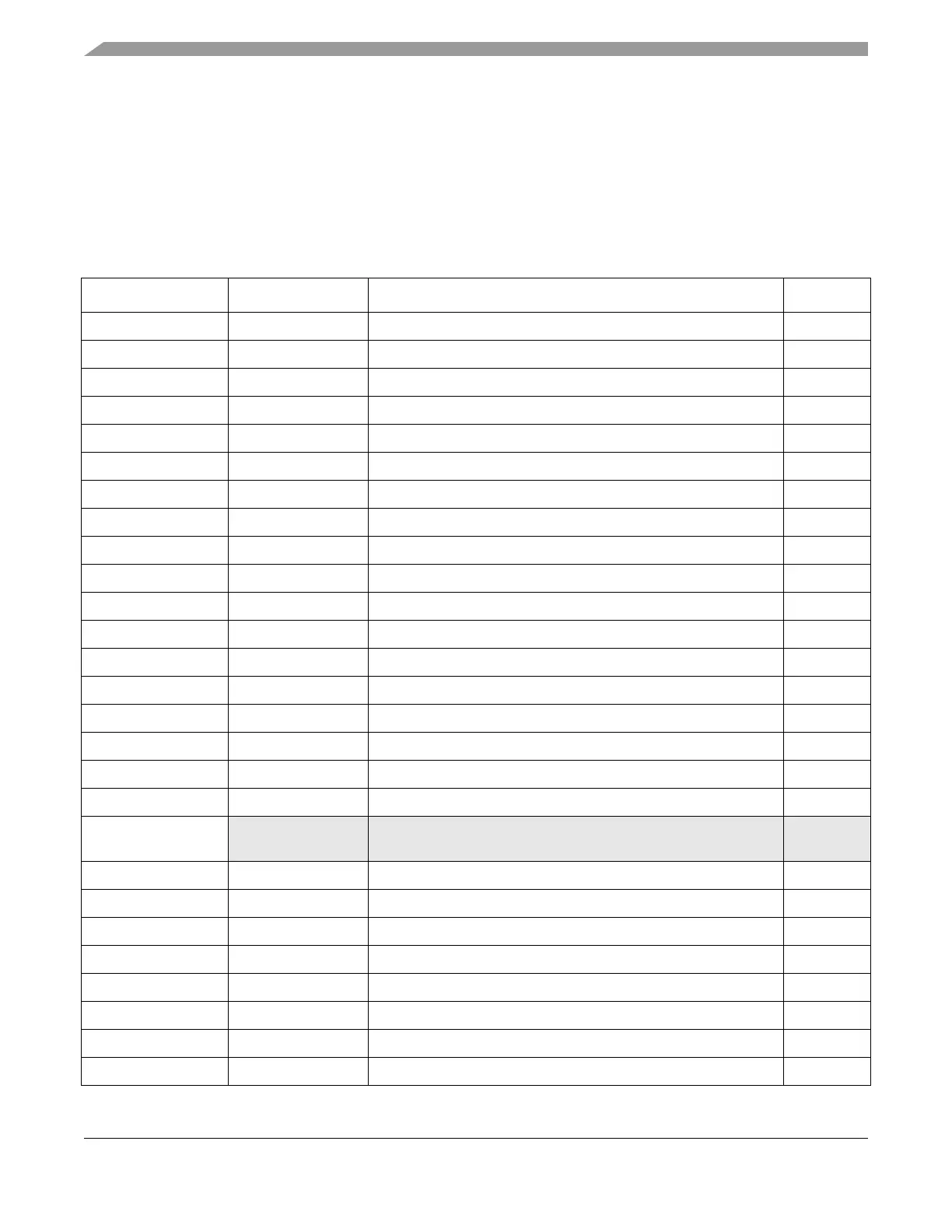

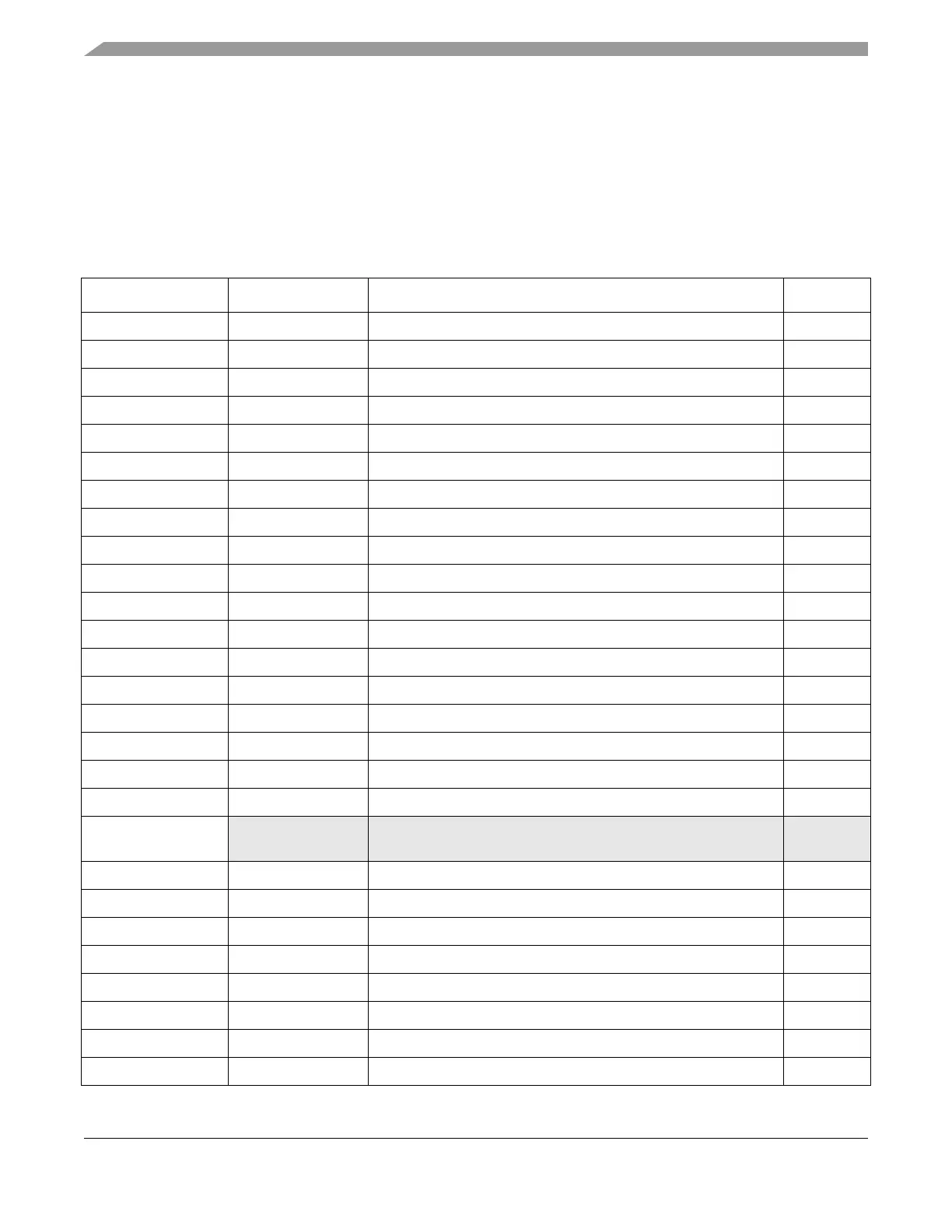

9.3 Memory Map/Register Definition

The eDMA’s programming model is partitioned into two regions: the first region defines a number of

registers providing control functions, while the second region corresponds to the local transfer control

descriptor memory.

Some registers are implemented as two 32-bit registers, and include an “H” and “L” suffix, signaling the

“high” and “low” portions of the control function. Table 9-1 is a 32-bit view of the eDMA’s memory map.

Table 9-1. eDMA 32-bit Memory Map (Sheet 1 of 5)

Address Register Name Register Description Size (bits)

Base (0xFFF4_4000) EDMA_CR eDMA control register 32

Base + 0x0004 EDMA_ESR eDMA error status register 32

Base + 0x0008 EDMA_ERQRH eDMA enable request high register (MPC5554 only) 32

Base + 0x000C EDMA_ERQRL eDMA enable request low register 32

Base + 0x0010 EDMA_EEIRH eDMA enable error interrupt high register (MPC5554 only) 32

Base + 0x0014 EDMA_EEIRL eDMA enable error interrupt low register 32

Base + 0x0018 EDMA_SERQR eDMA set enable request register 8

Base + 0x0019 EDMA_CERQR eDMA clear enable request register 8

Base + 0x001A EDMA_SEEIR eDMA set enable error interrupt register 8

Base + 0x001B EDMA_CEEIR eDMA clear enable error interrupt register 8

Base + 0x001C EDMA_CIRQR eDMA clear interrupt request register 8

Base + 0x001D EDMA_CER eDMA clear error register 8

Base + 0x001E EDMA_SSBR eDMA set start bit register 8

Base + 0x001F EDMA_CDSBR eDMA clear done status bit register 8

Base + 0x0020 EDMA_IRQRH eDMA interrupt request high register (MPC5554 only) 32

Base + 0x0024 EDMA_IRQRL eDMA interrupt request low register 32

Base + 0x0028 EDMA_ERH eDMA error high register (MPC5554 only) 32

Base + 0x002C EDMA_ERL eDMA error low register 32

Base + 0x0030–

Base + 0x00FF

— Reserved —

Base + 0x0100 EDMA_CPR0 eDMA channel 0 priority register 8

Base + 0x0101 EDMA_CPR1 eDMA channel 1 priority register 8

Base + 0x0102 EDMA_CPR2 eDMA channel 2 priority register 8

Base + 0x0103 EDMA_CPR3 eDMA channel 3 priority register 8

Base + 0x0104 EDMA_CPR4 eDMA channel 4 priority register 8

Base + 0x0105 EDMA_CPR5 eDMA channel 5 priority register 8

Base + 0x0106 EDMA_CPR6 eDMA channel 6 priority register 8

Base + 0x0107 EDMA_CPR7 eDMA channel 7 priority register 8

Loading...

Loading...