MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-68 Freescale Semiconductor

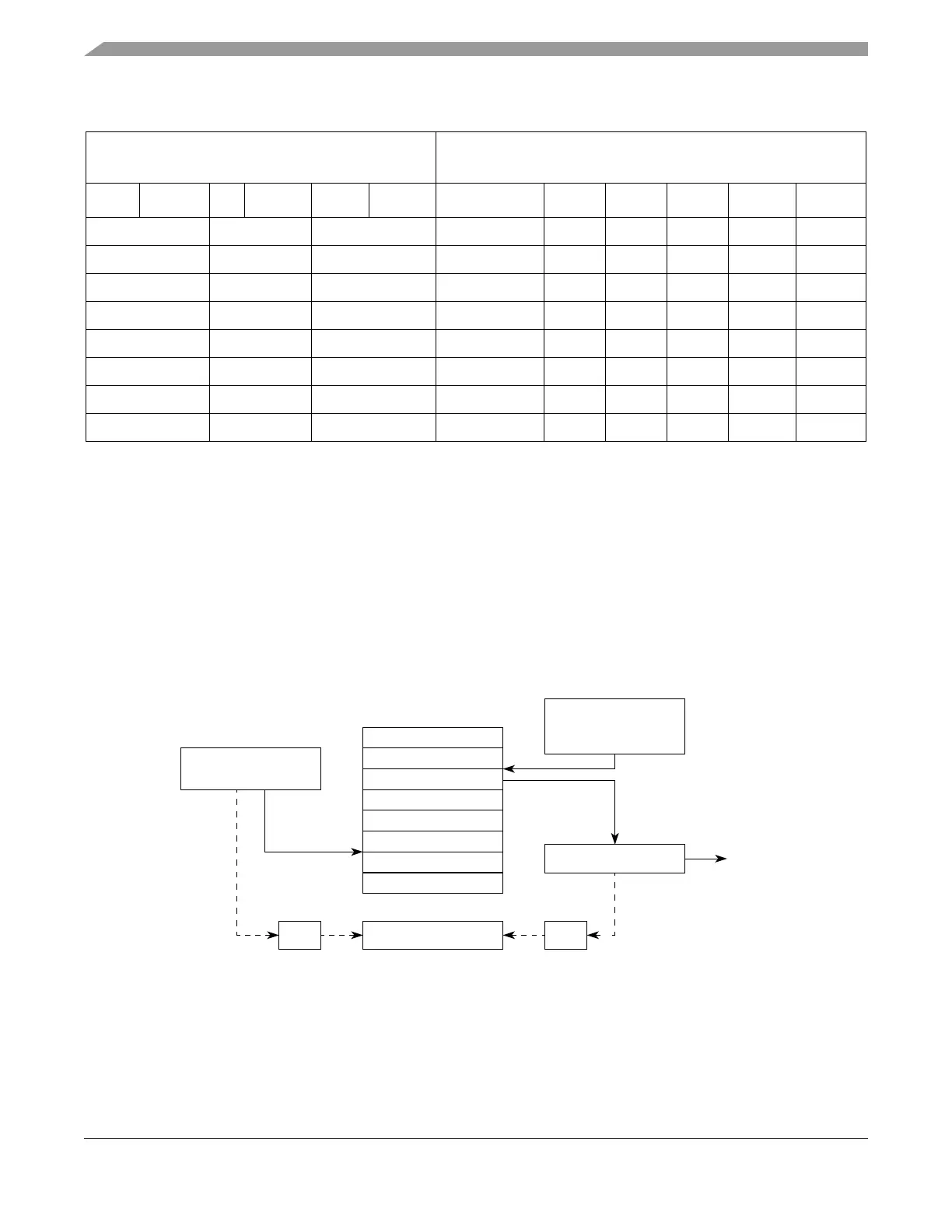

20.5.5 Calculation of FIFO Pointer Addresses

The user has complete visibility of the TX and RX FIFO contents through the FIFO registers, and valid

entries can be identified through a memory mapped pointer and a memory mapped counter for each FIFO.

The pointer to the first-in entry in each FIFO is memory mapped. For the TX FIFO the first-in pointer is

the transmit next pointer (TXNXTPTR). For the RX FIFO the first-in pointer is the pop next pointer

(POPNXTPTR). Figure 20-45 illustrates the concept of first-in and last-in FIFO entries along with the

FIFO counter. The TX FIFO is chosen for the illustration, but the concepts carry over to the RX FIFO. See

Section 20.4.3.4, “Transmit First In First Out (TX FIFO) Buffering Mechanism,” and Section 20.4.3.5,

“Receive First In First Out (RX FIFO) Buffering Mechanism,” for details on the FIFO operation.

Figure 20-45. TX FIFO Pointers and Counter

Table 20-33. MPC5xx QSPI Compatibility with the DSPI

MPC5xx Family Control Bits

DSPI Corresponding Control Bits

Corresponding DSPIx_CTAR Register Configuration

BITSE CTAS[0] DT CTAS[1] DSCK CTAS[2] DSPIx_CTARx FMSZ PDT DT PCSSCK CSSCK

0 0 0 0 0111 10 0011 00 0000

0 0 1 1 0111 10 0011 User User

0 1 0 2 0111 User

1

1

Selected by user

User 00 0000

0 1 1 3 0111 User User User User

1 0 0 4 User 10 0011 00 0000

1 0 1 5 User 10 0011 User User

1 1 0 6 User User User 00 0000

1 1 1 7 User User User User User

Entry C

Entry A (First In)

– 1

Entry B

Entry D (Last In)

TX FIFO Base

Push TX FIFO

TX FIFO Counter

Shift Register SOUT

Register

Transmit Next

Data Pointer

–

–

–

–

+ 1

(TXNXTPTR)

Loading...

Loading...