MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-2 Freescale Semiconductor

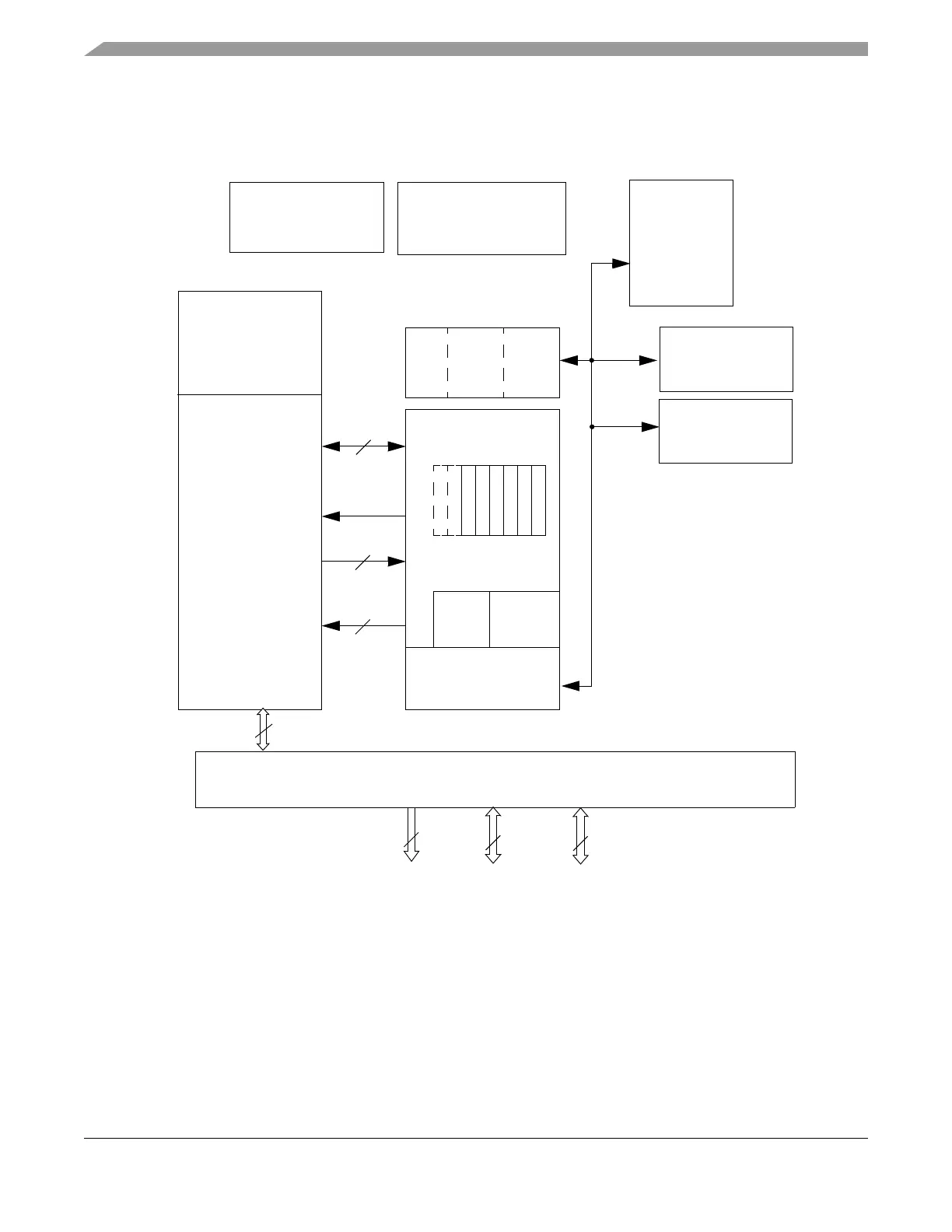

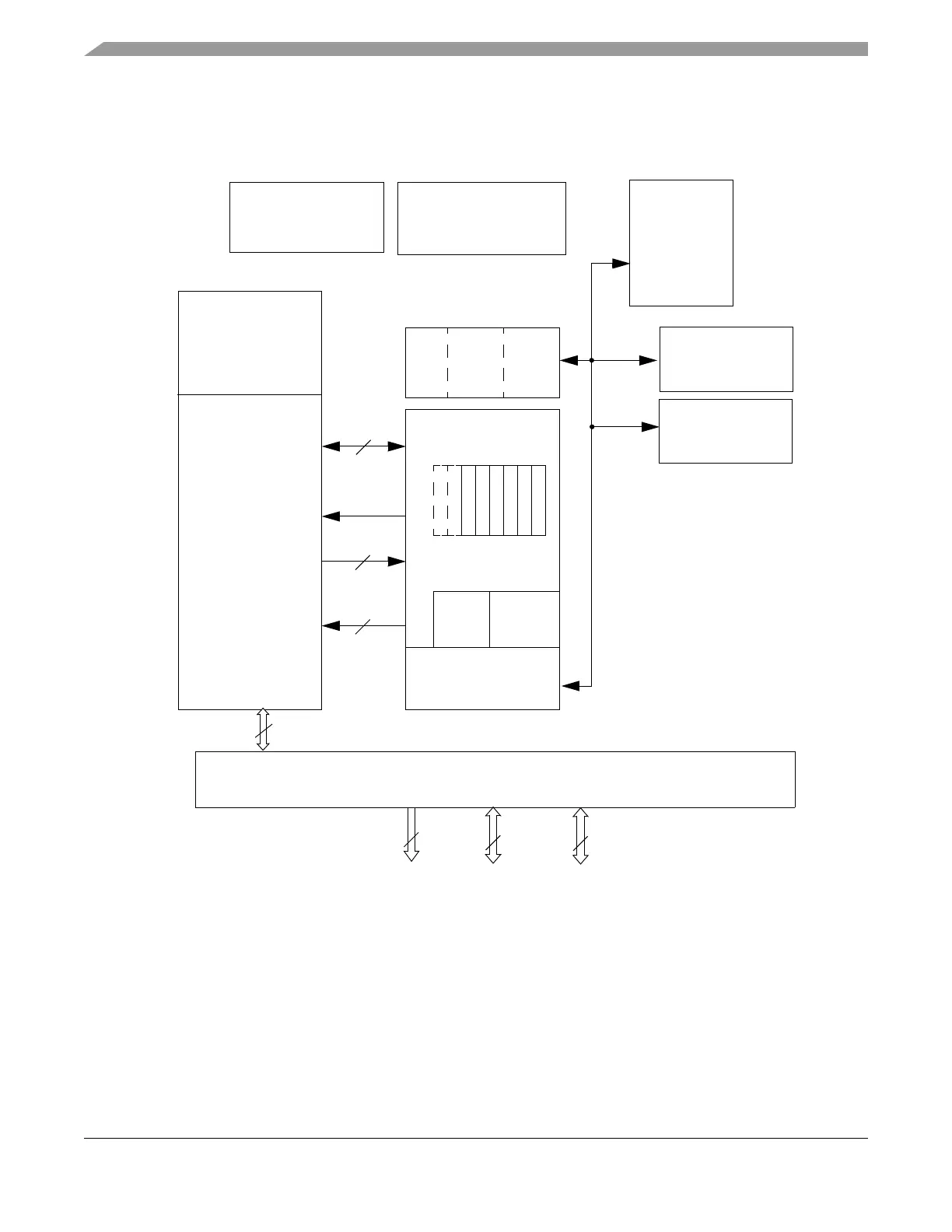

3.1.1 Block Diagram

Figure 3-1 shows a block diagram of the e200z6 core complex.

Figure 3-1. e200z6 Block Diagram

3.1.2 Overview

The e200z6 core integrates an integer execution unit, branch control unit, instruction fetch and load/store

units, and a multi-ported register file capable of sustaining three read and two write operations per clock.

Most integer instructions execute in a single clock cycle. Branch target prefetching is performed by the

branch target address cache to allow single-cycle branches in many cases.

CPU

Control Logic

Load/

32-Kbyte (MPC5554) /

Cache

Data

Memory

Management

Unit

Address

Store

Unit

Control

Instruction Unit

Address

Branch

Unit

PC

Unit

Instruction Buffer

GPRs

CR

SPR

Multiply

Unit

Bus Interface Unit

Control

32

64

Data Out

64

64

Signal

Processing

OnCE/NEXUS 1/

Control Logic

Engine

(SPE APU)

Unified

Integer

Execution

Unit

Data In

64

CTR

XER

LR

(64-bit)

NEXUS 3

8-Kbyte (MPC5553)

Loading...

Loading...