Freescale Semiconductor -1

Appendix C

Revision History

This appendix lists major changes between versions of the MPC5553/5554 Microcontroller Reference

Manual. For convenience, the corrections are grouped by revision.

C.1 Changes Between Rev. 4 and Rev. 5

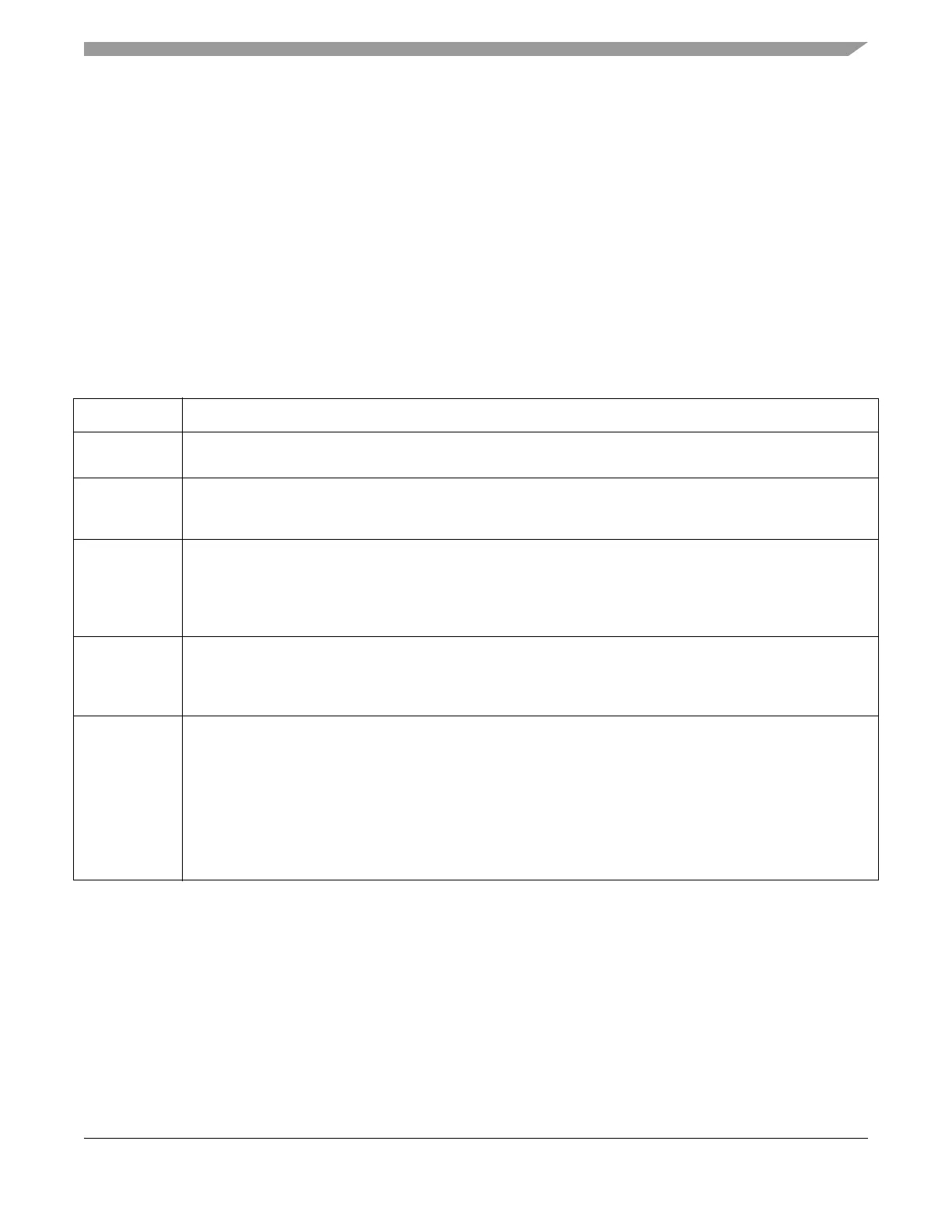

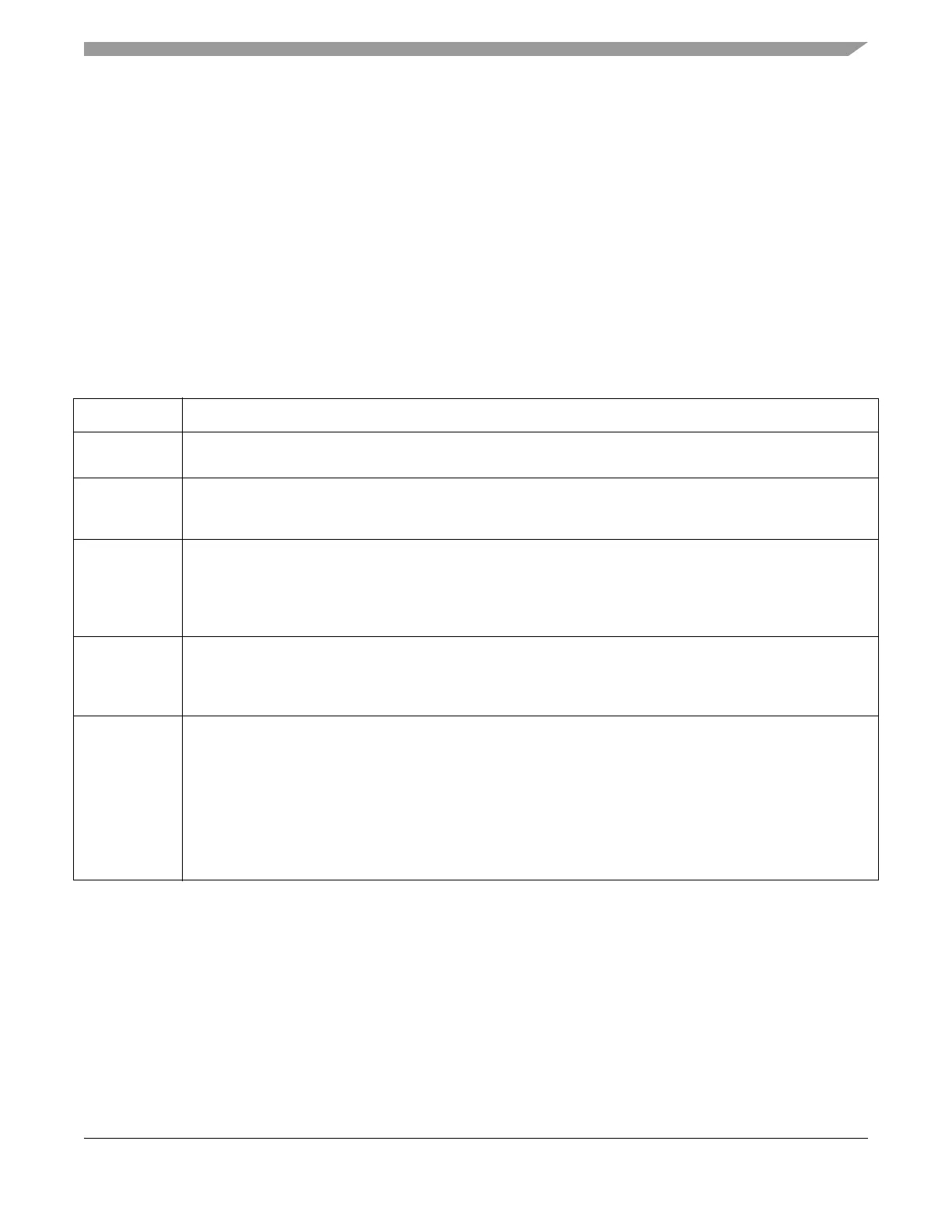

Table A-1. Rev. 4 to Rev. 5 Changes

Chapter Description

Chapter 1

Overview

In Tabl e 1- 2, in the address range 0x0100_0000–0x1FFF_FFFF(emulation mapping of FLASH Array), updated

the Used Size (bytes) cell as “2 Mbytes (MPC5554) and 1.5 Mbytes (MPC5553)”.

Chapter 2

Signal

Description

In Tabl e 2- 1 and Ta bl e 2 -2 , corrected the ball numbers in the Power / Ground Signals section, Pin Labels /

Package Type column.

Chapter 5

Peripheral

Bridge

(PBRIDGE_A,

PBRIDGE_B)

Corrected the presentation of bits 20–31 in the Master Privilege Control Registers (PBRIDGE_x_MPCR) figure,

Figure 5-2, to indicate that the bits are readable and writable, even though they’re not defined.

Chapter 6

System

Integration Unit

(SIU)

In Section 6.3.1.12.61, “Pad Configuration Register 105 (SIU_PCR105), rephrased footnote 1 to the following:

“When configured as PCSB[0], the OBE bit has no effect. When configured as PCSD[2], set the OBE bit to 1 for

master operation, and clear it to 0 for slave operation. When configured as GPO, set the OBE bit to 1.”

Chapter 9

Enhanced

Direct Memory

Access (eDMA)

•In Ta bl e 9 -2 2, removed mention of Transmit Complete flag in rows for eSCIA_COMBTX and eSCIB_COMBTX.

•In Section 9.4.1, “eDMA Microarchitecture, in the "TCD local memory" bullet, under Memory controller section,

deleted the sentence "The hooks to a BIST controller for the local TCD memory are included in this module".

•In Section 9.3.1.13, “eDMA Interrupt Request Registers (EDMA_IRQRH, EDMA_IRQRL), in the second

paragraph, removed the last line "without the need to perform a read-modify-write sequence to the

EDMA_IRQRH and EDMA_IRQRL".

•In Tabl e 9-1 8, BWC bit[0:1] description, added the following sentence to the BWC bit: “To minimize start-up

latency, bandwidth control stalls are suppressed for the first two system bus cycles and after the last write of

each minor loop.”

Loading...

Loading...