MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

13-4 Freescale Semiconductor

13.2 External Signal Description

Table 13-1 shows a list of signals required for flash.

13.2.1 Voltage for Flash Only (V

FLASH)

V

FLASH

is a supply required for reads of the flash core. This voltage is specified as 3.3V with a tolerance

of 0.3 V.

13.2.2 Program and Erase Voltage for Flash Only (V

PP

)

V

PP

is a supply required for program and erase of the flash core. This voltage is specified as 5 V with a

tolerance of -0.5 V/+0.25 V during program and erase operations. V

PP

is required at all times, even during

normal reads of flash memory. During read operations, V

PP

can be as high as 5.3 V and as low as 3.0 V.

13.3 Memory Map/Register Description

The FBIU occupies a 512-MB portion of the address space. The actual flash array is multiply-mapped

within this space.

The MPC5553/MPC5554 internal flash has a feature that allows the internal flash timing to be modified

to emulate an external memory, hence the name, external emulation mode. The upper five address lines

are used to provide additional timing control that allows the FBIU response timing on the system bus

(which must be controlled in order to provide for timing emulation of alternate memory types). Refer to

Figure 13-3.

Figure 13-3. FBIU Address Scheme

This feature allows calibration parameters to be tested using an external memory; and then in production,

the internal flash access timing is modified to match timing of the external memory. The access time of the

internal flash is lengthened based on the address range being accessed. To access an area with a slower

access time, the address is modified per Table 13-2.

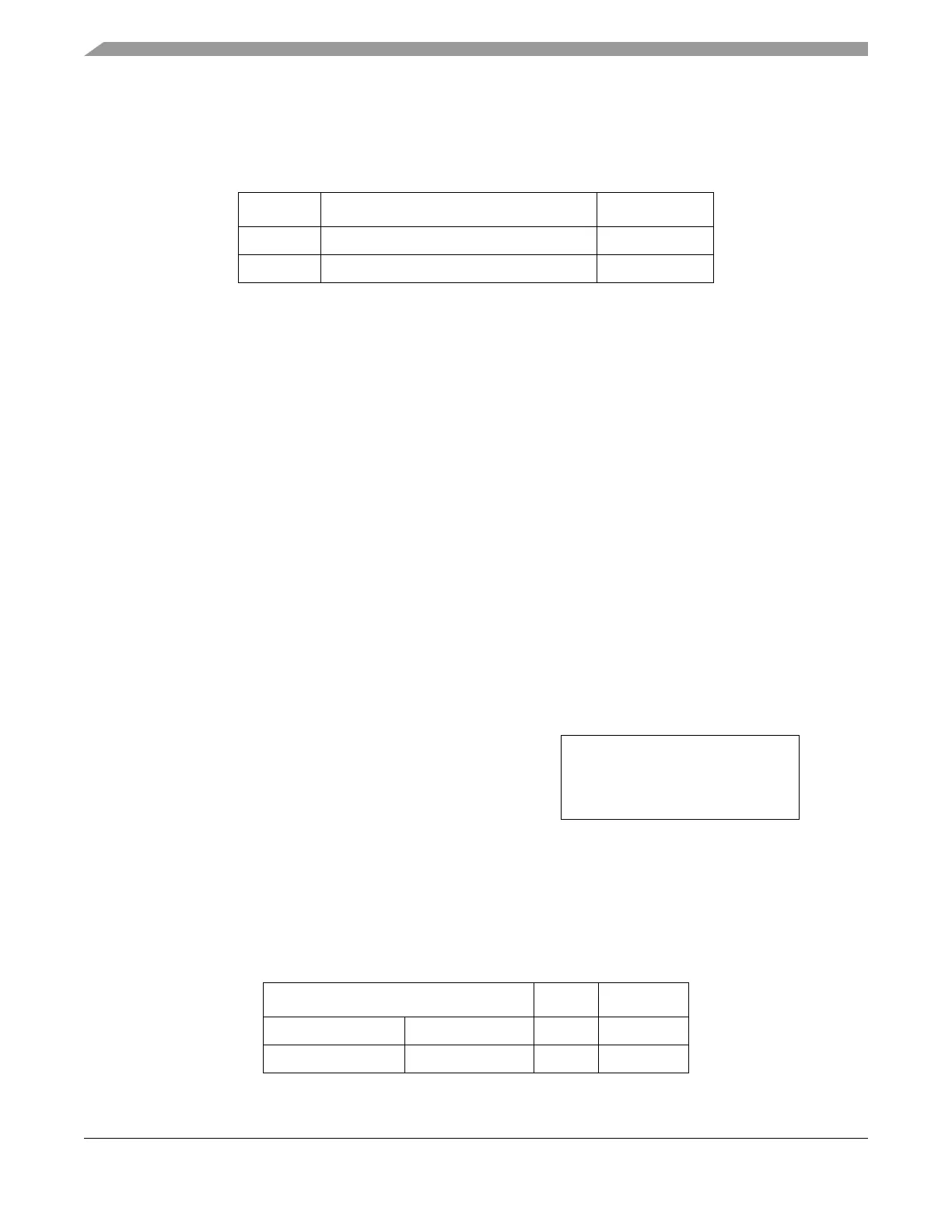

Table 13-1. Signal Properties

Name Function Reset State

V

FLASH

Flash read power supply NA

V

PP

Flash program/erase power supply NA

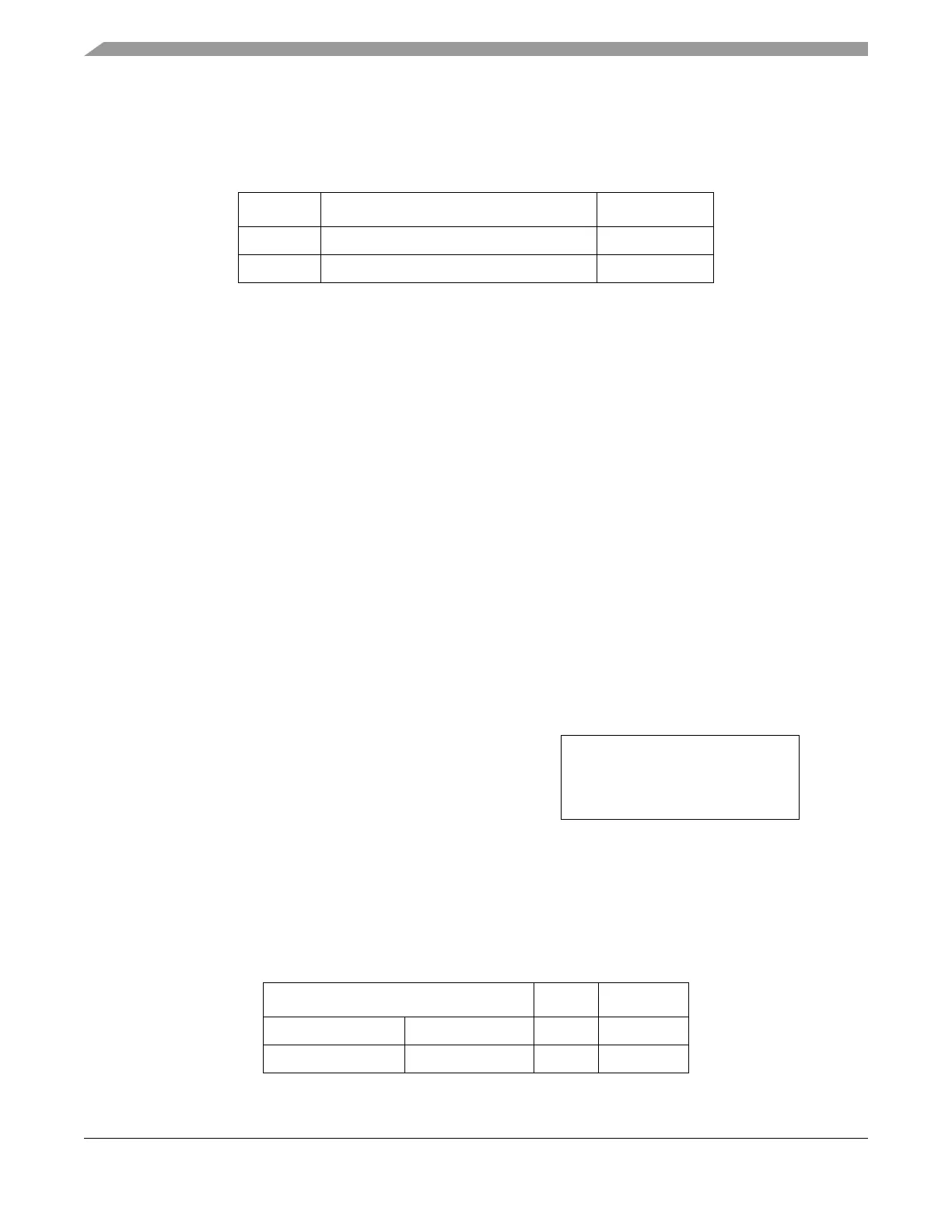

Table 13-2. Internal Flash External Emulation Mode

Address Range YYYYY Wait States

0x0000_0000 0x001F_FFFF 00000 0

0x0100_0000 0x011F_FFFF 01000 8

Flash Array Access or

0bYYYYY_0000_0000_0000_0000_0000_0000 -

Flash Shadow Row Access

YYYYY - additional primary wait-states

0bYYYYY_1111_1111_1111_1111_1111_1111

Loading...

Loading...