MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

20-32 Freescale Semiconductor

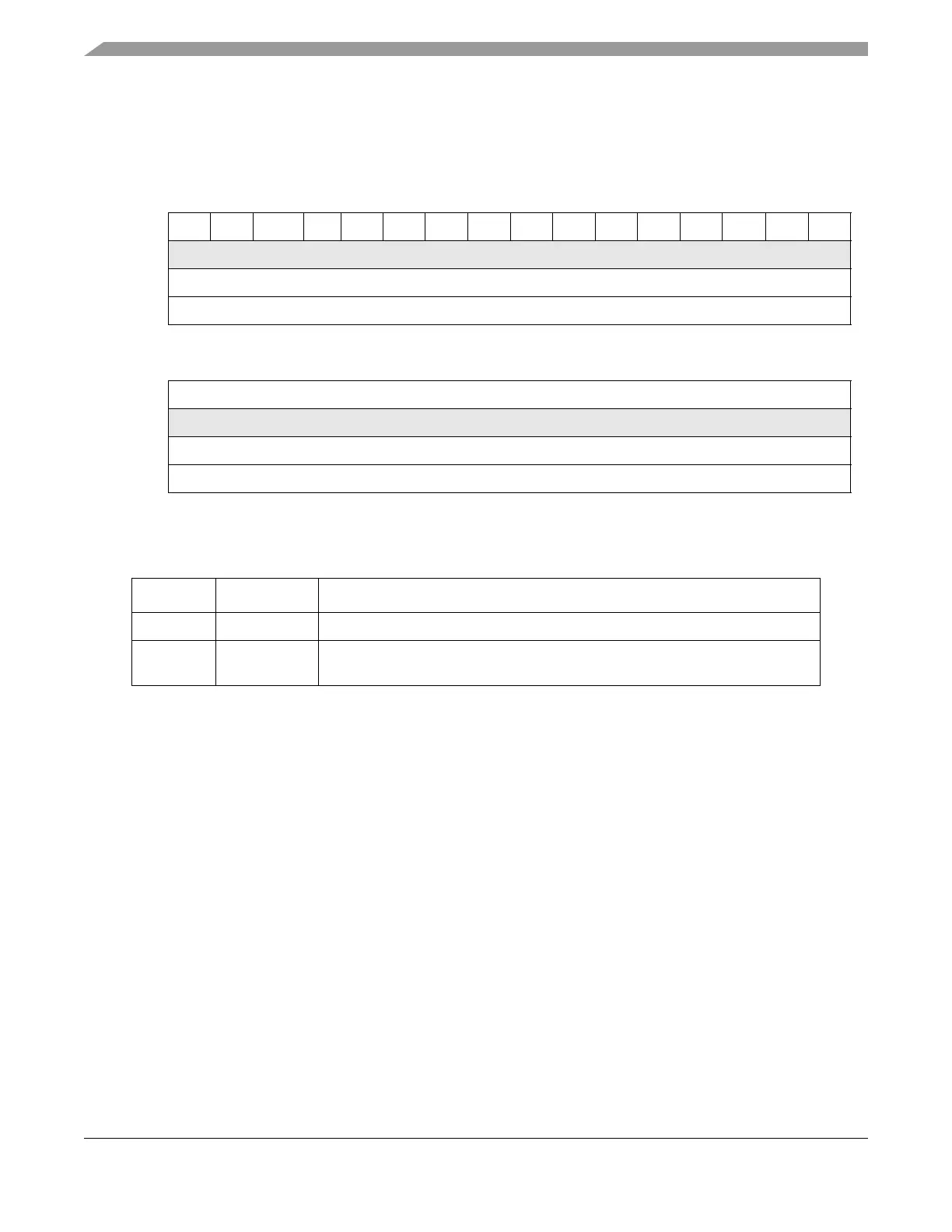

20.3.2.14 DSPI DSI Deserialization Data Register (DSPIx_DDR)

The DSPIx_DDR holds the signal states for the parallel output signals. The DSPIx_DDR is read-only and

it is memory mapped so that host software can read the incoming DSI frames.

20.4 Functional Description

The DSPI supports full-duplex, synchronous serial communications between the MPC5553/MPC5554 and

peripheral devices. The DSPI can also be used to reduce the number of pins required for I/O by serializing

and deserializing up to 16 parallel input/output signals from the eTPU and eMIOS. All communications

are through an SPI-like protocol.

The DSPI has three configurations:

• SPI configuration in which the DSPI operates as a basic SPI or a queued SPI.

• DSI configuration in which the DSPI serializes and deserializes parallel input/output signals or bits

from memory mapped registers.

• CSI configuration in which the DSPI combines the functionality of the SPI and DSI configurations.

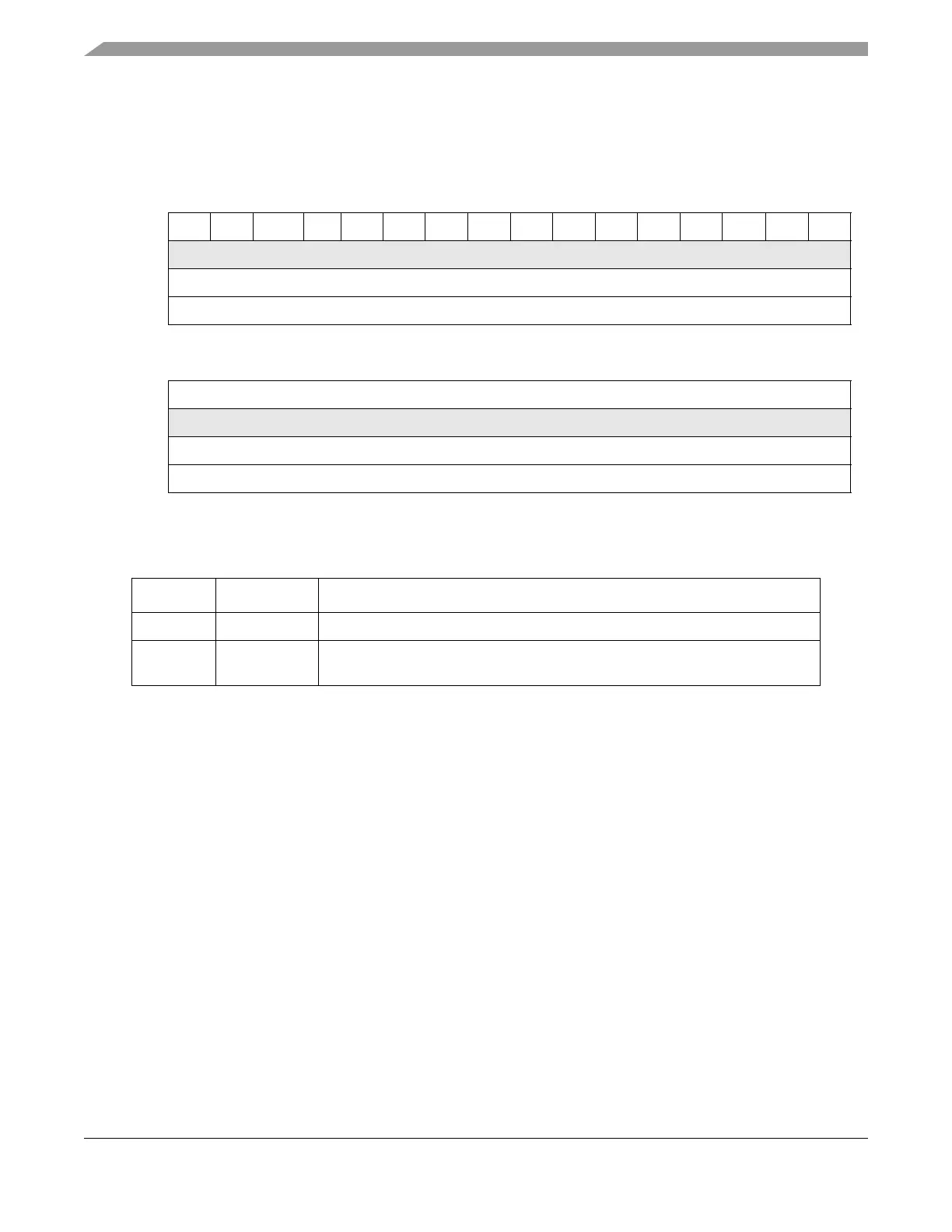

The DCONF field in the DSPIx_MCR register determines the DSPI configuration. See Table 20-3 for the

DSPI configuration values.

The DSPIx_CTAR0–DSPIx_CTAR7 registers hold clock and transfer attributes. The manner in which a

CTAR is selected depends on the DSPI configuration (SPI, DSI, or CSI). The SPI configuration can select

which CTAR to use on a frame by frame basis by setting the CTAS field in the DSPIx_PUSHR. The DSI

configuration statically selects which CTAR to use. In CSI configuration, priority logic determines if SPI

data or DSI data is transferred. The type of data transferred (whether DSI or SPI) dictates which CTAR the

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R00 00000000000000

W

Reset00 00000000000000

Reg Addr Base + 0x00CC

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R DESER_DATA

W

Reset00 00000000000000

Reg Addr Base + 0x00CC

Figure 20-16. DSPI Deserialization Data Register (DSPIx_DDR)

Table 20-16. DSPIx_DDR Field Description

Bits Name Description

0–15 — Reserved.

16–31 DESER_DATA Deserialized data. Holds deserialized data which is presented as signal states to

the parallel output signals.

Loading...

Loading...