MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-26 Freescale Semiconductor

Single-beat transfers are supported for cache-inhibited read and write cycles, and write-buffer writes. Burst

transfers of four doublewords are supported for cache linefill and copyback operations.

3.3.5 Timer Facilities

The core provides a set of registers to provide fixed interval timing and watchdog functions for the system.

All of these must be initialized during start-up. The registers associated with fixed interval timer and

watchdog functions are the following:

• Timer control register (TCR) – provides control of the timer and watchdog facilities.

• Timer status register (TSR) – provides status of the timer facilities.

• Time base registers (TBU and TBL) – Two 32-bit registers (upper and lower) that are concatenated

to provide a long-period, 64-bit counter.

• Decrementer register (DEC) – a decrementing counter that is updated at the same rate as the time

base. The DEC provides a means of signaling an exception after a specified amount of time. The

DEC is typically used as a general-purpose software timer. Note that the decrementer always runs

when the system is clocked, and may be written to by software at any time.

• Decrementer auto reload register (DECAR) – provides a value that is automatically reloaded (if

enabled) into the decrementer register when the decrementer reaches 0.

For more information on the fixed-interval timer, watchdog timer, and timer and counter registers, refer to

the e200z6 PowerPC

TM

Core Reference Manual and EREF: A Reference for Freescale Book E and the

e500 core.

3.3.6 Signal Processing Extension APU (SPE APU)

3.3.6.1 Overview

The Power Architecture embedded category 32-bit instructions operate on the lower (least significant) 32

bits of the 64-bit GPRs. New SPE instructions are defined that view the 64-bit register as being composed

of a vector of two 32-bit elements, and some of the instructions also read or write 16-bit elements. These

new instructions can also be used to perform scalar operations by ignoring the results of the upper 32-bit

half of the register file. Some instructions are defined that produce a 64-bit scalar result. Vector fixed-point

instructions operate on a vector of two 32-bit or four 16-bit fixed-point numbers resident in the 64-bit

GPRs. Vector floating-point instructions operate on a vector of two 32-bit single-precision floating-point

numbers resident in the 64-bit GPRs. Scalar floating-point instructions operate on the lower half of GPRs.

These single-precision floating-point instructions do not have a separate register file; there is a single

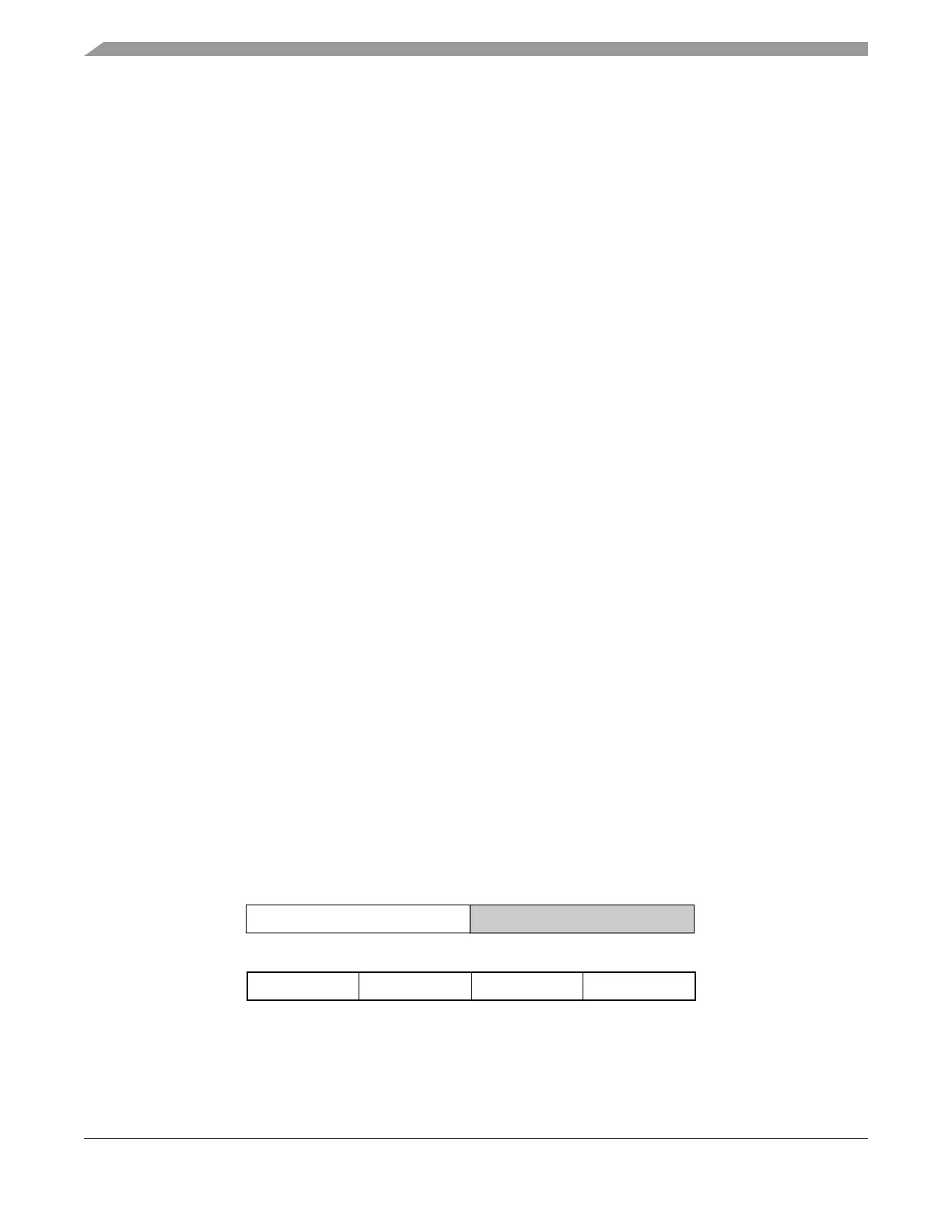

shared register file for all instructions. Figure 3-16 shows two different representations of the 64-bit GPRs.

The shaded half is the only region operated on by the 32-bit Power Architecture embedded category

instructions.

Figure 3-16. 64-bit General-Purpose Registers

0313263

GPRx

Lower/Least Significant Word

Upper/Most Significant Word

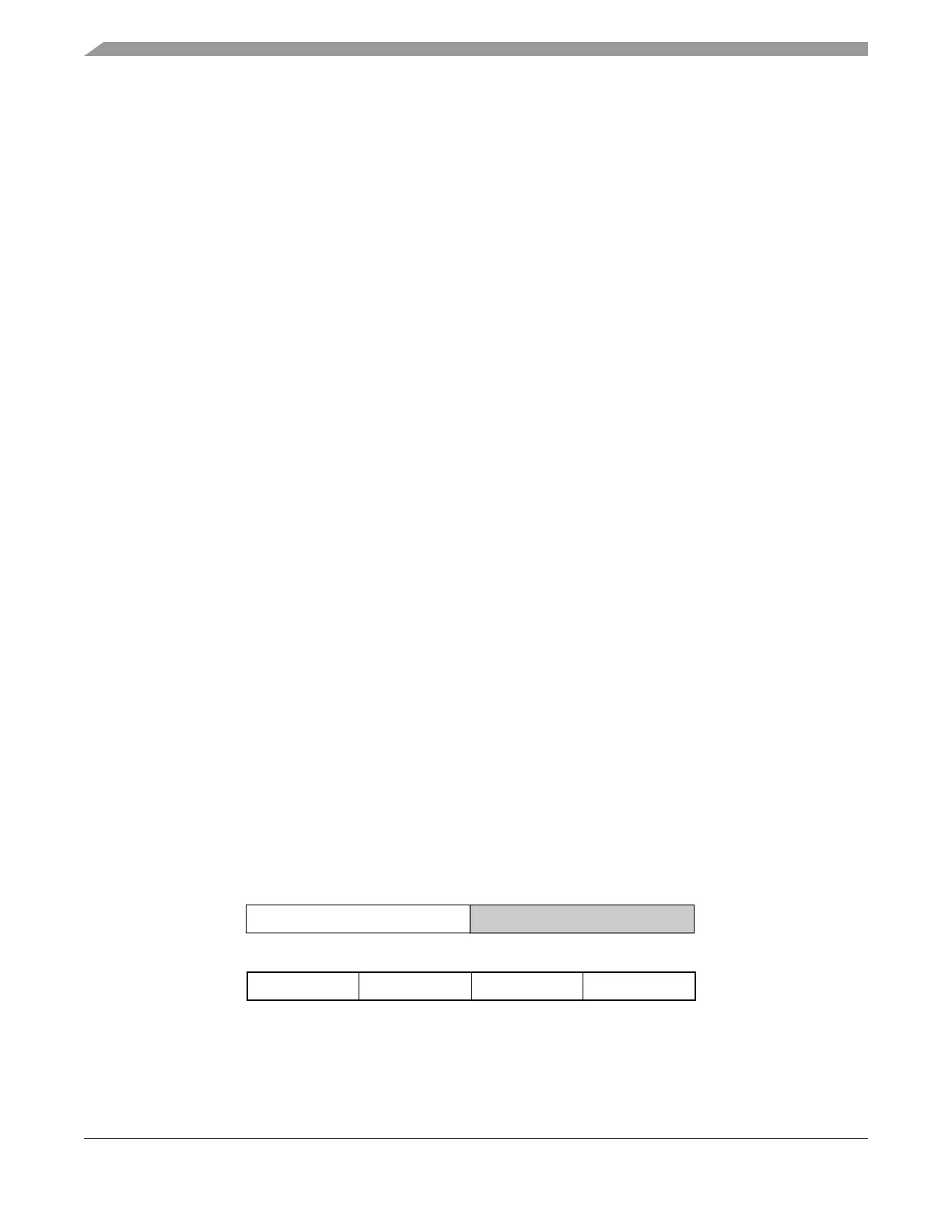

15 16 47 48

0313263

GPRx

Loading...

Loading...