System Interface Unit (SIU)

MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 6-105

6.3.1.23 Compare B Low Register (SIU_CBRL)

The SIU_CBRL holds the 32-bit value that is compared against the value in the SIU_CARL. The CMPBL

field is read/write and is reset by the synchronous reset signal.

6.4 Functional Description

The following sections provide an overview of the SIU operation.

6.4.1 System Configuration

6.4.1.1 Boot Configuration

The BOOTCFG[0:1] pins are used to determine the boot mode initiated by the BAM program, and whether

external arbitration is selected for external booting. The BAM program uses the BOOTCFG field to

determine where to read the reset configuration halfword (RCHW), and whether to initiate a FlexCAN or

eSCI boot. Refer to Section 16.3.2.2.5, “Reset Configuration Halfword Read of the BAM chapter for detail

on the RCHW. Table 6-53 defines the boot modes specified by the BOOTCFG[0:1] pins. If the RSTCFG

pin is asserted during the assertion of RSTOUT

, except in the case of a software external reset, the

BOOTCFG pins are latched 4 clock cycles prior to the negation of the RSTOUT

pin and are used to update

the SIU_RSR and the BAM boot mode. Otherwise, if RSTCFG is negated during the assertion of

RSTOUT, the BOOTCFG pins are ignored and the boot mode defaults to boot from internal flash memory.

Address: Base + 0x0994 Access: Read / write[0:31]

0123456789101112131415

R

CMPBL

W

Reset

0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

CMPBL

W

Reset

0000000000000000

Figure 6-140. Compare B Low Register (SIU_CBRL)

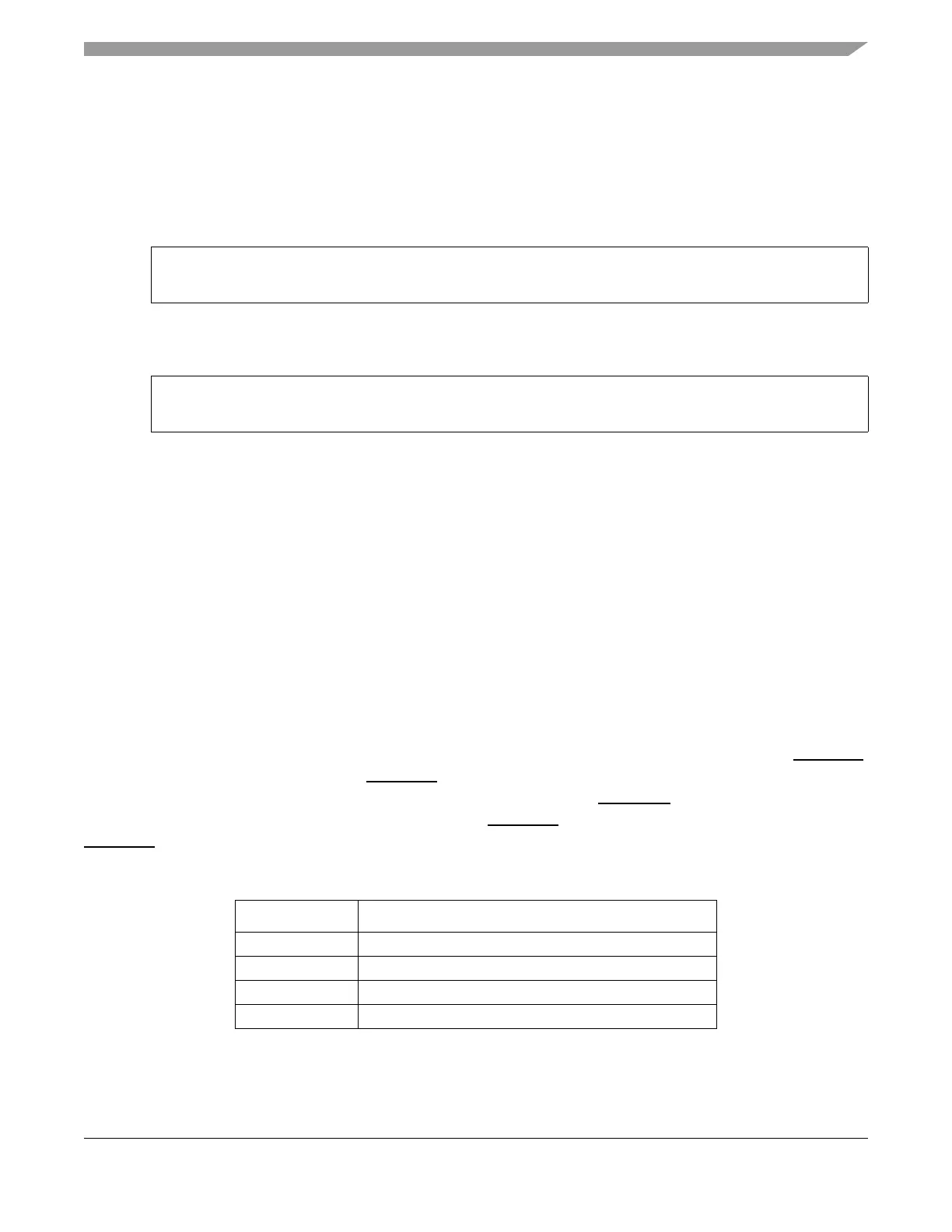

Table 6-53. BOOTCFG[0:1] Configuration

Value Meaning

0b00 Boot from internal flash memory

0b01 FlexCAN/eSCI boot

0b10 Boot from external memory (no arbitration)

0b11 Boot from external memory (external arbitration)

Loading...

Loading...