MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 5-1

Chapter 5

Peripheral Bridge (PBRIDGE_A, PBRIDGE_B)

5.1 Introduction

5.1.1 Block Diagram

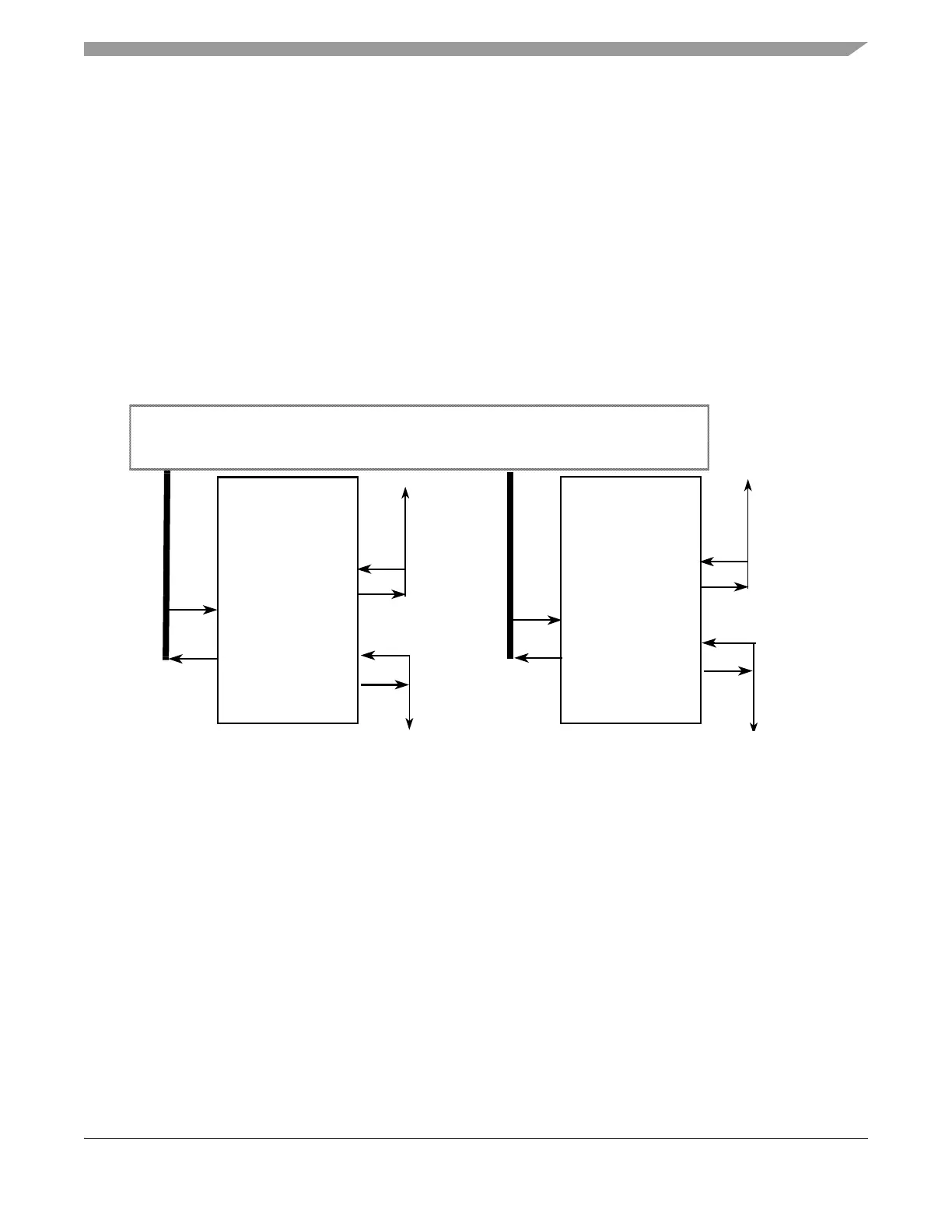

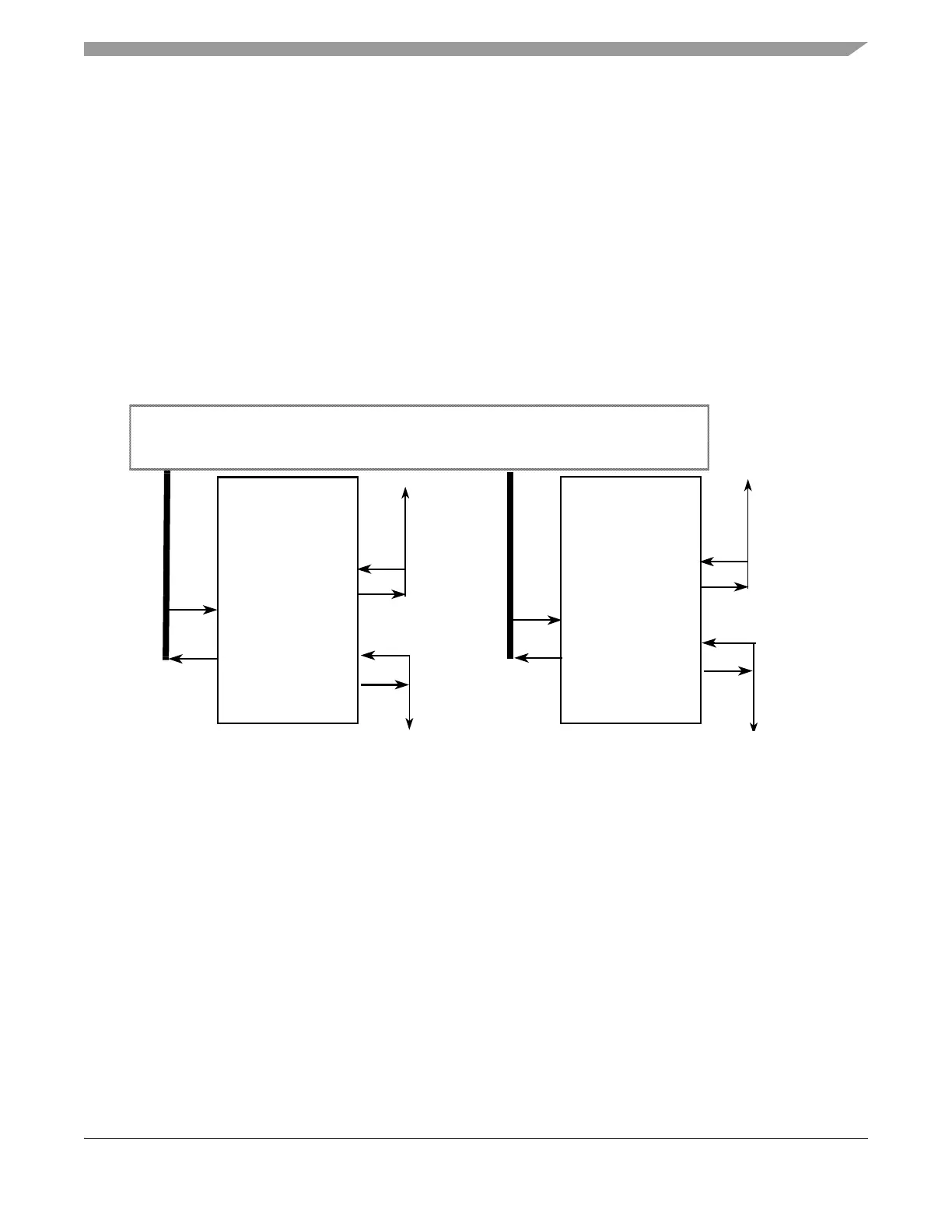

The PBRIDGE is the interface between the system bus and on-chip peripherals as shown in Figure 5-1.

Figure 5-1. PBRIDGE Interface

5.1.2 Overview

There are two peripheral bridges, PBRIDGE_A and PBRIDGE_B, which act as interfaces between the

system bus and lower bandwidth peripherals. In this manual, PBRIDGE refers to either of these bridges,

as their functionality is identical. The only difference is the peripherals to which they connect. Accesses

that fall within the address space of the PBRIDGE are decoded to provide individual module selects for

peripheral devices on the slave bus interface.

5.1.2.1 Access Protections

The PBRIDGE provides programmable access protections for both masters and peripherals. It allows the

privilege level of a master to be overridden, forcing it to user mode privilege, and allows masters to be

designated as trusted or untrusted. Peripherals may require supervisor privilege level for access, may

restrict access to a trusted master only, and may be write-protected. See Table 5-1 for a list of master/slave

IDs and the peripherals associated with each master and slave. More information on access protection may

be found in Section 13.3.2.9, “Flash Bus Interface Unit Access Protection Register (FLASH_BIUAPR).”

Off-platform Slave

Peripheral

On-platform Slave

Peripheral

Bridge A

(PBRIDGE_B)(PBRIDGE_A)

Bridge B

Off-platform Slave

System Bus

System Bus

System Bus Crossbar Switch (XBAR)

On-platform Slave

Loading...

Loading...