MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 5-5

5.3.1 Register Descriptions

There are three types of registers that control each PBRIDGE. All registers are 32-bit registers and can

only be accessed in supervisor mode by trusted bus masters. Additionally, these registers must only be read

from or written to by a 32-bit aligned access. PBRIDGE registers are mapped into the PBRIDGE_A and

PBRIDGE_B address spaces. The protection and access fields of the MPR, PACR, and OPACR registers

are 4 bits in width.

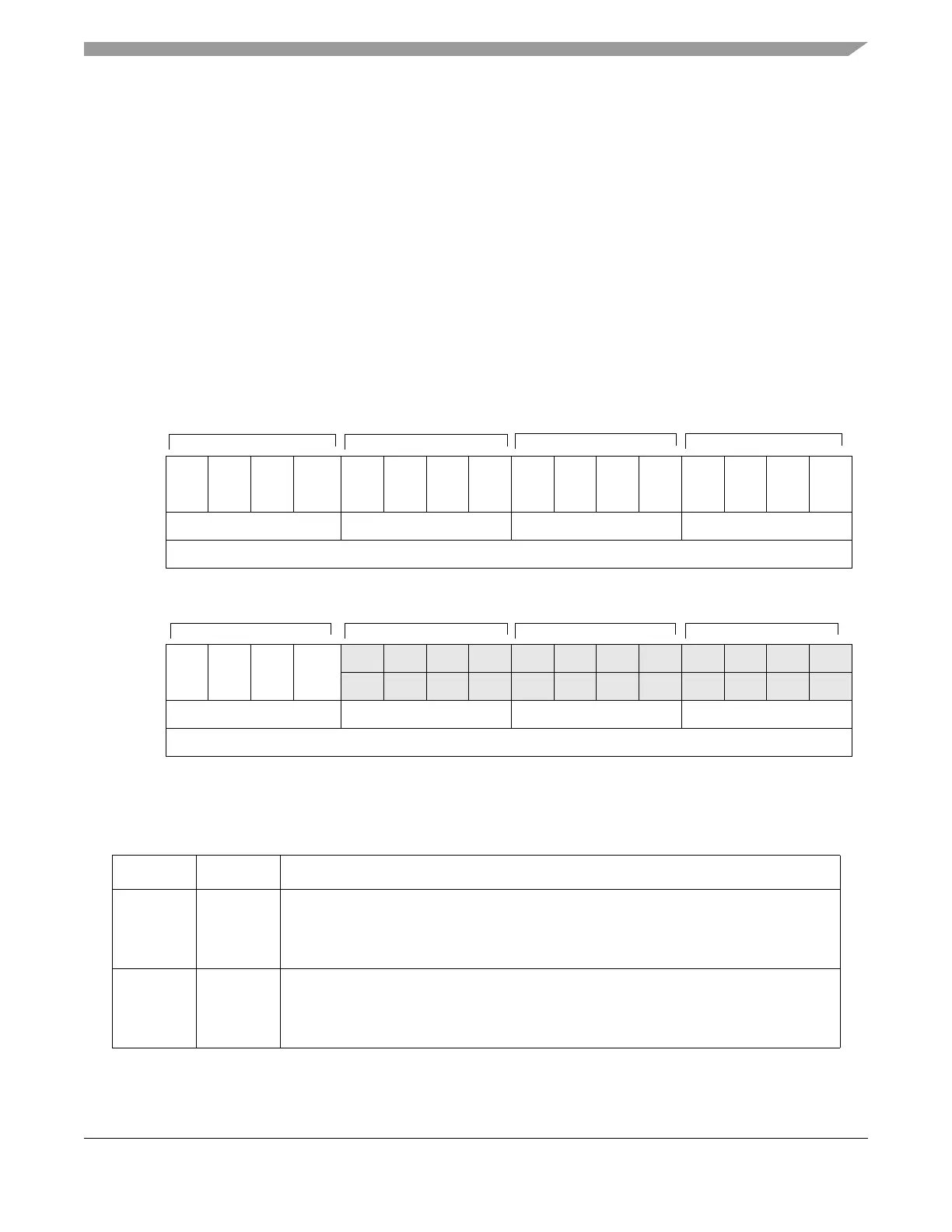

5.3.1.1 Master Privilege Control Register (PBRIDGE_x_MPCR)

Each master privilege control register (PBRIDGE_x_MPCR) specifies 4-bit access fields defining the

access privilege level associated with a bus master in the platform, as well as specifying whether write

accesses from this master are bufferable. The registers provide one field per bus master. Note that access

field 4 is available only in the MPC5553.

012 3 456789101112131415

RMBW

0

MTR

0

MTW

0

MPL

0

MBW

1

MTR

1

MTW

1

MPL

1

MBW

2

MTR

2

MTW

2

MPL

2

MBW

3

MTR

3

MTW

3

MPL

3

W

Reset011 1 011101110111

Reg Addr Base + 0x0000

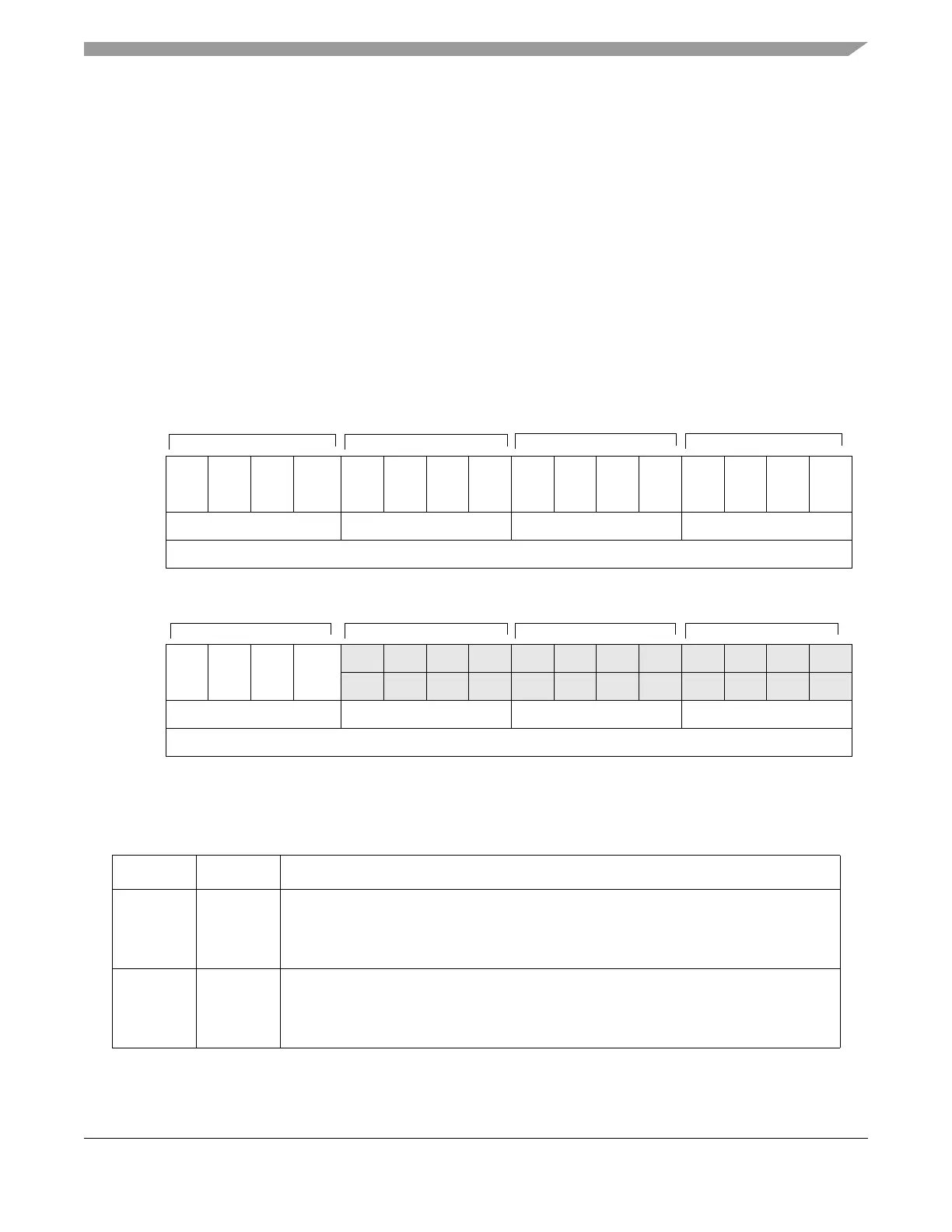

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RMBW

4

1

1

Available only in the MPC5553

MTR

4

1

MTW

4

1

MPL

4

1

W

Reset011 1 011101110111

Reg Addr Base + 0x0000

Figure 5-2. Master Privilege Control Registers (PBRIDGE_x_MPCR)

Table 5-4. PBRIDGE_x_MPCR Field Descriptions

Bits Name Description

0 MBW0 Master buffer writes. Determines whether the PBRIDGE is enabled to buffer writes from

the CPU. Writes not able to be buffered by default.

0 Write accesses from the CPU are not bufferable

1 Write accesses from the CPU are allowed to be buffered

1 MTR0 Master trusted for reads. Determines whether the CPU is trusted for read accesses.

Trusted by default.

0 The CPU is not trusted for read accesses.

1 The CPU is trusted for read accesses.

Loading...

Loading...