MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

5-6 Freescale Semiconductor

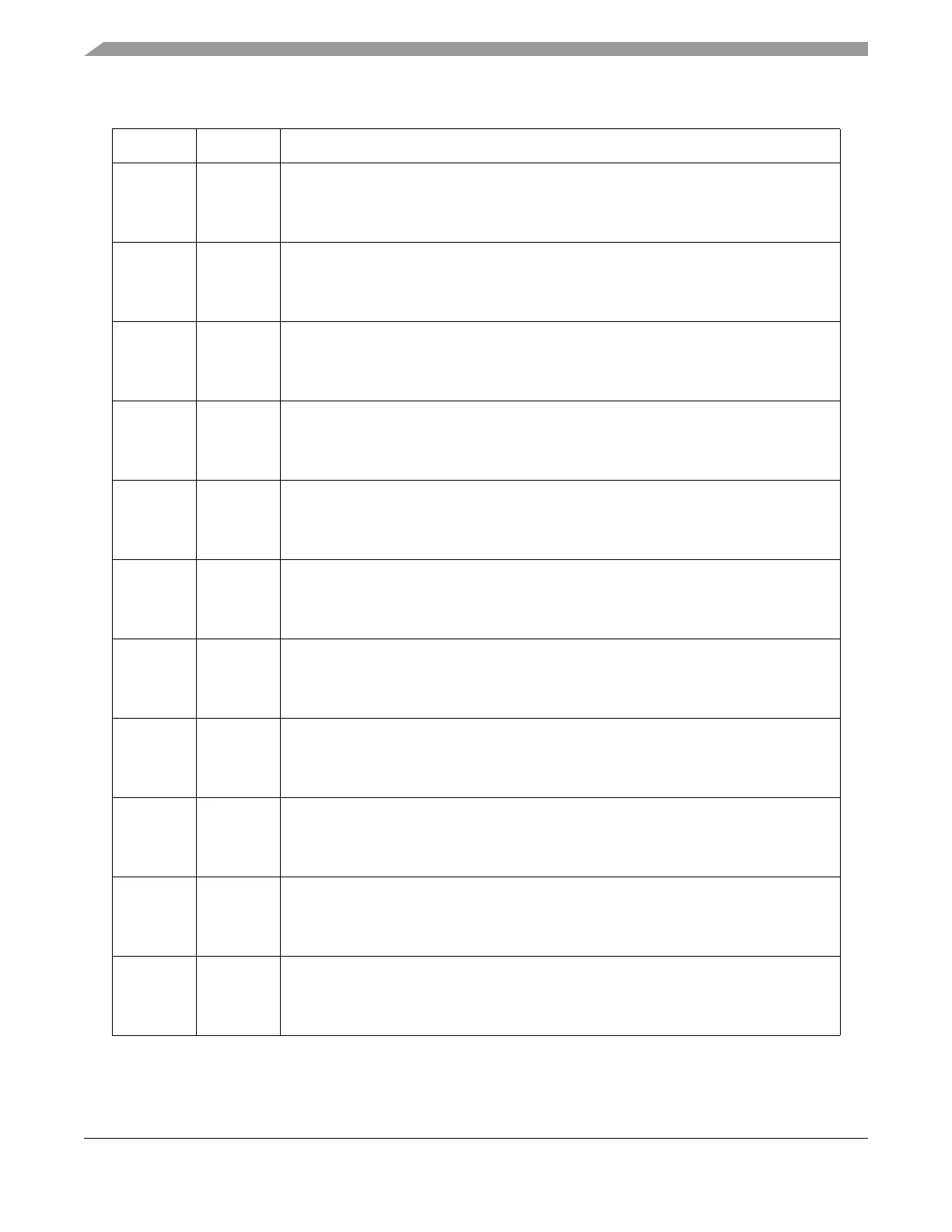

2 MTW0 Master trusted for writes. Determines whether the master is trusted for write accesses.

Trusted by default.

0 The CPU is not trusted for write accesses.

1 The CPU is trusted for write accesses.

3 MPL0 Master privilege level. Determines how the privilege level of the CPU is determined.

Accesses not forced to user mode by default.

0 Accesses from the CPU are forced to user mode.

1 Accesses from the CPU are not forced to user mode.

4 MBW1 Master buffer writes. Determines whether the PBRIDGE is enabled to buffer writes from

the Nexus. Writes not able to be buffered by default.

0 Write accesses from the Nexus are not bufferable

1 Write accesses from the Nexus are allowed to be buffered

5 MTR1 Master trusted for reads. Determines whether the Nexus is trusted for read accesses.

Trusted by default.

0 The Nexus is not trusted for read accesses.

1 The Nexus is trusted for read accesses.

6 MTW1 Master trusted for writes. Determines whether the master is trusted for write accesses.

Trusted by default.

0 The Nexus is not trusted for write accesses.

1 The Nexus is trusted for write accesses.

7 MPL1 Master privilege level. Determines how the privilege level of the Nexus is determined.

Accesses not forced to user mode by default.

0 Accesses from the Nexus are forced to user mode.

1 Accesses from the Nexus are not forced to user mode.

8 MBW2 Master buffer writes. Determines whether the PBRIDGE is enabled to buffer writes from

the eDMA. Writes not able to be buffered by default.

0 Write accesses from the eDMA are not bufferable

1 Write accesses from the eDMA are allowed to be buffered

9 MTR2 Master trusted for reads. Determines whether the eDMA is trusted for read accesses.

Trusted by default.

0 The eDMA is not trusted for read accesses.

1 The eDMA is trusted for read accesses.

10 MTW2 Master trusted for writes. Determines whether the master is trusted for write accesses.

Trusted by default.

0 The eDMA is not trusted for write accesses.

1 The eDMA is trusted for write accesses.

11 MPL2 Master privilege level. Determines how the privilege level of the eDMA is determined.

Accesses not forced to user mode by default.

0 Accesses from the eDMA are forced to user mode.

1 Accesses from the eDMA are not forced to user mode.

12 MBW3 Master buffer writes. Determines whether the PBRIDGE is enabled to buffer writes from

the EBI. Writes not able to be buffered by default.

0 Write accesses from the EBI are not bufferable

1 Write accesses from the EBI are allowed to be buffered

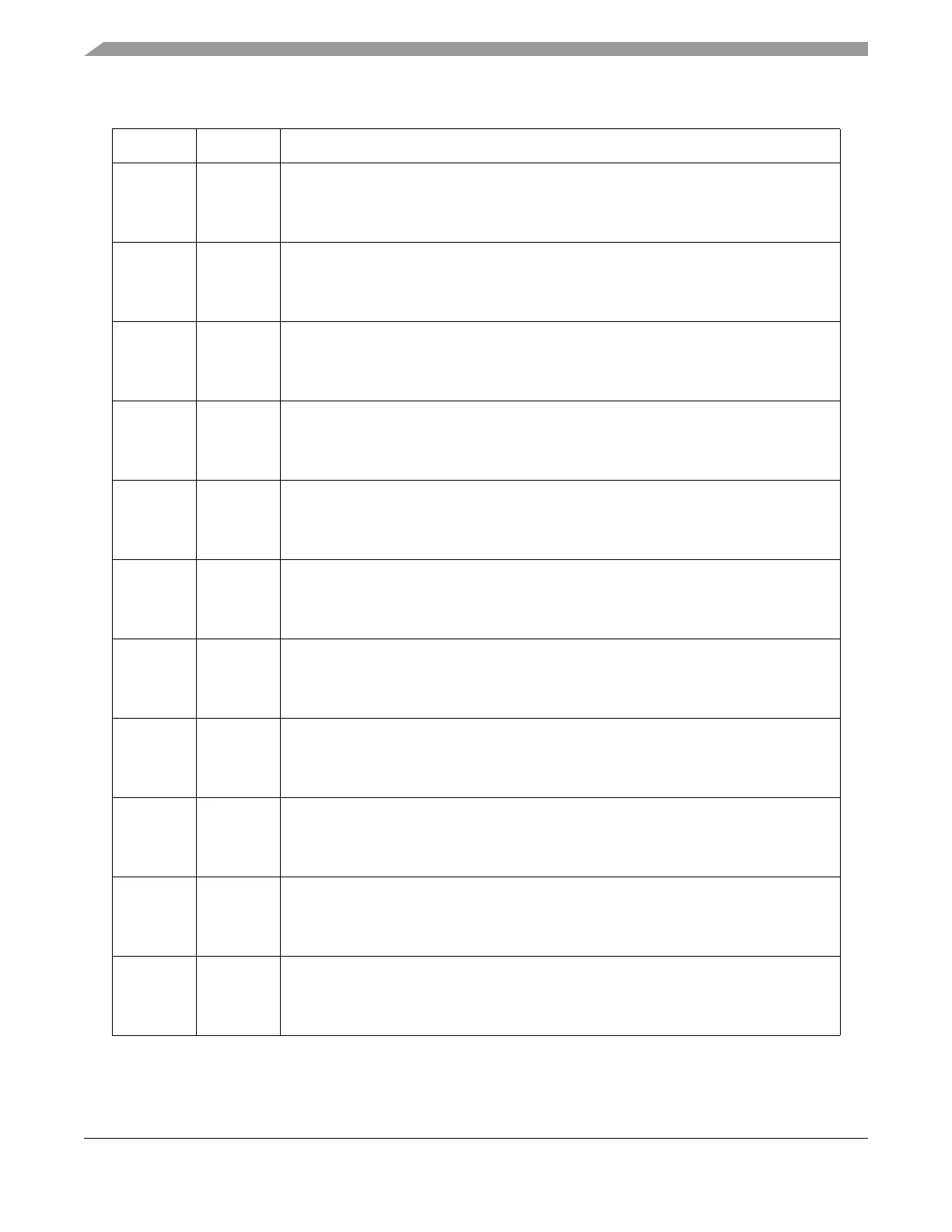

Table 5-4. PBRIDGE_x_MPCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...