MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

14-10 Freescale Semiconductor

14.3.4 Registers

14.3.4.1 FEC Burst Optimization Master Control Register (FBOMCR) (MPC5553

Only)

Although not an FEC register, the FEC burst optimization master control register (FBOMCR) controls

FEC burst optimization behavior on the system bus, hence it is described below. FEC registers are

described in Section 14.3.4.2.1, “Ethernet Interrupt Event Register (EIR)” through Section 14.3.4.3.4,

“Receive Buffer Size Register (EMRBR).”

In order to increase throughput, the FEC interface to the system bus can accumulate read requests or writes

to burst those transfers on the system bus. The FBOMCR determines the XBAR ports for which this

bursting is enabled, as well as whether the bursting is for reads, writes, or both. FBOMCR also controls

how errors for writes are handled. The FBOMCR address is 0xFFF4_0024, which is the ECSM base

address 0xFFF4_0000 plus the offset of 0x0024.

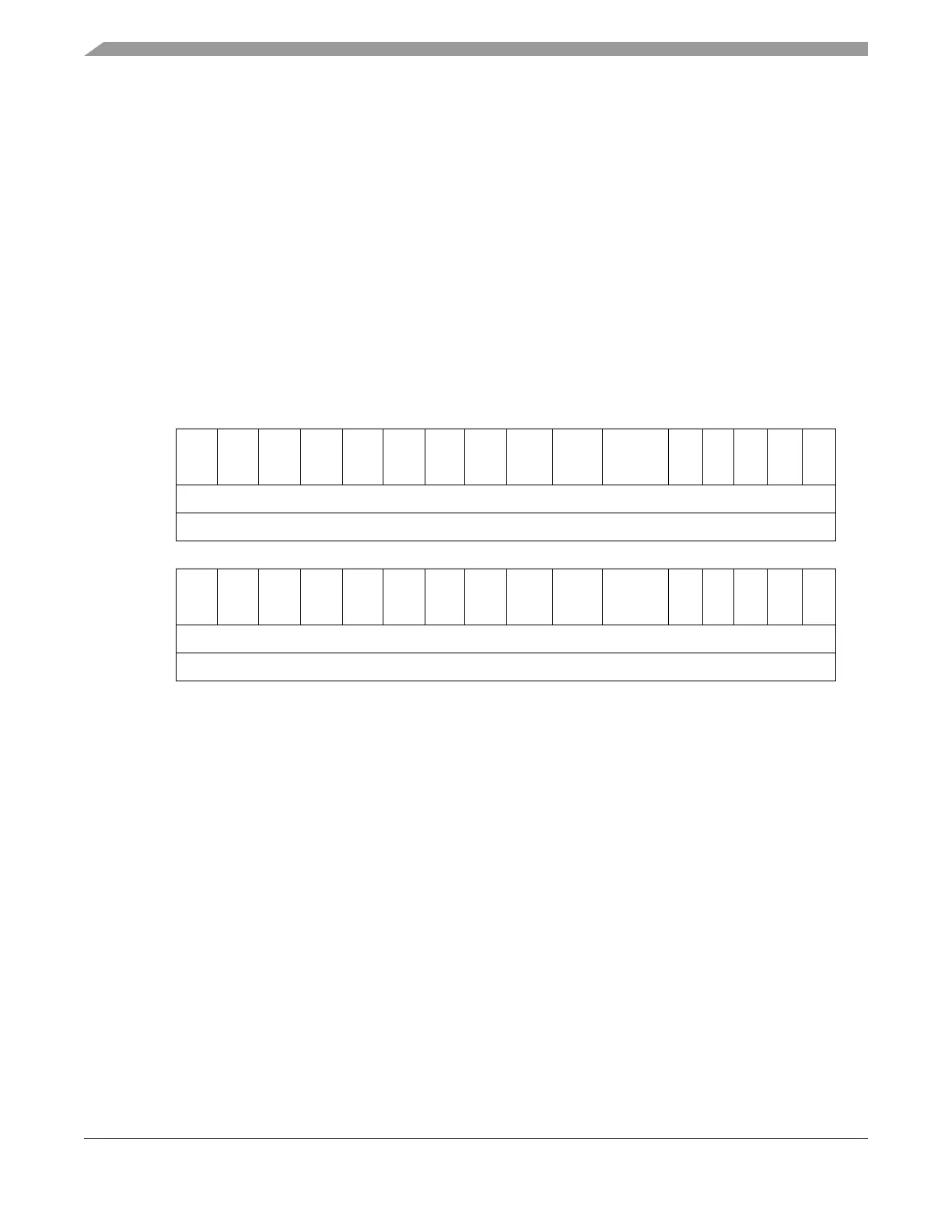

0 1234567 8 9 10 1112131415

RFXS

BE0

FXS

BE1

FXS

BE2

000FXS

BE6

FXS

BE7

RBEN WBEN ACCERR 0 0 0 0 0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Address ECSM Base Address: 0xFFF4_0000 + 0x0024 = 0xFFF4_0024

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Address ECSM Base Address: 0xFFF4_0000 + 0x0024 = 0xFFF4_0024

Figure 14-2. FEC Burst Optimization Master Control Register (FBOMCR)

Loading...

Loading...