MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 14-11

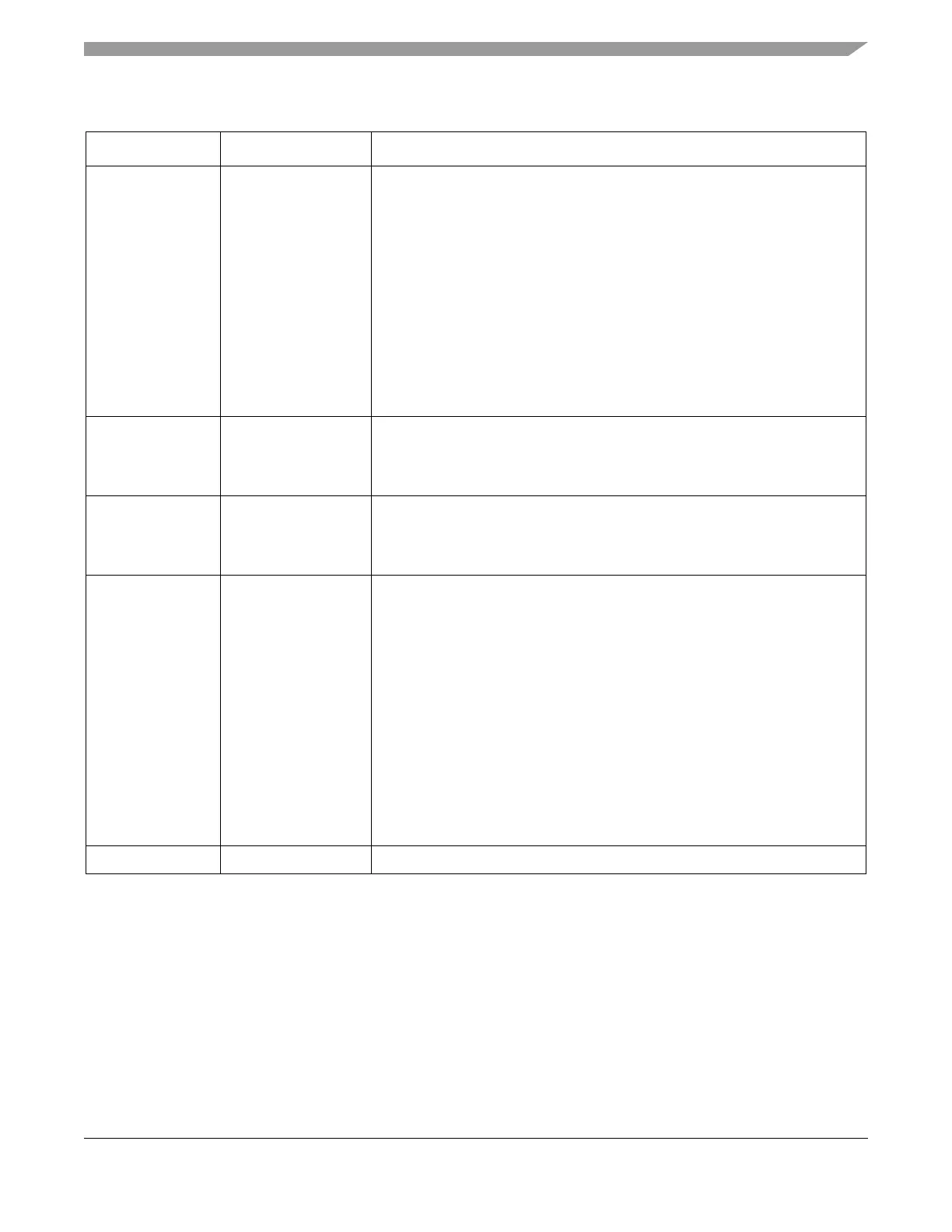

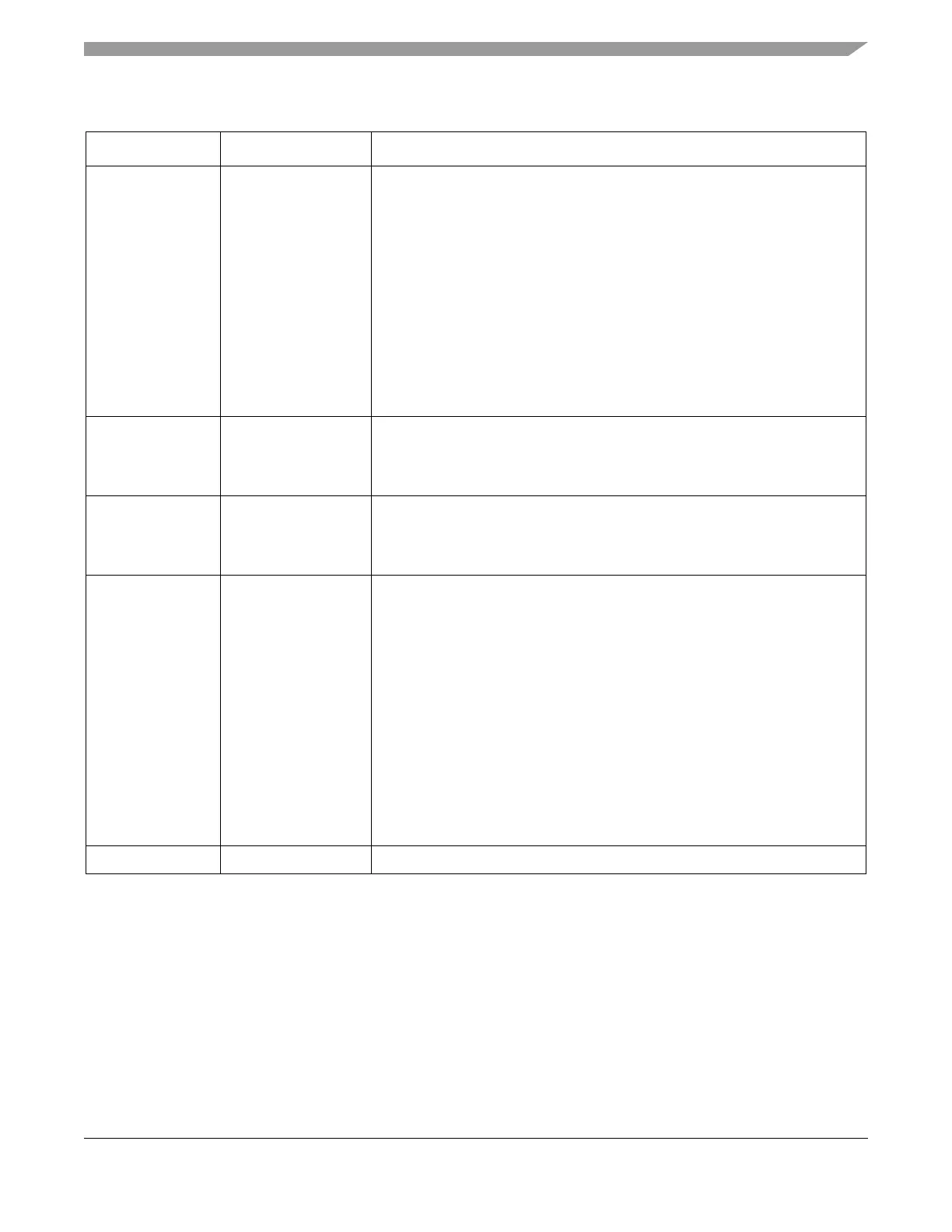

Table 14-4. FBOMCR Field Descriptions

Bits Name Description

0-7 FXSBEn

[0:7]

FXSBE – FEC XBAR slave burst enable. FXSBEn enables bursting by the FEC

interface to the XBAR slave port controlled by by that respective FXSBEn bit. If

FXSBEn is asserted, then that XBAR slave port enabled by the bit can accept

the bursts allowed by RBEN and WBEN. Otherwise, the FEC interface will not

burst to the XBAR slave port controlled by that respective FXSBEn bit. Read

bursts from that XBAR slave port are enabled by RBEN. Write bursts to that

XBAR slave port are enabled by WBEN.

FXSBEn assignments to XBAR slave ports:

FXSBE0 = Flash

FXSBE1 = EBI

FXSBE2 = Internal SRAM

FXSBE6 = Peripheral bridge A

FXSBE7 = Peripheral bridge B

8 RBEN Global read burst enable from XBAR slave port designated by FXSBEn

0 = Read bursting from all XBAR slave ports is disabled.

1 = Read bursting is enabled from any XBAR slave port whose FXSBEn bit is

asserted.

9 WBEN Global write burst enable to XBAR slave port designated by FXSBEn

0 = Write bursting to all XBAR slave ports is disabled.

1 = Write bursting is enabled to any XBAR slave port whose FXSBEn bit is

asserted.

10 ACCERR Accumulate error - This bit determines whether an error response for the first

half of the write burst is accumulated to the second half of the write burst or

discarded. In order to complete the burst, the FEC interface to the system bus

responds by indicating that the first half of the burst completed without error

before it actually writes the data so that it can fetch the second half of the write

data from the FIFO. When actually written onto the system bus, the first half of

the write burst can have an error. Because this half initially responded without

an error to the FIFO, the error is discarded or accumulated with the error

response for the second half of the burst.

0 Any error to the first half of the write burst is discarded.

1 Any actual error response to the first half of the write burst is accumulated in

the second half's response. In other words, an error response to the first half

will be seen in the response to the second half, even if the second half does

not error.

11-31 — Reserved, should be cleared.

Loading...

Loading...