MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

14-12 Freescale Semiconductor

14.3.4.2 FEC Registers

The following sections describe each FEC register in detail. The base address of these registers is

0xFFF4_C000.

14.3.4.2.1 Ethernet Interrupt Event Register (EIR)

When an event occurs that sets a bit in the EIR, an interrupt will be generated if the corresponding bit in

the interrupt mask register (EIMR) is also set. The bit in the EIR is cleared if a one is written to that bit

position; writing zero has no effect. This register is cleared upon hardware reset.

These interrupts can be divided into operational interrupts, transceiver/network error interrupts, and

internal error interrupts. Interrupts which may occur in normal operation are GRA, TXF, TXB, RXF, RXB,

and MII. Interrupts resulting from errors/problems detected in the network or transceiver are HBERR,

BABR, BABT, LC, and RL. Interrupts resulting from internal errors are HBERR and UN.

Some of the error interrupts are independently counted in the MIB block counters. Software may choose

to mask off these interrupts because these errors will be visible to network management via the MIB

counters:

• HBERR - IEEE_T_SQE

• BABR - RMON_R_OVERSIZE (good CRC), RMON_R_JAB (bad CRC)

• BABT - RMON_T_OVERSIZE (good CRC), RMON_T_JAB (bad CRC)

• LATE_COL - IEEE_T_LCOL

• COL_RETRY_LIM - IEEE_T_EXCOL

• XFIFO_UN - IEEET_MACERR

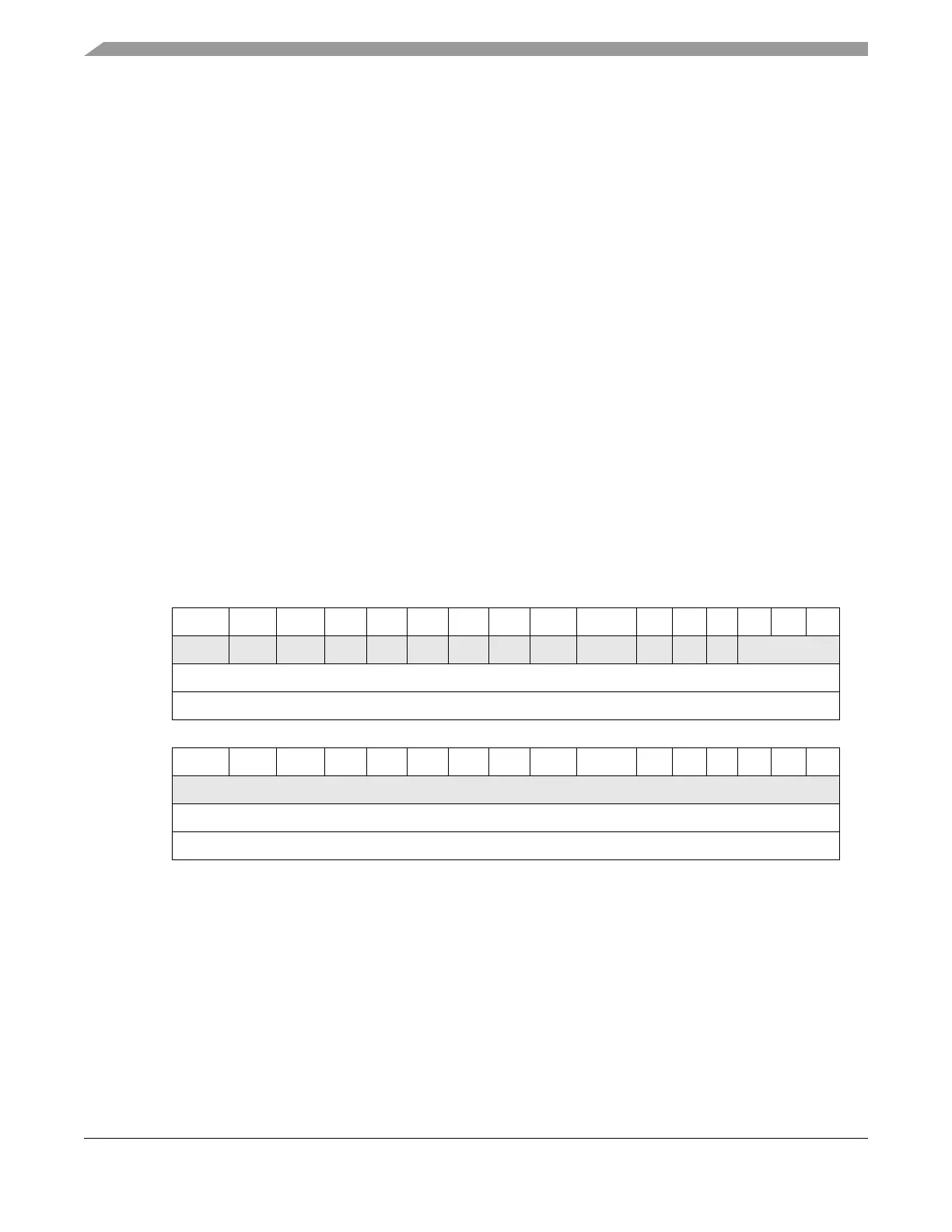

Figure 14-3. Ethernet Interrupt Event Register (EIR)

0 1 2 3 4 5 6 7 8 9 101112131415

R HBERR BABR BABT GRA TXF TXB RXF RXB MII EBERR LC RL UN 000

W w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c w1c

Reset0 0 0 00000 0 0 000000

Address Base (0xFFF4_C000) + 0x0004

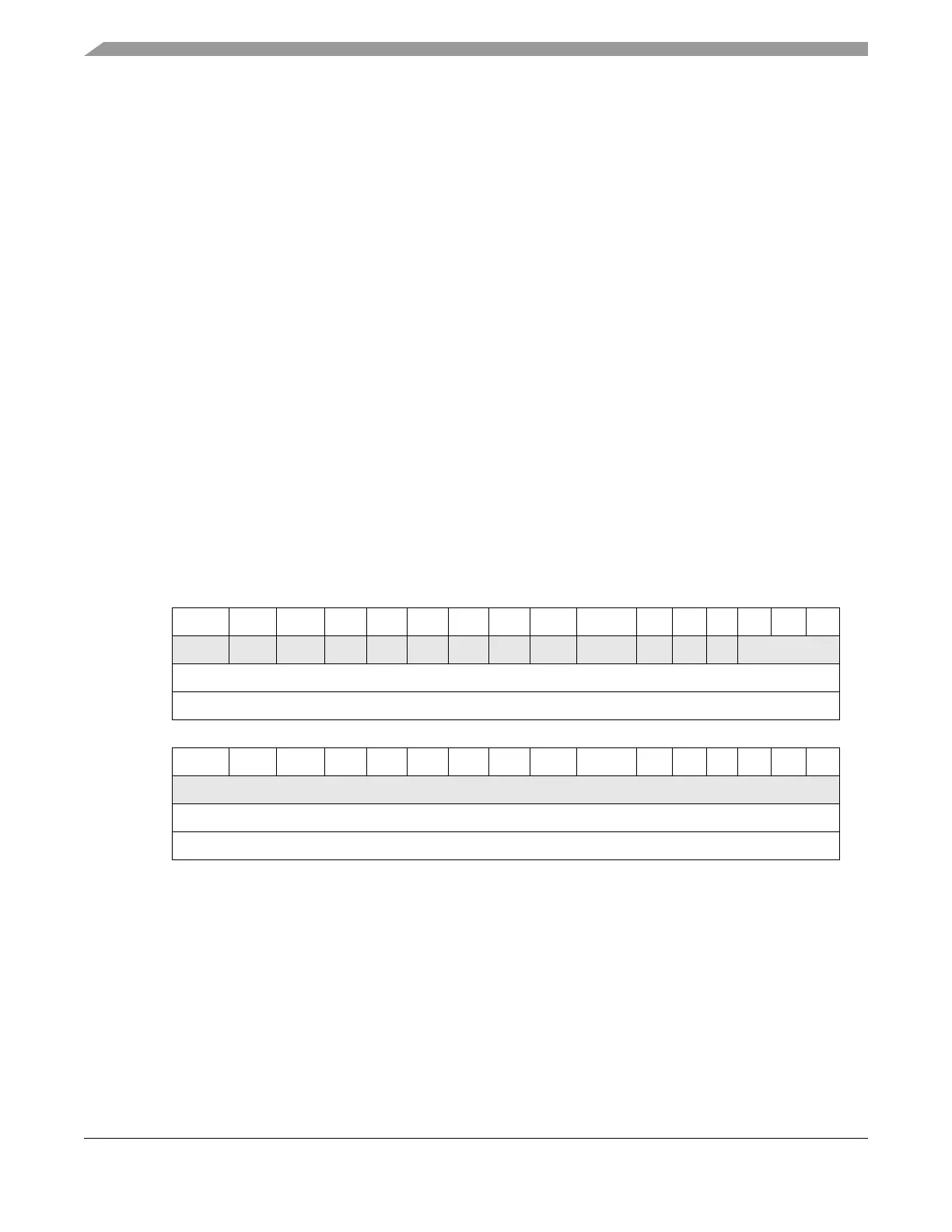

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 0 0 00000 0 0 000000

W

Reset0 0 0 00000 0 0 000000

Address Base (0xFFF4_C000) + 0x0004

1

“w1c” signifies the bit is cleared by writing 1 to it.

Loading...

Loading...