MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 14-13

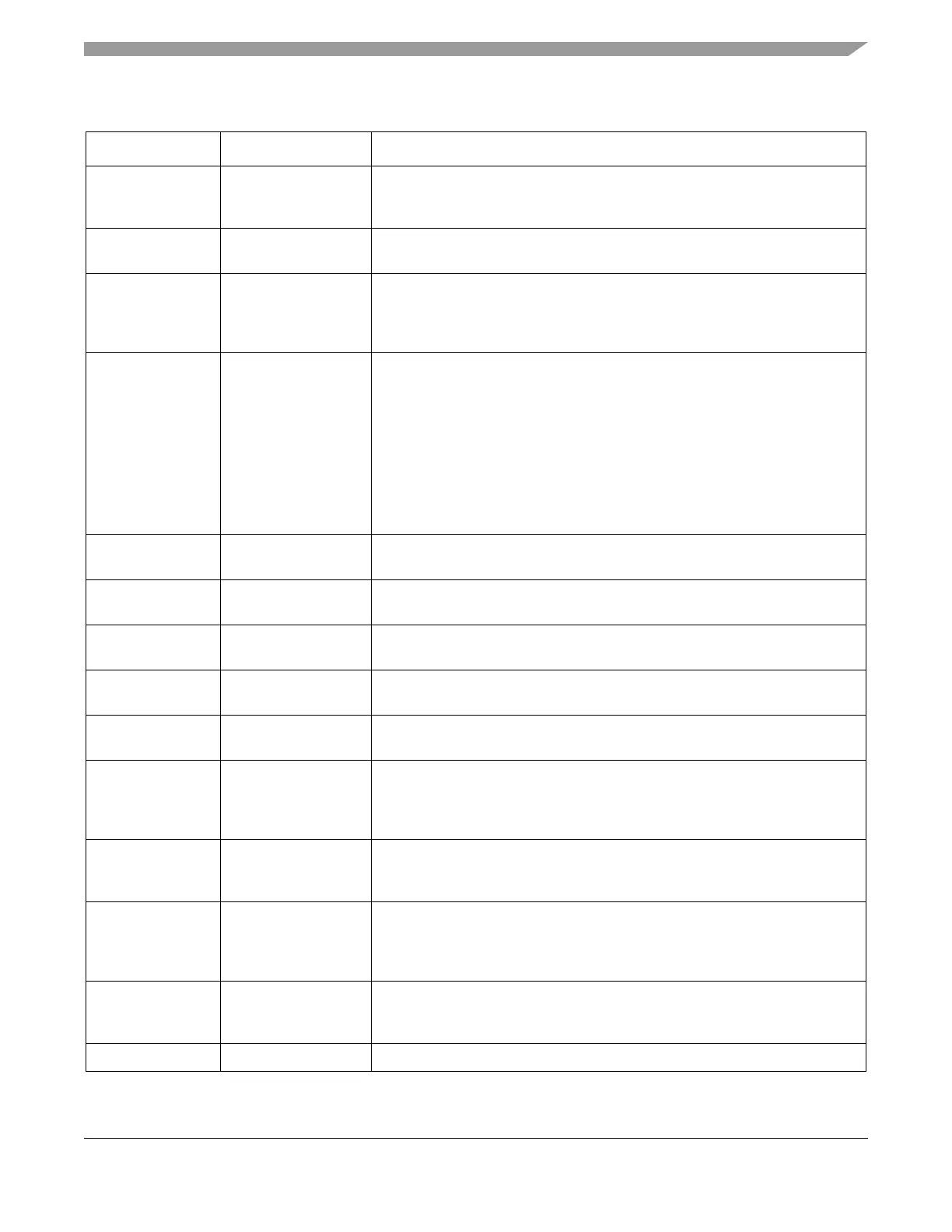

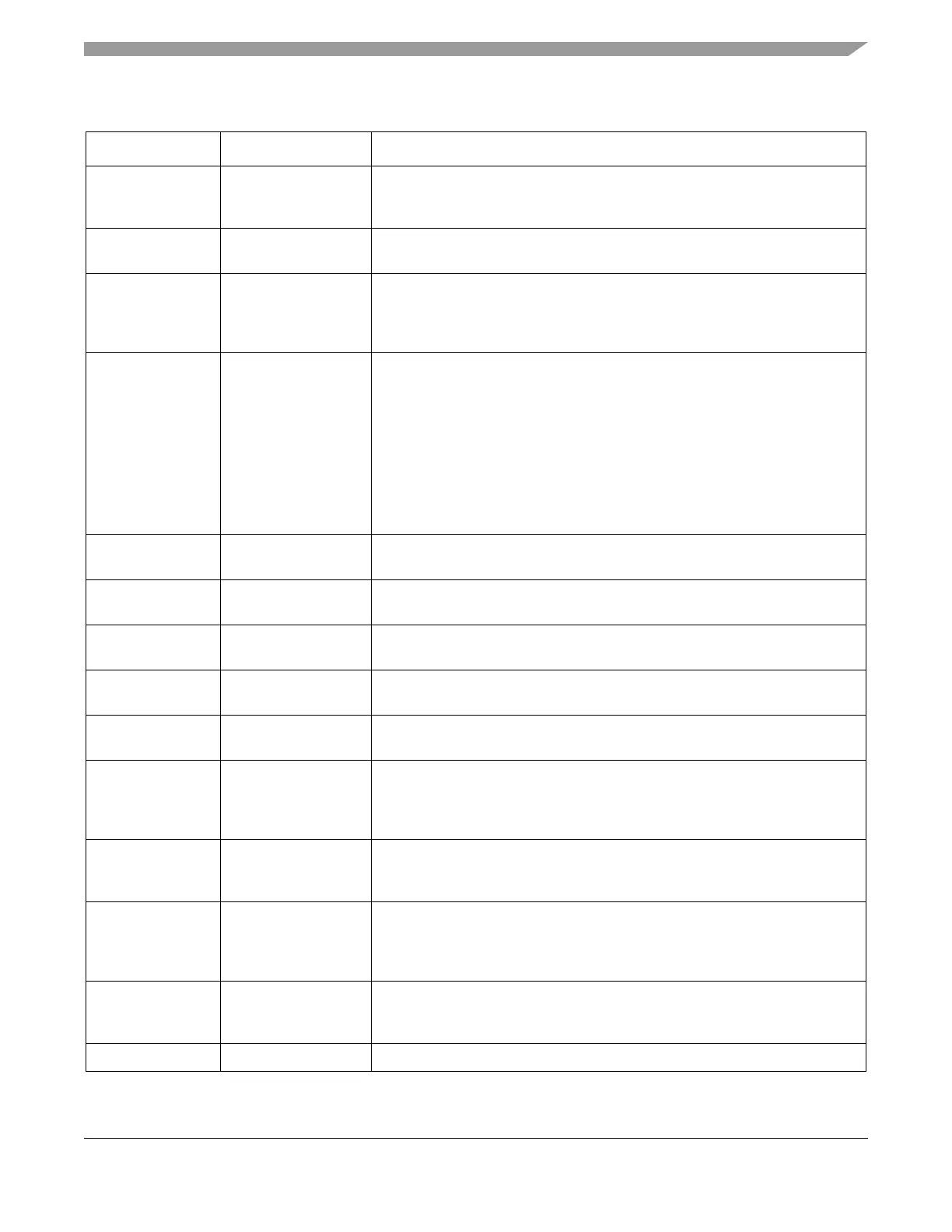

Table 14-5. EIR Field Descriptions

Bits Name Description

0 HBERR Heartbeat error. This interrupt indicates that HBC is set in the TCR register and

that the COL input was not asserted within the Heartbeat window following a

transmission.

1 BABR Babbling receive error. This bit indicates a frame was received with length in

excess of RCR[MAX_FL] bytes.

2 BABT Babbling transmit error. This bit indicates that the transmitted frame length has

exceeded RCR[MAX_FL] bytes. This condition is usually caused by a frame that

is too long being placed into the transmit data buffers. Truncation does not

occur.

3 GRA Graceful stop complete. This interrupt will be asserted for one of three reasons.

Graceful stop means that the transmitter is put into a pause state after

completion of the frame currently being transmitted.

1) A graceful stop, which was initiated by the setting of the TCR[GTS] bit is now

complete.

2) A graceful stop, which was initiated by the setting of the TCR[TFC_PAUSE]

bit is now complete.

3) A graceful stop, which was initiated by the reception of a valid full-duplex flow

control “pause” frame is now complete. Refer to Section 14.4.10, “Full-Duplex

Flow Control.”

4 TXF Transmit frame interrupt. This bit indicates that a frame has been transmitted

and that the last corresponding buffer descriptor has been updated.

5 TXB Transmit buffer interrupt. This bit indicates that a transmit buffer descriptor has

been updated.

6 RXF Receive frame interrupt. This bit indicates that a frame has been received and

that the last corresponding buffer descriptor has been updated.

7 RXB Receive buffer interrupt. This bit indicates that a receive buffer descriptor has

been updated that was not the last in the frame.

8 MII MII interrupt. This bit indicates that the MII has completed the data transfer

requested.

9 EBERR Ethernet bus error. This bit indicates that a system bus error occurred when a

DMA transaction was underway. When the EBERR bit is set, ECR[ETHER_EN]

will be cleared, halting frame processing by the FEC. When this occurs software

will need to insure that the FIFO controller and DMA are also soft reset.

10 LC Late collison. This bit indicates that a collision occurred beyond the collision

window (slot time) in half-duplex mode. The frame is truncated with a bad CRC

and the remainder of the frame is discarded.

11 RL Collision retry limit. This bit indicates that a collision occurred on each of 16

successive attempts to transmit the frame. The frame is discarded without being

transmitted and transmission of the next frame will commence. Can only occur

in half-duplex mode.

12 UN Transmit FIFO underrun. This bit indicates that the transmit FIFO became empty

before the complete frame was transmitted. A bad CRC is appended to the

frame fragment and the remainder of the frame is discarded.

13-31 — Reserved, should be cleared.

Loading...

Loading...