MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-13

12.3 Memory Map/Register Definition

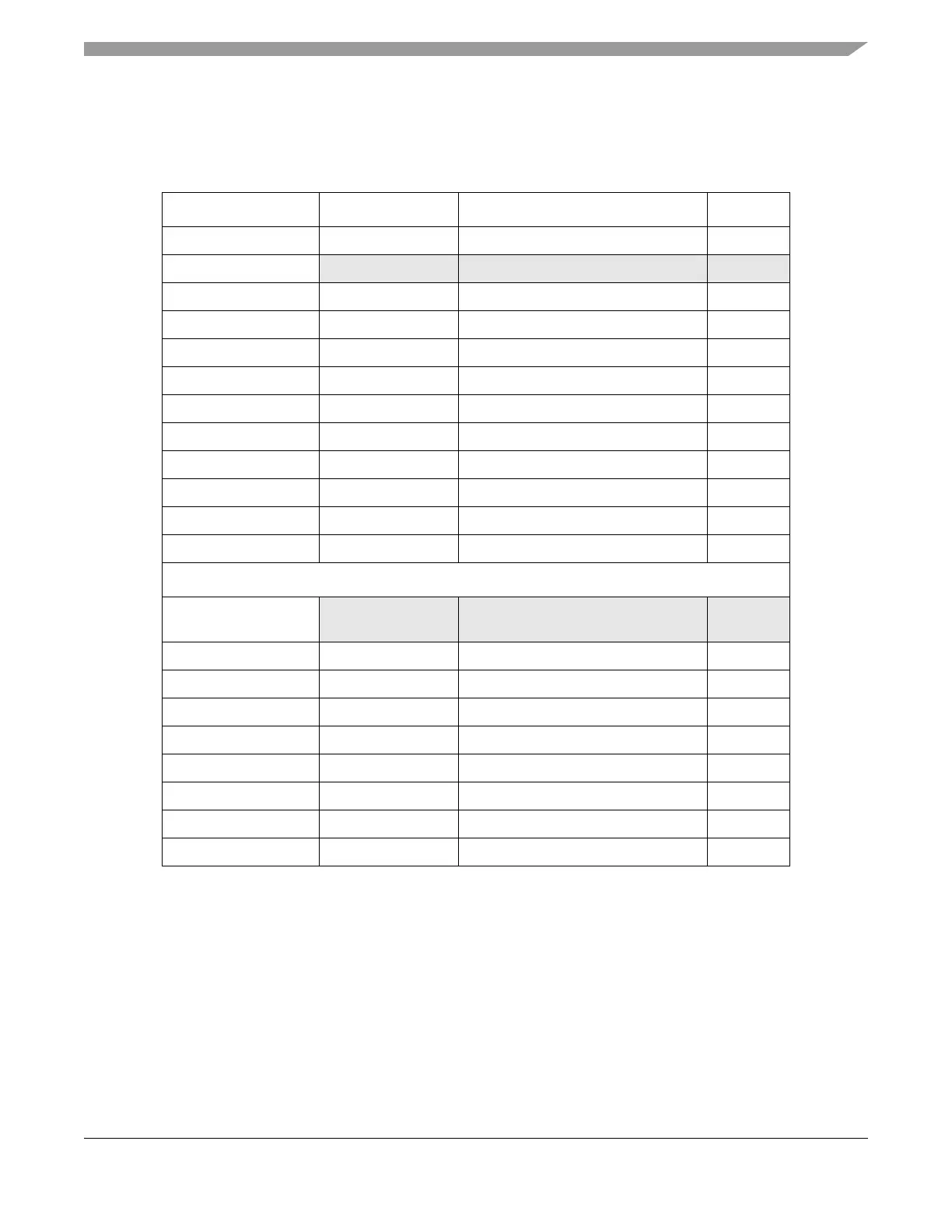

Table 12-6 is a memory map of the EBI registers.

12.3.1 Register Descriptions

12.3.1.1 Writing EBI Registers While a Transaction is in Progress

Other than the exceptions noted below, EBI registers must not be written while a transaction to the EBI

(from internal or external master) is in progress (or within 2 CLKOUT cycles after a transaction has just

completed, to allow internal state machines to go IDLE). In such cases, the behavior is undefined.

Exceptions that can be written while an EBI transaction is in progress are the following:

• All bits in EBI_TESR

Table 12-6. EBI Memory Map

Address Register Name Register Description Size (bits)

Base (0xC3F8_4000) EBI_MCR EBI module configuration register 32

Base + 0x0004

— Reserved —

Base + 0x0008 EBI_TESR EBI transfer error status register 32

Base + 0x000C EBI_BMCR EBI bus monitor control register 32

Base + 0x0010 EBI_BR0 EBI base register bank 0 32

Base + 0x0014 EBI_OR0 EBI option register bank 0 32

Base + 0x0018 EBI_BR1 EBI base register bank 1 32

Base + 0x001C EBI_OR1 EBI option register bank 1 32

Base + 0x0020 EBI_BR2 EBI base register bank 2 32

Base + 0x0024 EBI_OR2 EBI option register bank 2 32

Base + 0x0028 EBI_BR3 EBI base register bank 3 32

Base + 0x002C EBI_OR3 EBI option register bank 3 32

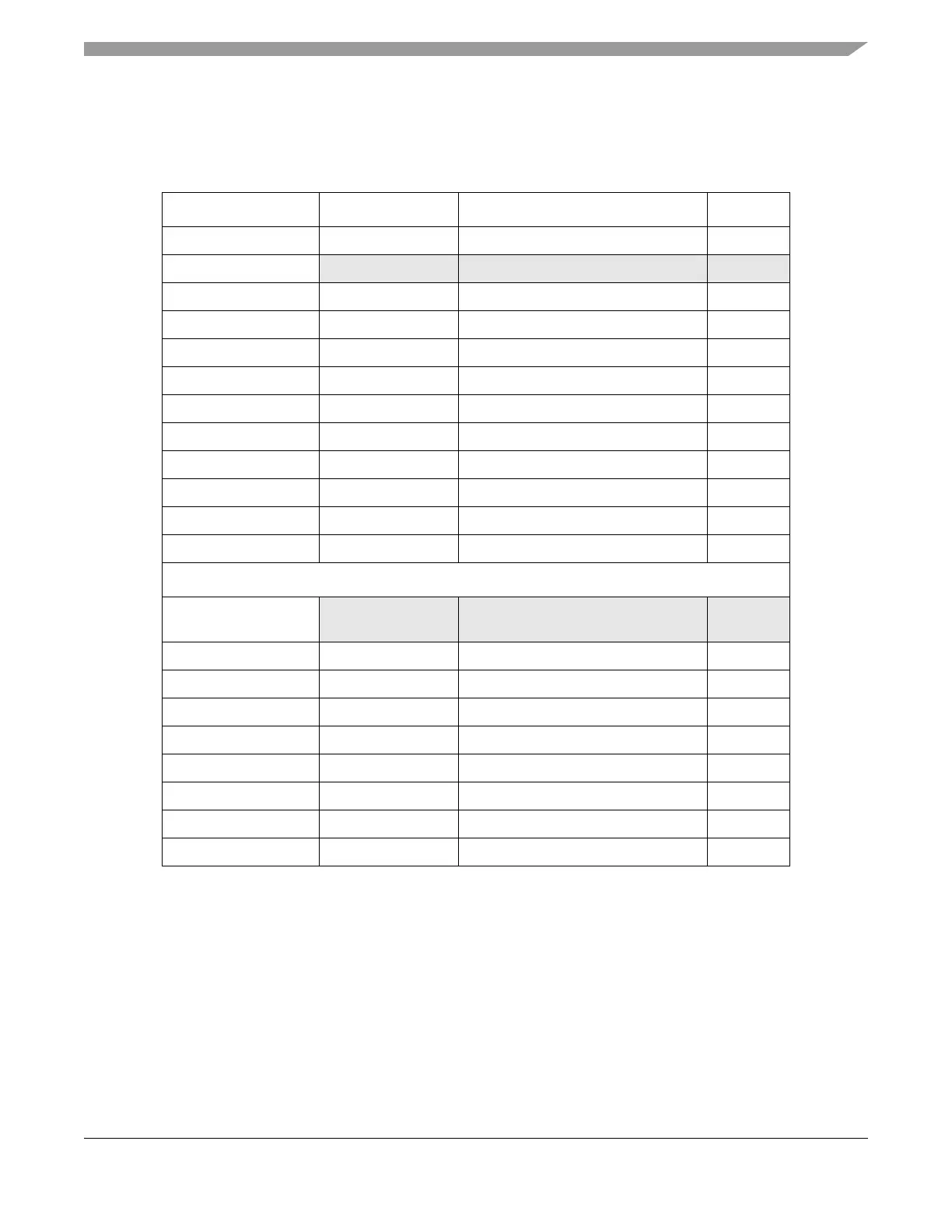

MPC5553-Only Calibration Registers:

Base + 0x30 -

Base + 0x3C

— Reserved —

Base + 0x0040 EBI_CAL_BR0 EBI Calibration Base Register Bank 0 32

Base + 0x0044 EBI_CAL_OR0 EBI Calibration Option Register Bank 0 32

Base + 0x0048 EBI_CAL_BR1 EBI Calibration Base Register Bank 1 32

Base + 0x004C EBI_CAL_OR1 EBI Calibration Option Register Bank 1 32

Base + 0x0050 EBI_CAL_BR2 EBI Calibration Base Register Bank 2 32

Base + 0x0054 EBI_CAL_OR2 EBI Calibration Option Register Bank 2 32

Base + 0x0058 EBI_CAL_BR3 EBI Calibration Base Register Bank 3 32

Base + 0x005C EBI_CAL_OR3 EBI Calibration Option Register Bank 3 32

Loading...

Loading...