MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 12-11

12.2.1.15 Transfer Size 0–1 (TSIZ[0:1]) — MPC5554 Only

TSIZ[0:1] indicates the size of the requested data transfer.

TSIZ[0:1] is driven by the EBI or an external master depending on who owns the external bus. The

TSIZ[0:1] signals may be used with ADDR[30:31] to determine which byte lanes of the data bus are

involved in the transfer. For non-burst transfers, the TSIZ[0:1] signals specify the number of bytes starting

from the byte location addressed by ADDR[30:31]. In burst transfers, the value of TSIZ[0:1] is always 00.

If the SIZEN bit in the EBI_MCR is 1, then TSIZ[0:1] is ignored by the EBI as an input for external master

transactions and the size is instead determined by the SIZE field in the EBI_MCR. The SIZEN bit has no

effect on the EBI when it is mastering a transaction on the external bus. TSIZ[0:1] is still driven

appropriately by the EBI and may or may not be used by the external master depending on the SIZEN

setting for the external master’s EBI. See Section 12.3.1.3, “EBI Module Configuration Register

(EBI_MCR).”

Note that in the MPC5553, the EBI_MCR[SIZEN] bit must be set to 1 in order to run external master

accesses to the MPC5553.

12.2.1.16 Write/Byte Enables (WE / BE)

Write enables are used to enable program operations to a particular memory. These signals can also be used

as byte enables for read and write operation by setting the WEBS bit in the appropriate base register. WE

/ BE are only asserted for chip select accesses.

WE

/ BE are driven by the EBI or an external master depending on who owns the external bus. See

Section 12.4.1.13, “Four Write/Byte Enable (WE/BE) Signals — Only MPC5554 and 416 BGA of

MPC5553” for more details on WE / BE functionality.

The MPC5554 and the 416 BGA package of the MPC5553 use WE[0:3]/ BE[0:3]. The 324 BGA of the

MPC5553 uses only WE[0:1]/ BE[0:1]. The 208 BGA of the MPC5553 has no write/byte enable signals.

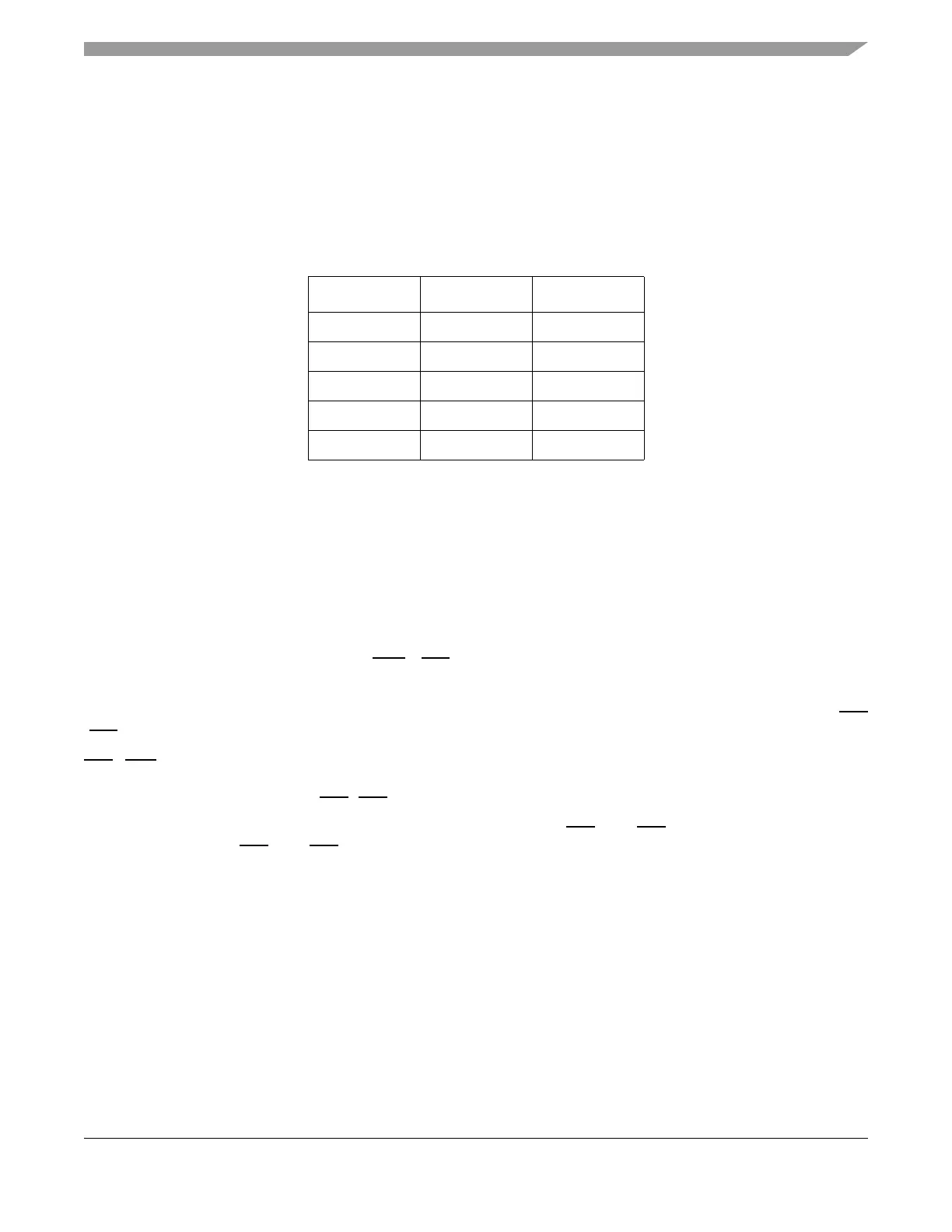

12.2.2 Signal Function/Direction by Mode

Depending on the mode of operation, some or all of the EBI external signals may not be used by the EBI.

When a signal is configured for non-EBI function in the EBI_MCR, the EBI always negates the signal if

the EBI controls the corresponding pad (determined by SIU configuration). Table 12-5 lists the function

and direction of the external signals in each of the EBI modes of operation. The clock signals are not

included because they are output only (from the FMPLL module) and are not affected by EBI modes. See

Section 12.3.1.3, “EBI Module Configuration Register (EBI_MCR)” for details on the EXTM and MDIS

bits.

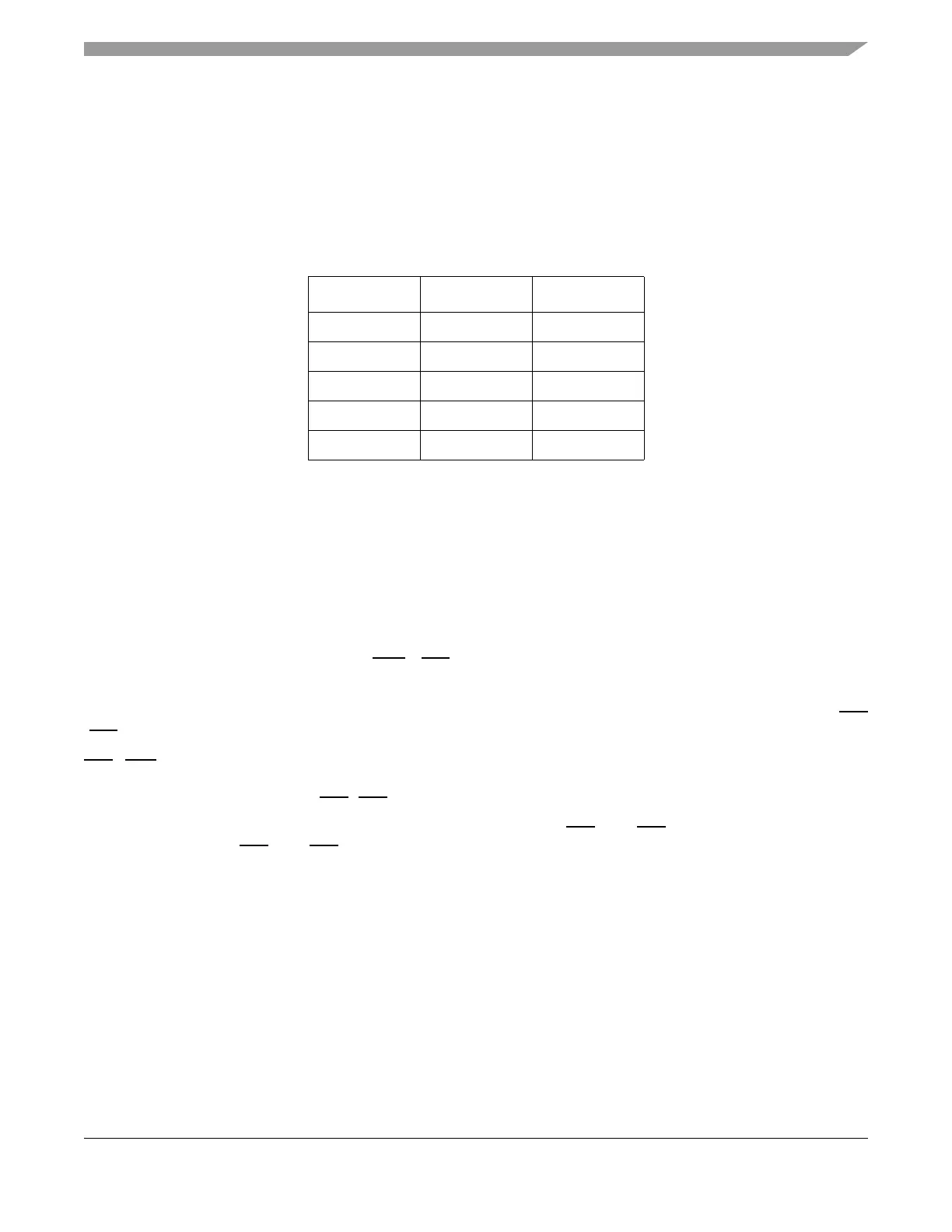

Table 12-4. TSIZ[0:1] Encoding

Burst Cycle TSIZ[0:1] Transfer Size

N 01 Byte

N 10 16-bit

N 11 Reserved

N 00 32-bit

Y00Burst

Loading...

Loading...