MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

25-72 Freescale Semiconductor

• Data trace via data write messaging (DWM) and data read messaging (DRM). This provides the

capability for the development tool to trace reads and/or writes through the eDMA module to

(selected) internal memory resources.

• Watchpoint messaging via the auxiliary pins.

• Watchpoint trigger enable of data trace messaging (DTM).

• Registers for data trace, watchpoint generation, and watchpoint trigger.

• All features controllable and configurable via the JTAG port.

• Power management.

— Low power design

— Dynamic power management of FIFOs and control logic

25.13 External Signal Description

The NXDM module uses the same pins and pin protocol as defined in Section 25.2.

25.13.1 Rules for Output Messages

The NXDM module observes the same rules for output messages as the NPC. See Section 25.7.2.2.1,

“Rules of Messages.”

25.13.2 Auxiliary Port Arbitration

The NXDM module arbitrates for the shared Nexus port. This arbitration is handled by the NPC (See

Section 25.5) based on prioritized requests from the NXDM and the other Nexus clients sharing the port.

25.14 NXDM Programmers Model

This section describes the NXDM programmers model. Nexus registers are accessed using the JTAG port

in compliance with IEEE 1149.1. See Chapter 24, “IEEE 1149.1 Test Access Port Controller (JTAGC)”

and Section 25.7.2.3 for details on Nexus register access.

25.14.1 NXDM Nexus Register Map

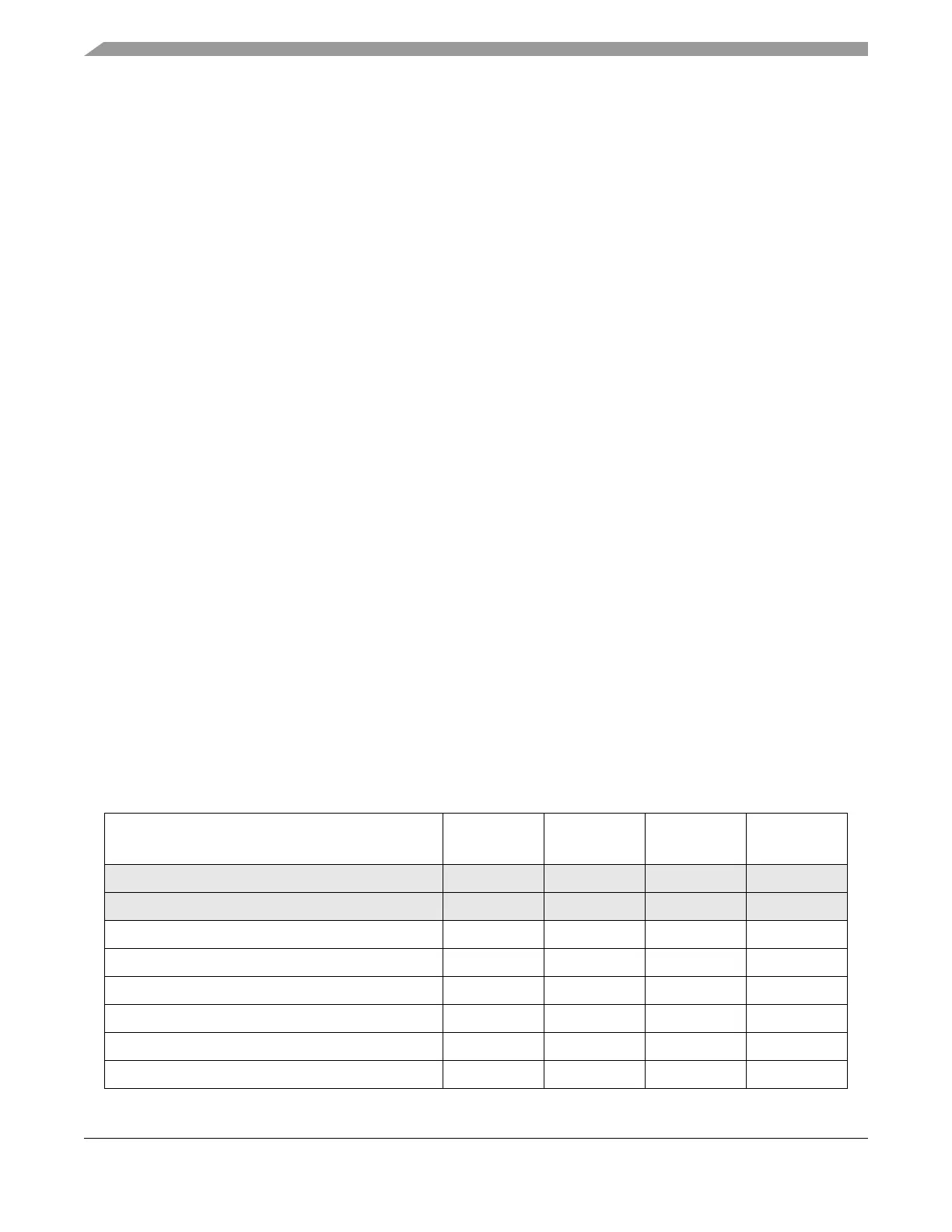

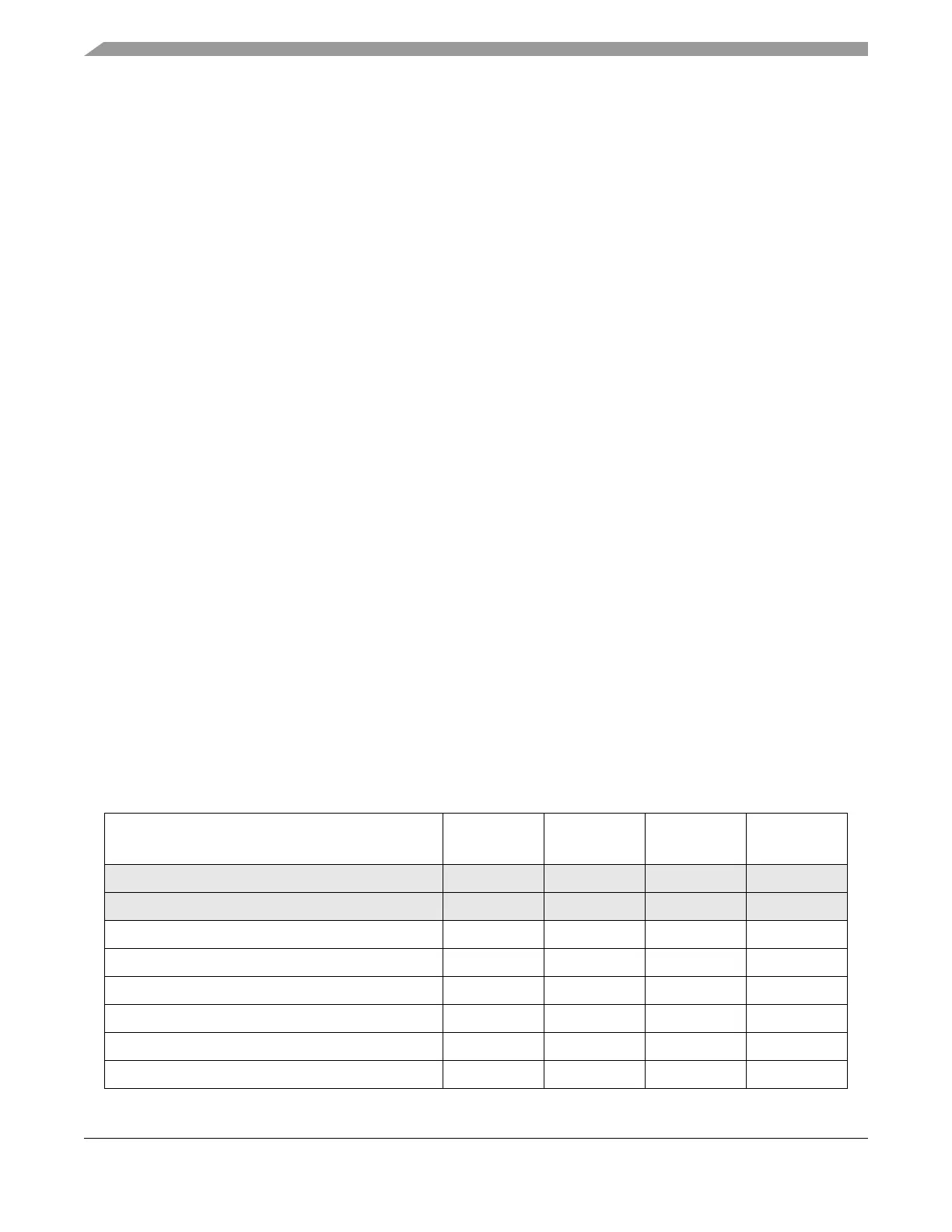

Table 25-45. NXDM Register Map

Nexus Register

Nexus Access

Opcode

Read/Write

Read

Address

Write

Address

Client Select Control (CSC)

1

0x1 R 0x02 –

Port Configuration Register (PCR)

1

See NPC R/W – –

Development Control 1 (DC1) 0x2 R/W 0x04 0x05

Development Control 2 (DC2) 0x3 R/W 0x05 0x06

Watchpoint Trigger (WT) 0xB R/W 0x16 0x17

Data Trace Control (DTC) 0xD R/W 0x1A 0x1B

Data Trace Start Address 1 (DTSA1) 0xE R/W 0x1C 0x1D

Data Trace Start Address 2 (DTSA2) 0xF R/W 0x1E 0x1F

Loading...

Loading...