MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

A-2 Freescale Semiconductor

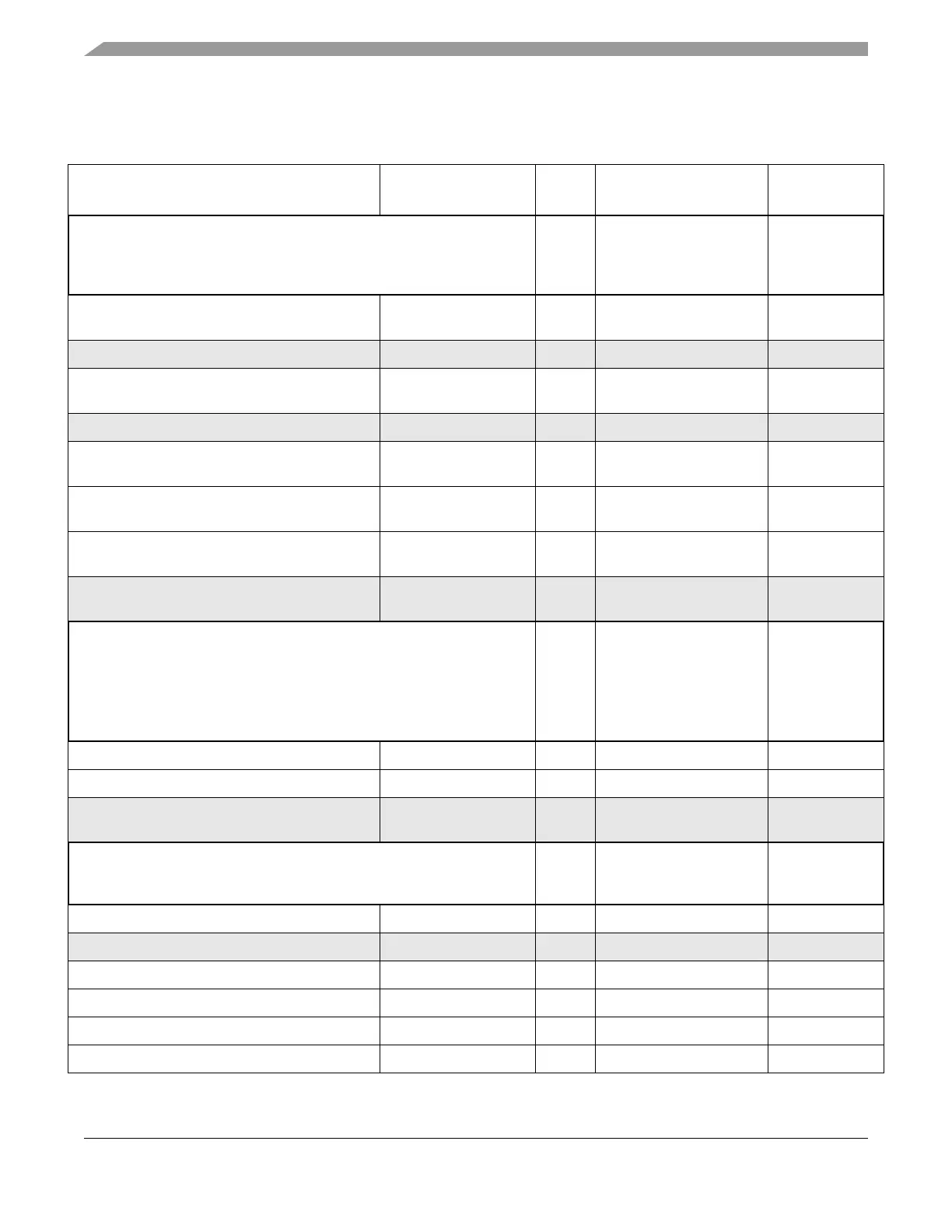

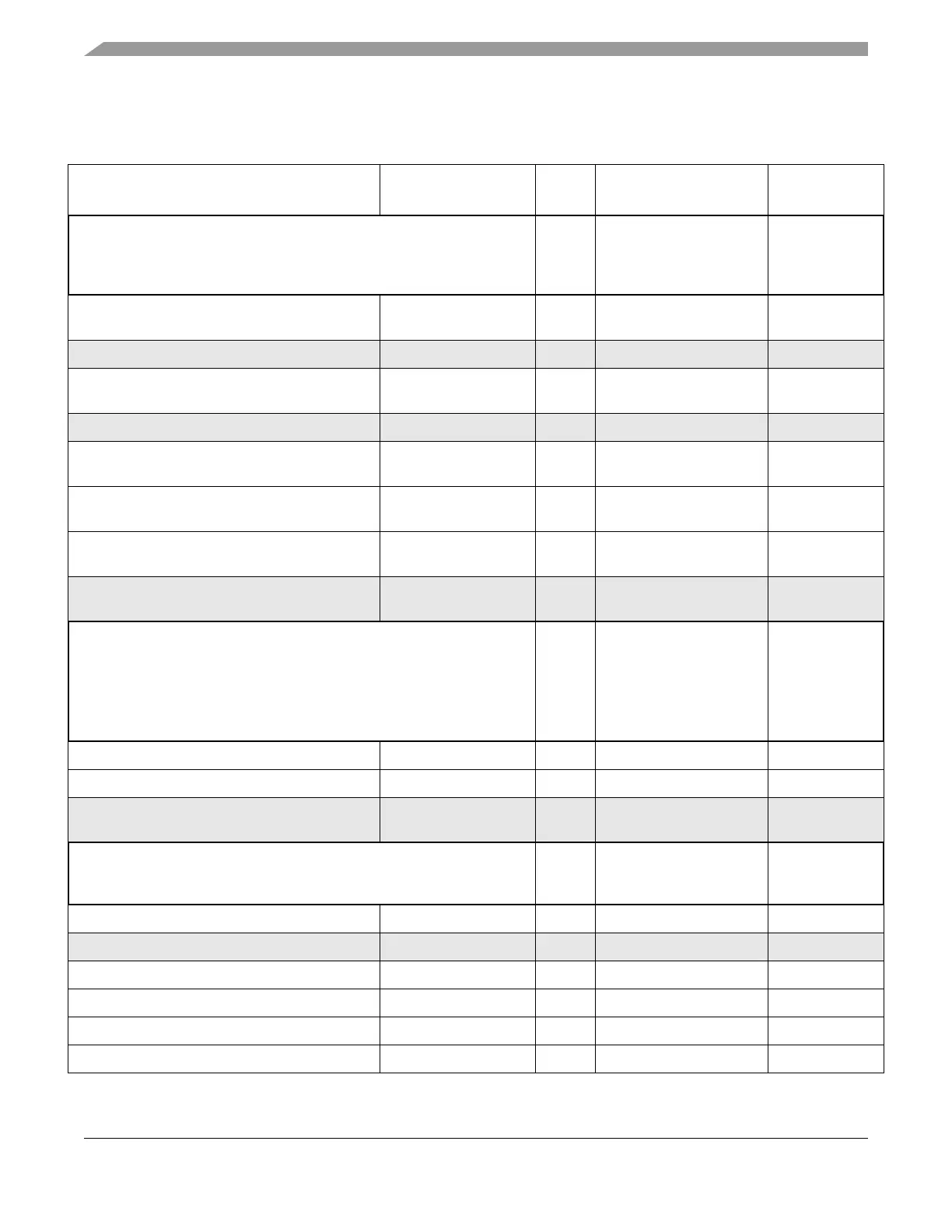

A.2 Detailed Register Map

Table A-2. MPC5554 / MPC5553 Detailed Register Map

Register Description Register Name

Used

Size

Address Reference

Peripheral Bridge A (PBRIDGE_A)

0xC3F0_0000 Chapter 5,

“Peripheral Bridge

(PBRIDGE_A,

PBRIDGE_B)”

Peripheral bridge A master privilege control

register

PBRIDGE_A_MPCR 32-bit Base + 0x0000

Reserved — — Base + (0x0004-0x001F)

Peripheral bridge A peripheral access control

register 0

PBRIDGE_A_PACR0 32-bit Base + 0x0020

Reserved — — Base + (0x0024-0x003F)

Peripheral bridge A off-platform peripheral access

control register 0

PBRIDGE_A_OPACR0 32-bit Base + 0x0040

Peripheral bridge A off-platform peripheral access

control register 1

PBRIDGE_A_OPACR1 32-bit Base + 0x0044

Peripheral bridge A off-platform peripheral access

control register 2

PBRIDGE_A_OPACR2 32-bit Base + 0x0048

Reserved — — Base + (0x004C-

0xC3F7_FFFF)

Frequency Modulated Phase-Locked Loop (FMPLL)

0xC3F8_0000

Chapter 11,

“Frequency

Modulated Phase

Locked Loop

(FMPLL) and

System Clocks”

Synthesizer control register FMPLL_SYNCR 32-bit Base + 0x0000

Synthesizer status register FMPLL_SYNSR 32-bit Base + 0x0004

Reserved — — (Base + 0x0008)-

0xC3F8_3FFF

External Bus Interface (EBI)

0xC3F8_4000 Chapter 12,

“External Bus

Interface (EBI)”

Module configuration register EBI_MCR 32-bit Base + 0x0000

Reserved — — Base + (0x0004-0x0007)

Transfer error status register EBI_TESR 32-bit Base + 0x0008

Bus monitor control register EBI_BMCR 32-bit Base + 0x000C

Base register bank 0 EBI_BR0 32-bit Base + 0x0010

Option register bank 0 EBI_OR0 32-bit Base + 0x0014

Loading...

Loading...