MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 19-99

19.4.8 eQADC Synchronous Serial Interface (SSI) Submodule

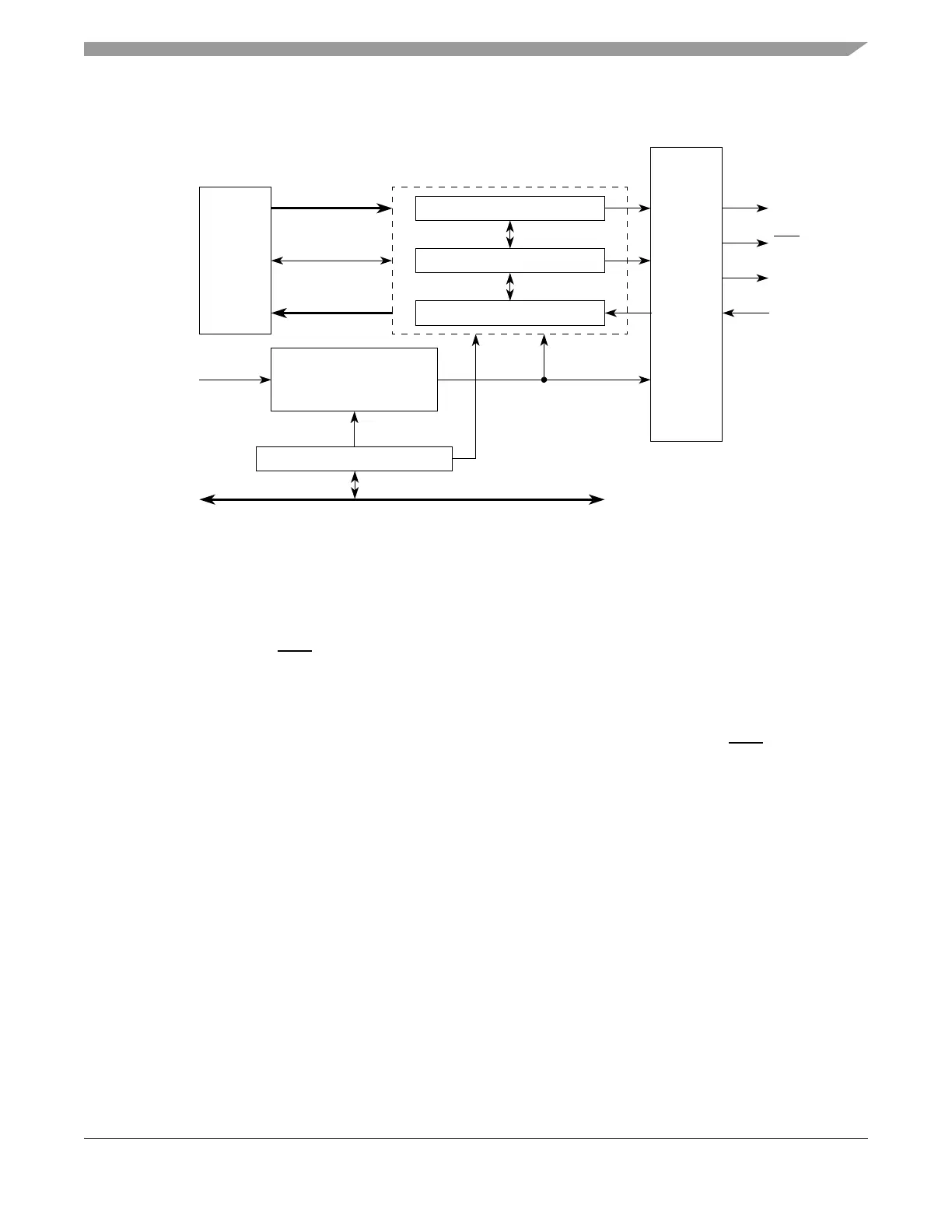

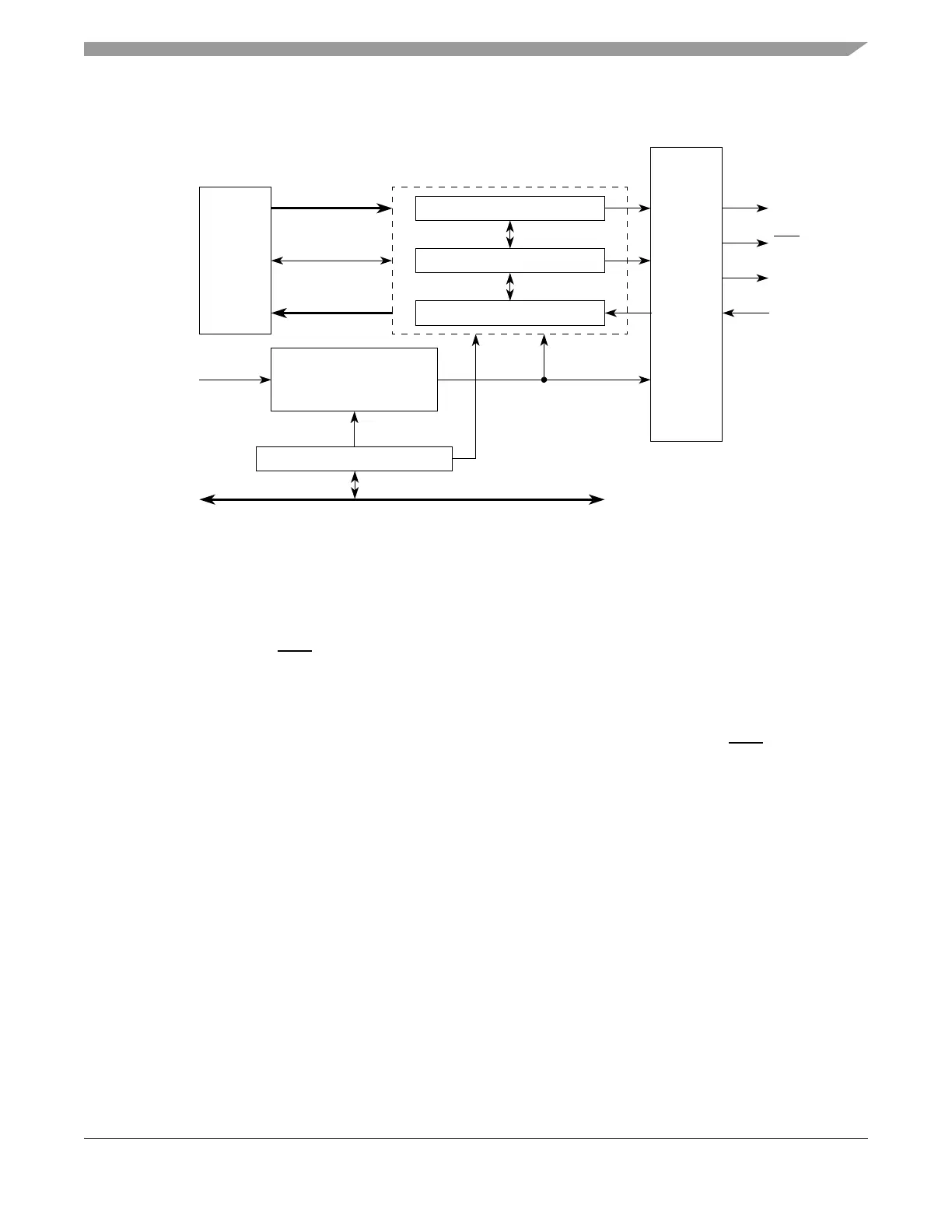

Figure 19-55. eQADC Synchronous Serial Interface Block Diagram

The eQADC SSI protocol allows for a full duplex, synchronous, serial communication between the

eQADC and a single external device. Figure 19-55 shows the different components inside the eQADC SSI.

The eQADC SSI submodule on the eQADC is always configured as a master. The eQADC SSI has four

associated port pins:

• Free running clock (FCK)

• Serial data select (SDS)

• Serial data in (SDI)

• Serial data out (SDO)

The FCK clock signal times the shifting and sampling of the two serial data signals and it is free running

between transmissions, allowing it to be used as the clock for the external device. The SDS signal will be

asserted to indicate the start of a transmission, and negated to indicate the end or the abort of a

transmission. SDI is the master serial data input and SDO the master serial data output.

The eQADC SSI submodule is enabled by setting the EQADC_MCR[ESSIE] (see Section 19.3.2.1).

When enabled, the eQADC SSI can be optionally capable of starting serial transmissions. When serial

transmissions are disabled (ESSIE set to 0b10), no data will be transmitted to the external device but FCK

will be free-running. This operation mode permits the control of the timing of the first serial transmission,

and can be used to avoid the transmission of data to an unstable external device, for example, a device that

is not fully reset. This mode of operation is specially important for the reset procedure of an external device

that uses the FCK as its main clock.

The main elements of the eQADC SSI are the shift registers. The 26-bit transmit shift register in the master

and 26-bit receive shift register in the slave are linked by the SDO pin. In a similar way, the 26-bit transmit

shift register in the slave and 26-bit receive shift register in the master are linked by the SDI pin. See

Figure 19-56. When a data transmission operation is performed, data in the transmit registers is serially

shifted twenty-six bit positions into the receive registers by the FCK clock from the master; data is

exchanged between the master and the slave. Data in the master transmit shift register in the beginning of

Transmit Shift Register

System

Clock

eQADC SSI Control Logic

Receive Shift Register

Pad

Interface

Master

Out

Slave

In

SDO

SDS

FCK

SDI

CFIFO Data

Control

RFIFO Data

Baud Clock Generator

Divide by:

2, 3, 4, ..., 15, 16, 17

FCK Clock

eQADC SSI Control Register

BR MDT

External Bus Interface

eQADC

FIFO

Control

Unit

Loading...

Loading...