MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 25-43

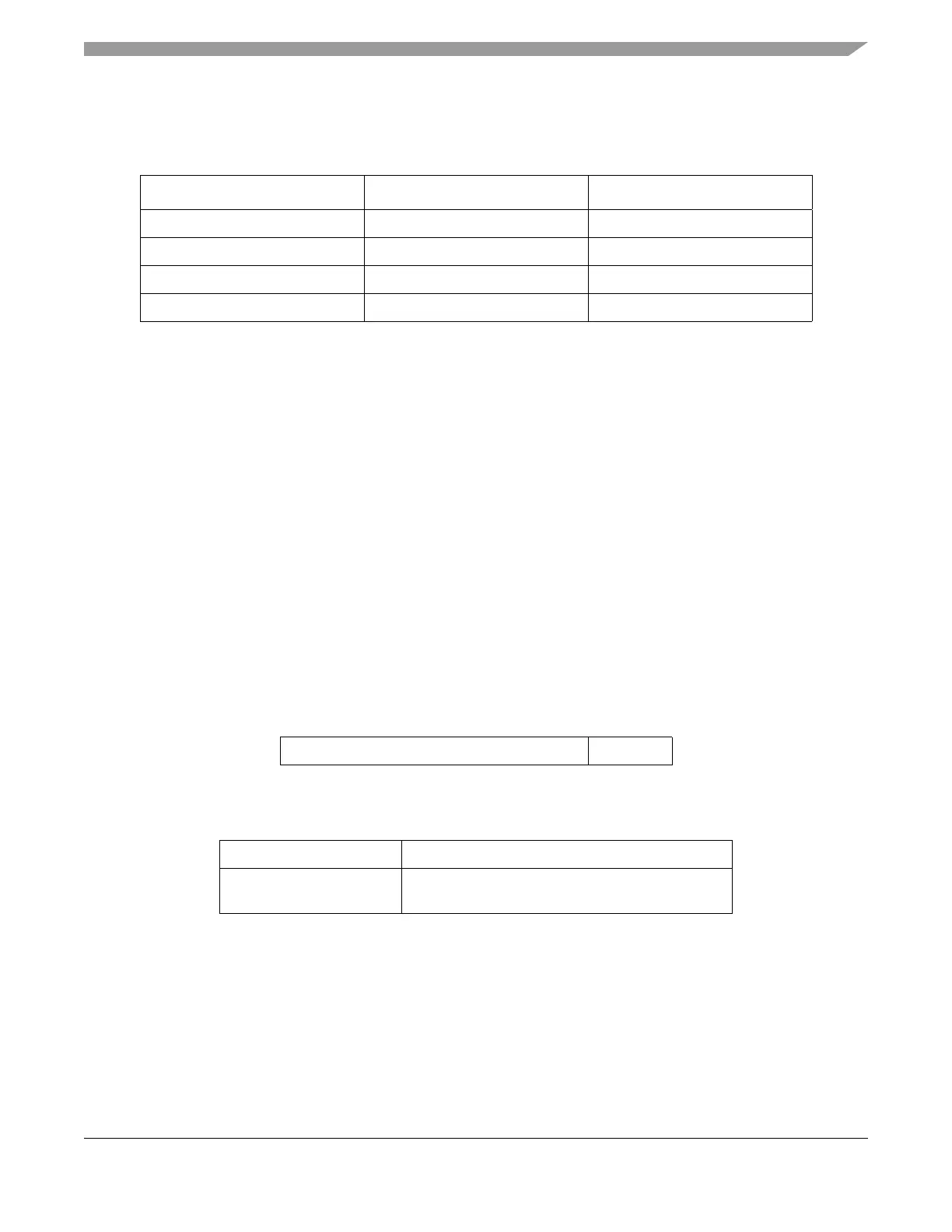

Table 25-32 illustrates the range that will be selected for data trace for various cases of DTSA being less

than, greater than, or equal to DTEA.

NOTE

DTSA must be less than DTEA in order to guarantee correct data write/read

traces. Data trace ranges are exclusive of the DTSA and DTEA addresses.

25.11.10 NZ6C3 Register Access via JTAG / OnCE

Access to Nexus3 register resources is enabled by loading a single instruction

(ACCESS_AUX_TAP_ONCE) into the JTAGC instruction register (IR), and then loading the

corresponding OnCE OCMD register with the NEXUS3_ACCESS instruction (refer to Table 25-5). For

the NZ6C3 module, the OCMD value is 0b00_0111_1100.

After the ACCESS_AUX_TAP_ONCE instruction has been loaded, the JTAG/OnCE port allows

tool/target communications with all Nexus3 registers according to the register map in Table 25-24.

Reading/writing of a NZ6C3 register then requires two (2) passes through the data-scan (DR) path of the

JTAG state machine (see Section 25.11.17).

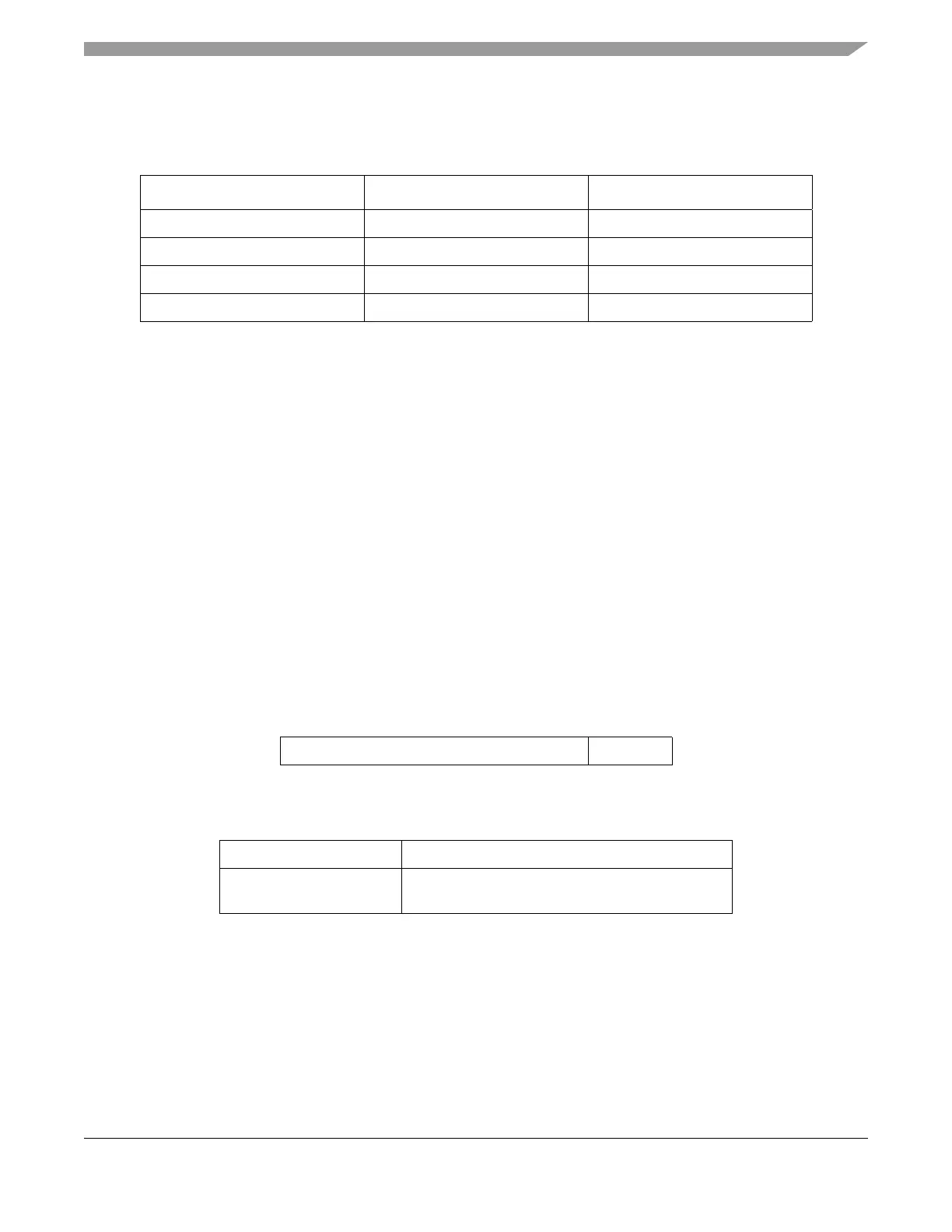

1. The first pass through the DR selects the NZ6C3 register to be accessed by providing an index (see

Table 25-24), and the direction (read/write). This is achieved by loading an 8-bit value into the

JTAG data register (DR). This register has the following format:

2. The second pass through the DR then shifts the data in or out of the JTAG port, lsb first.

a) During a read access, data is latched from the selected Nexus register when the JTAG state

machine passes through the capture-DR state.

b) During a write access, data is latched into the selected Nexus register when the JTAG state

machine passes through the update-DR state.

Table 25-32. Data Trace—Address Range Options

Programmed Values Range Control Bit Value Range Selected

DTSA < DTEA 0 DTSA -> <- DTEA

DTSA < DTEA 1 <- DTSA DTEA ->

DTSA > DTEA N/A Invalid range—no trace

DTSA = DTEA N/A Invalid range—no trace

Nexus Register Index: Selected from values in Table 25-24

Read/Write (R/W): 0 Read

1Write

Nexus Register Index

(7-bits) (1-bit)

R/W

RESET Value: 0x00

Loading...

Loading...