MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

15-4 Freescale Semiconductor

15.6.2 Reset Operation

When a reset event asserts while an access to system memory is in progress, the access either completes

successfully, or does not occur, depending on the cycle at which the reset occurs. Any data stored during

such an access becomes the intended data, and no other address locations are accessed or changed. If the

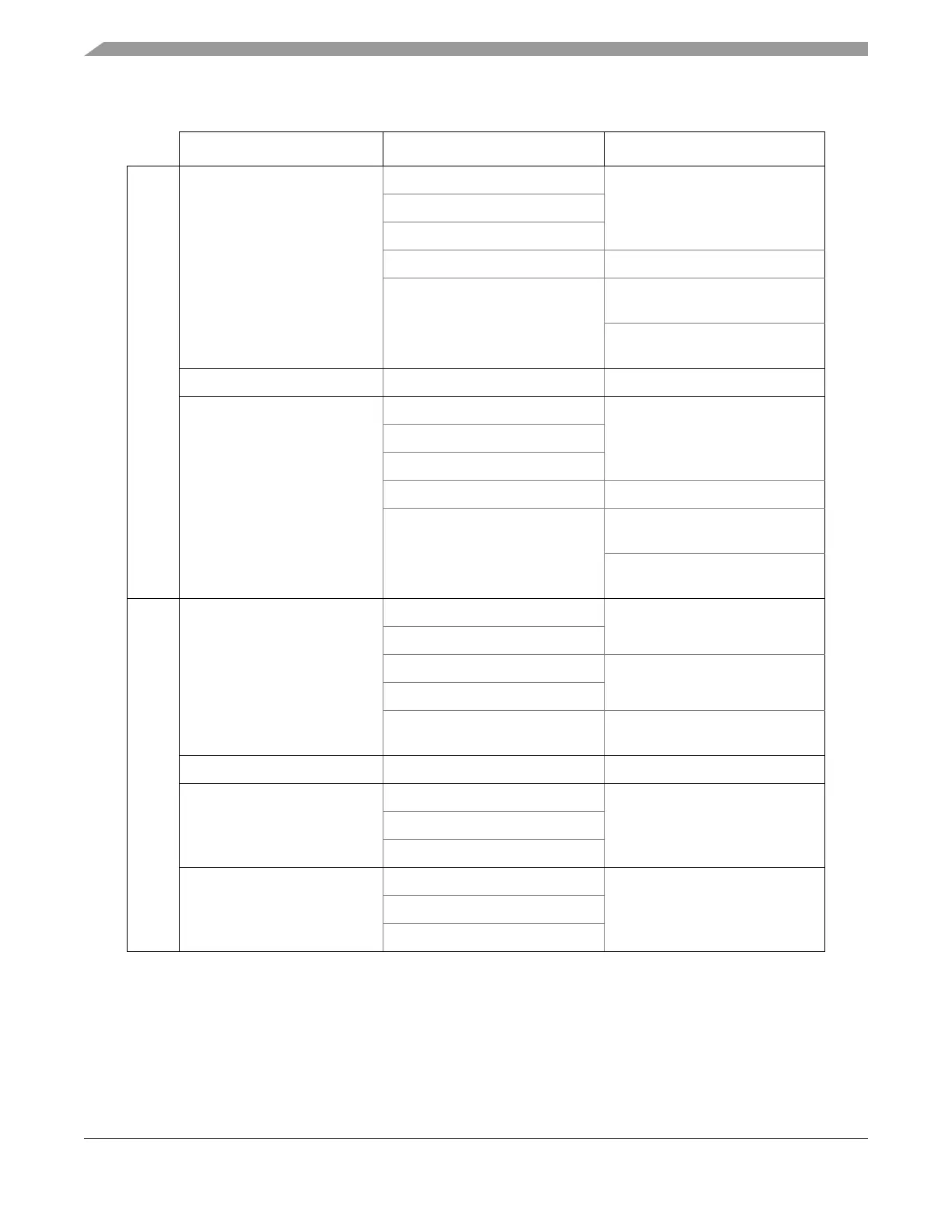

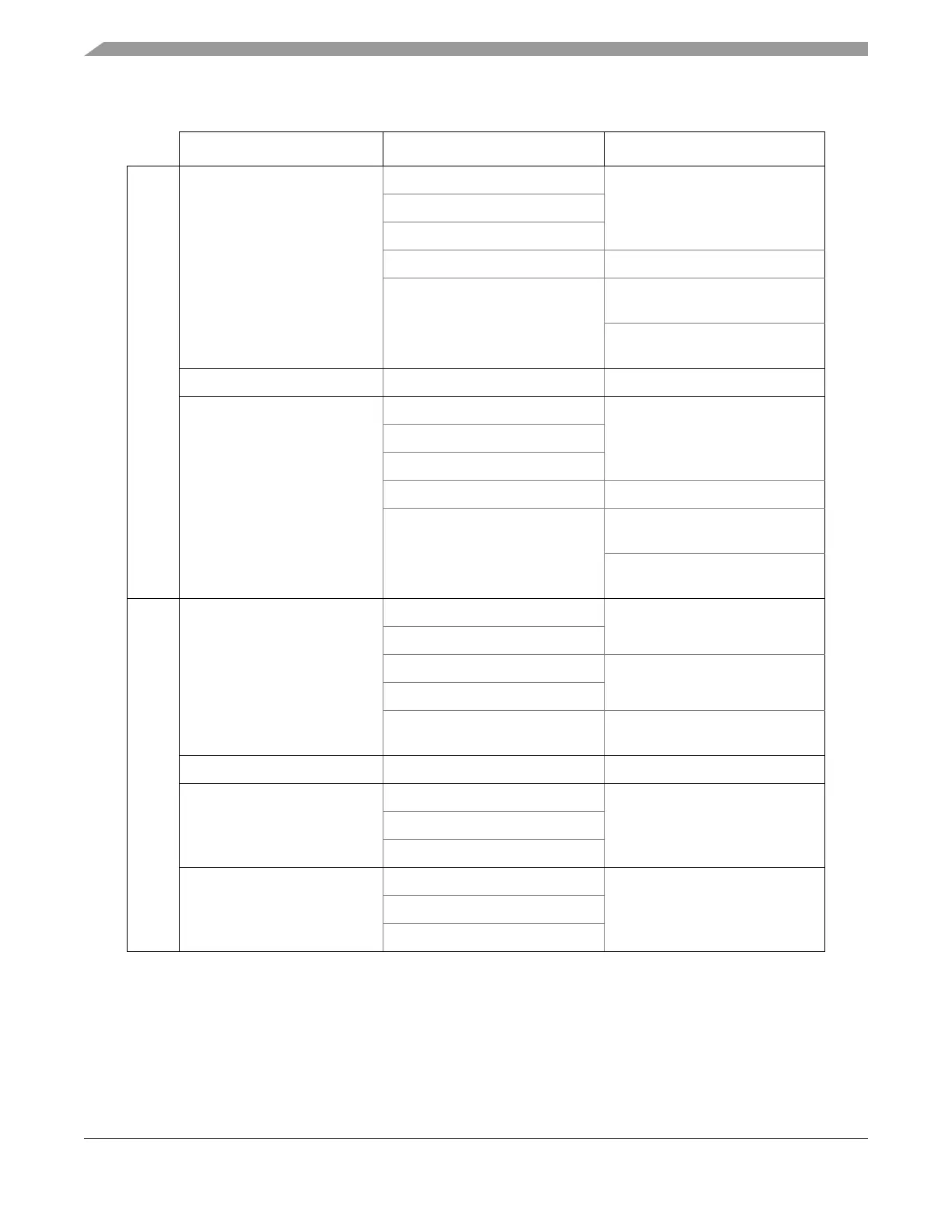

Table 15-2. Wait States During SRAM Accesses

Current Access Operation Previous Access Operation Number of Wait States Used

Read Operation

Read

Idle

1Pipelined Read

Burst Read

64-bit Write 2

8/16/32-bit Write

0

(read from the same address)

1

(read from a different address)

Pipelined Read Read 0

Burst Read

idle

1,0,0,0Pipelined Read

Burst Read

64-bit Write 2,0,0,0

8/16/32-bit Write

0,0,0,0

(read from the same address)

1,0,0,0

(read from a different address)

Write Operation

8/16/32-bit Write

idle

1

Read

Pipelined 8/16/32-bit write

2

64-bit write

8/16/32-bit write

0

(write to the same address)

Pipelined 8/16/32-bit Write 8/16/32-bit Write 0

64-bit Write

idle

064-bit Write

Read

64-bit Burst Write

idle

0,0,0,064-bit Write

Read

Loading...

Loading...