MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 21-33

21.4.9 Interrupt Operation

21.4.9.1 Interrupt Sources

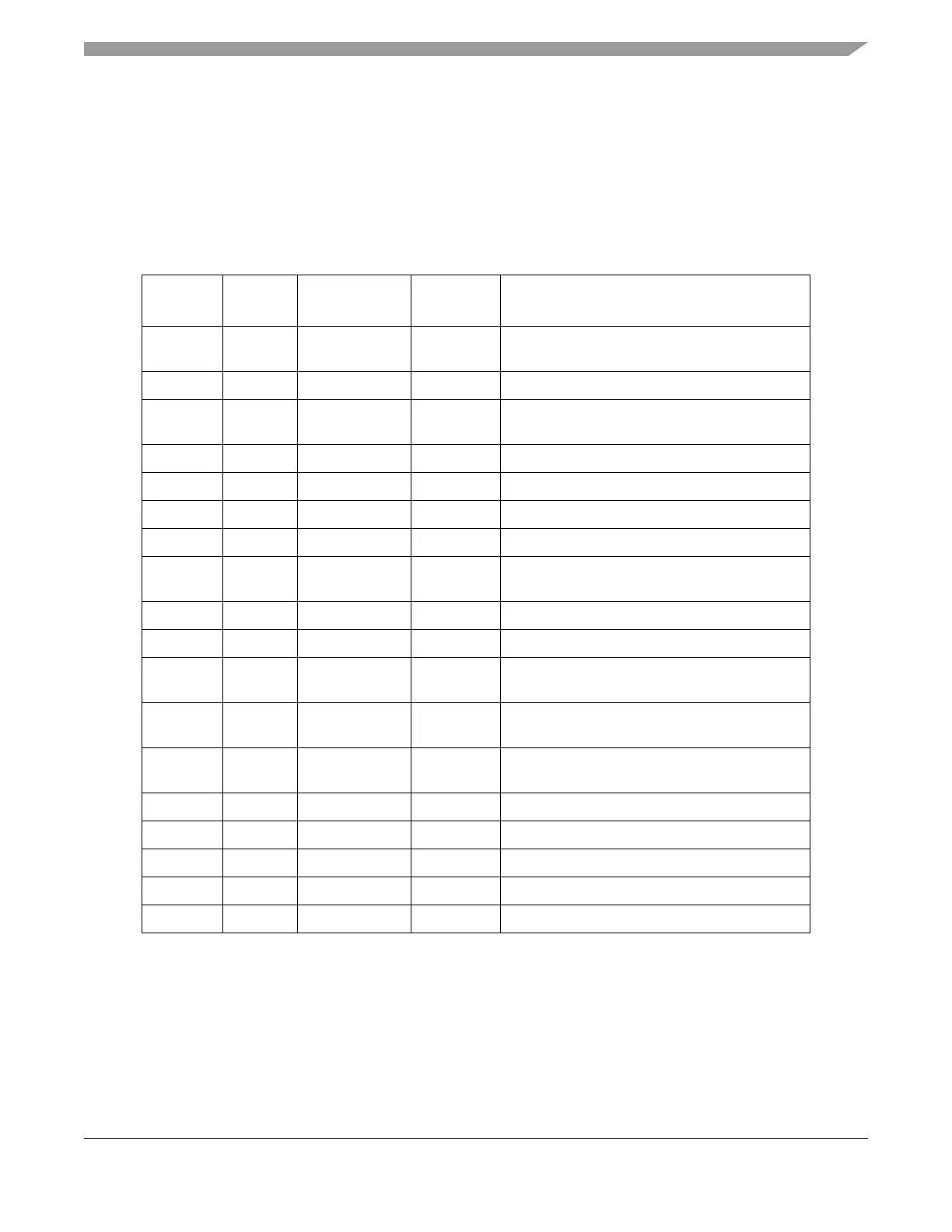

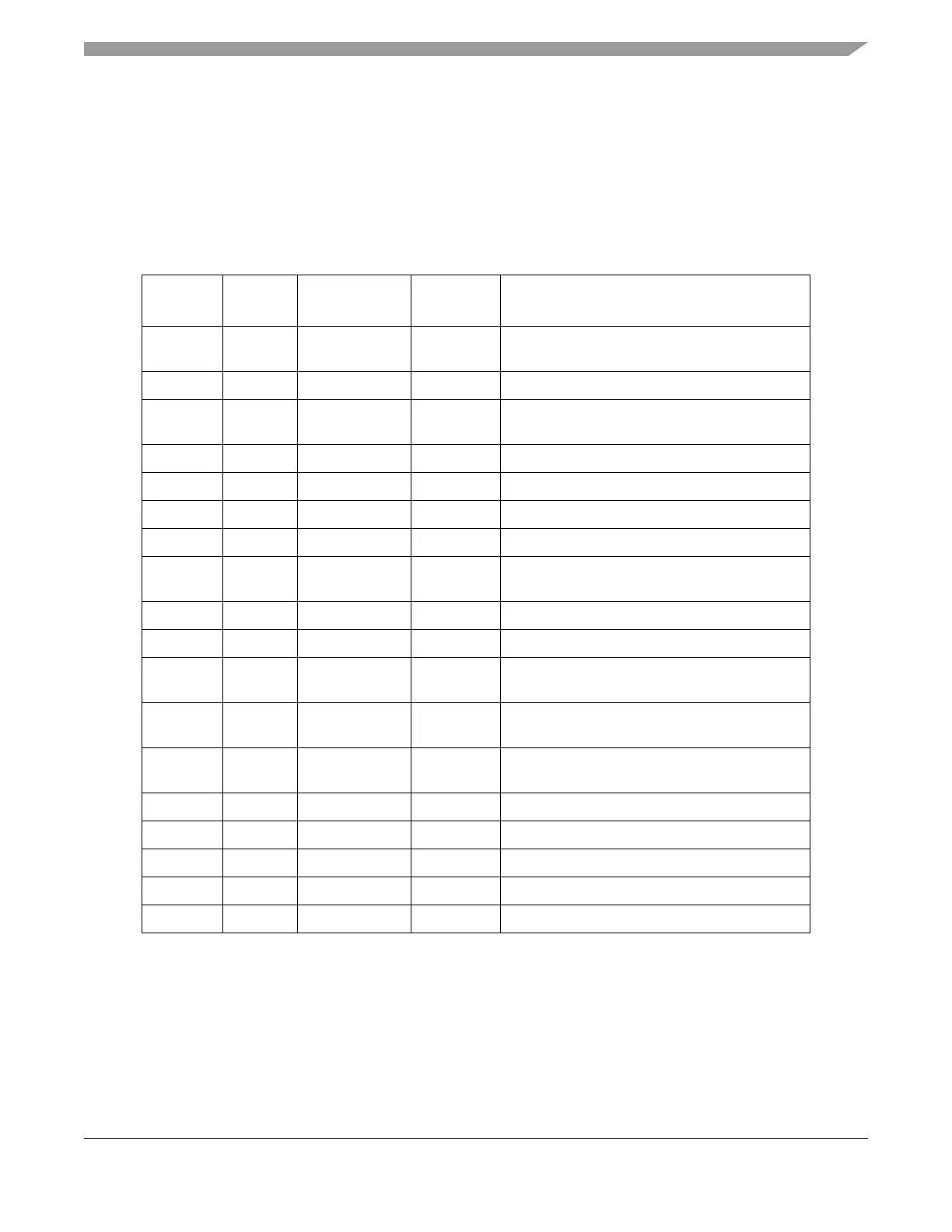

There are several interrupt sources that can generate an eSCI interrupt to the CPU. They are listed with

details and descriptions in Table 21-21.

The eSCI only originates interrupt requests. The following sections describe how the eSCI generates a

request and how the MCU acknowledges that request. The eSCI only has a single interrupt line (eSCI

interrupt signal, active high operation) and all the following interrupts, when generated, are ORed together

and issued through that port.

Table 21-21. eSCI Interrupt Flags, Sources, Mask Bits, and Descriptions

Interrupt

Source

Flag Source

Local

Enable

Description

Transmitter TDRE ESCIx_SR[0] TIE Indicates that a byte was transferred from

ESCIx_DR to the transmit shift register.

Transmitter TC ESCIx_SR[1] TCIE Indicates that a transmit is complete.

Receiver RDRF ESCIx_SR[2] RIE Indicates that received data is available in the

eSCI data register.

Receiver IDLE ESCIx_SR[3] ILIE Indicates that receiver input has become idle.

Receiver OR ESCIx_SR[4] ORIE Indicates that an overrun condition has occurred.

Receiver NF ESCIx_SR[5] NFIE Detect noise error on receiver input.

Receiver FE ESCIx_SR[6] FEIE Framing error has occurred.

Receiver PF ESCIx_SR[7] PFIE Parity of received data does not match parity bit;

parity error has occurred.

LIN BERR ESCIx_SR[11] IEBERR Detected a bit error, only valid in LIN mode.

LIN RXRDY ESCIx_SR[16] RXIE Indicates LIN hardware has received a data byte.

LIN TXRDY ESCIx_SR[17] TXIE Indicates LIN hardware can accept a control or

data byte.

LIN LWAKE ESCIx_SR[18] WUIE A wake-up character has been received from a

LIN frame.

LIN STO ESCIx_SR[19] STIE The response of the slave has been too slow

(slave timeout).

LIN PBERR ESCIx_SR[20] PBIE Physical bus error detected.

LIN CERR ESCIx_SR[21] CIE CRC error detected.

LIN CKERR ESCIx_SR[22] CKIE Checksum error detected.

LIN FRC ESCIx_SR[23] FCIE LIN frame completed.

LIN OVFL ESCIx_SR[31] OFIE ESCIx_LRR overflow.

Loading...

Loading...