MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-15

18.4.2 Register Description

Table 18-6 shows the eTPU registers and their locations, without examples or explanation of how the fields

are used. For a complete description of these registers users should refer to the Enhanced Time Processing

Unit (eTPU) Reference Manual. The features are explained in detail there.

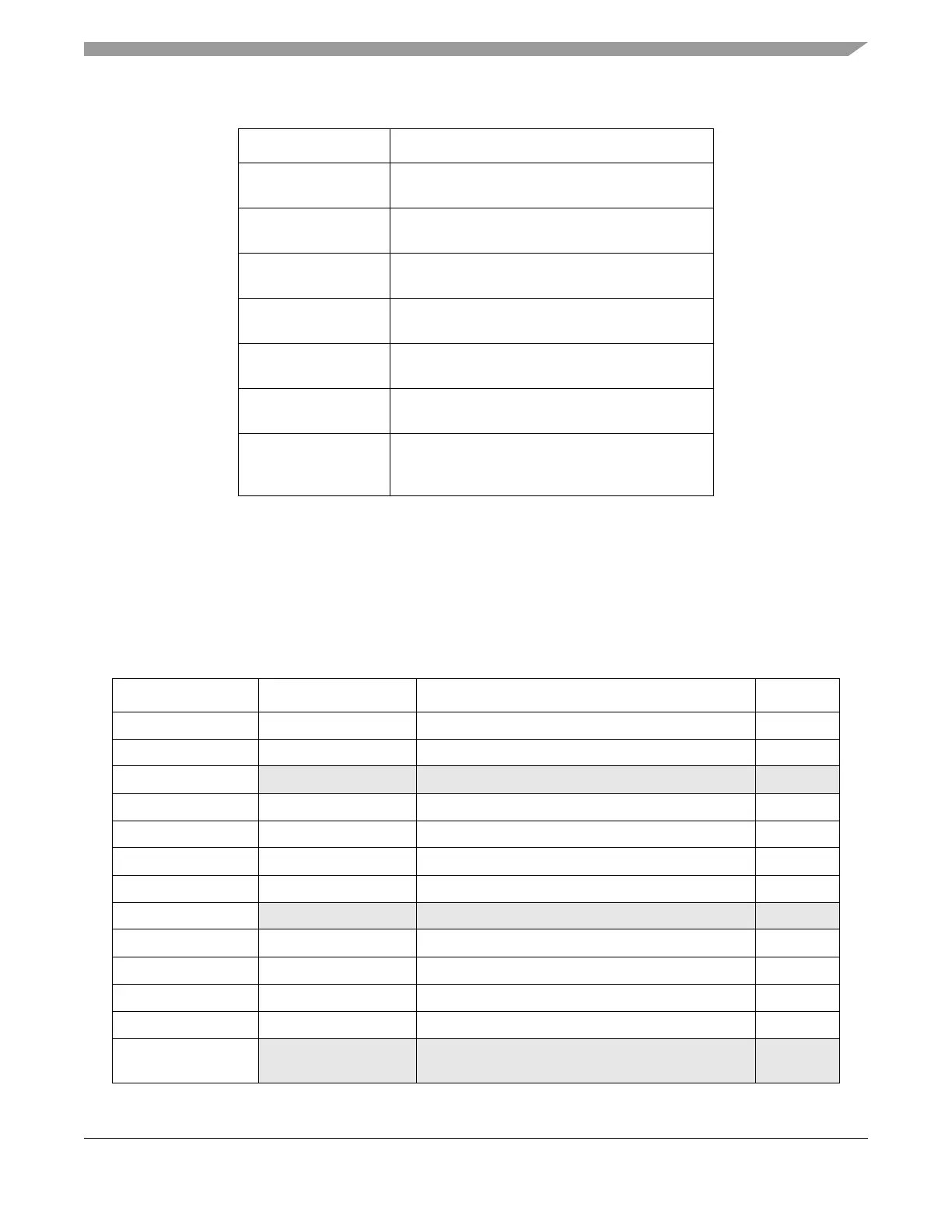

Base + 0x0_0C00–

Base + 0x0_7FFF

Reserved

Base + 0x0_8000–

Base + 0x0_8BFF

SDM (3 Kbytes)

Base + 0x0_8C00–

Base + 0x0_BFFF

Reserved

Base + 0x0_C000–

Base + 0x0_CBFF

SDM PSE mirror

1

(3 Kbytes)

Base + 0xCC00–

Base + 0xFFFF

Reserved

Base + 0x1_0000–

Base + 0x1_3FFF

SCM (16 Kbytes — MPC5554)

(12 Kbytes — MPC5553)

Base + 0x1_4000–

Base + 0x1_FFFF

Not writable

Reads the return value of ETPU_SCMOFFDATAR

register.

1

Parameter Sign Extension access area. See the eTPU reference manual.

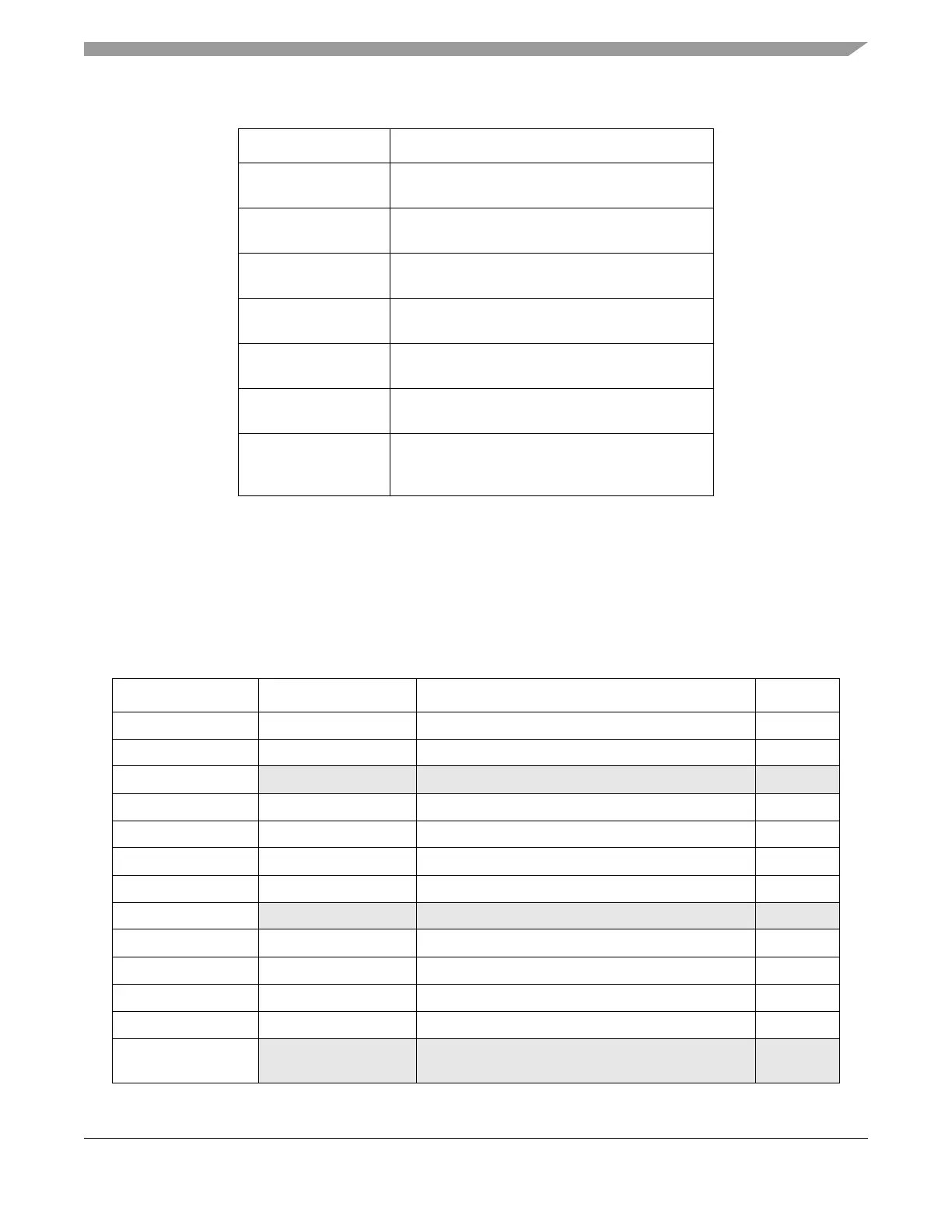

Table 18-6. Detailed Memory Map

Address Register Name Register Description Size (bits)

Base (0xC3FC_0000) ETPU_MCR eTPU module configuration register 32

Base + 0x0_0004 ETPU_CDCR eTPU coherent dual-parameter controller register 32

Base + 0x0_0008

— Reserved —

Base + 0x0_000C ETPU_MISCCMPR eTPU MISC compare register 32

Base + 0x0_0010 ETPU_SCMOFFDATAR eTPU SCM off-range data register 32

Base + 0x0_0014 ETPU_ECR_A eTPU A engine configuration register 32

Base + 0x0_0018 ETPU_ECR_B

1

eTPU B engine configuration register 32

Base + 0x0_001C

— Reserved —

Base + 0x0_0020 ETPU_TBCR_A eTPU A time base configuration register 32

Base + 0x0_0024 ETPU_TB1R_A eTPU A time base 1 32

Base + 0x0_0028 ETPU_TB2R_A eTPU A time base 2 32

Base + 0x0_002C ETPU_REDCR_A eTPU A STAC bus interface configuration register 32

Base + 0x0_0030–

Base + 0x0_003F

— Reserved —

Table 18-5. eTPU High-Level Memory Map (Continued)

Address Register Description

Loading...

Loading...