MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-16 Freescale Semiconductor

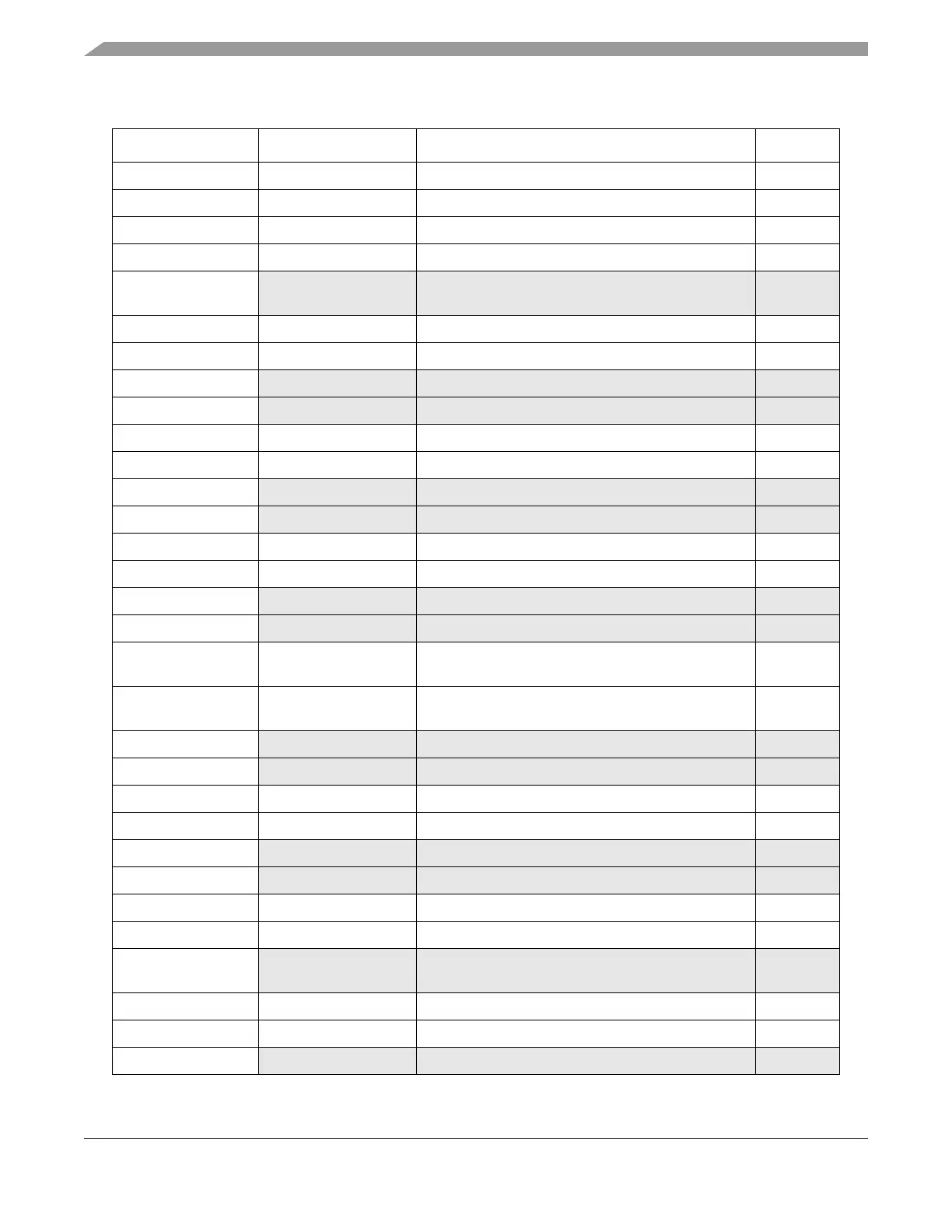

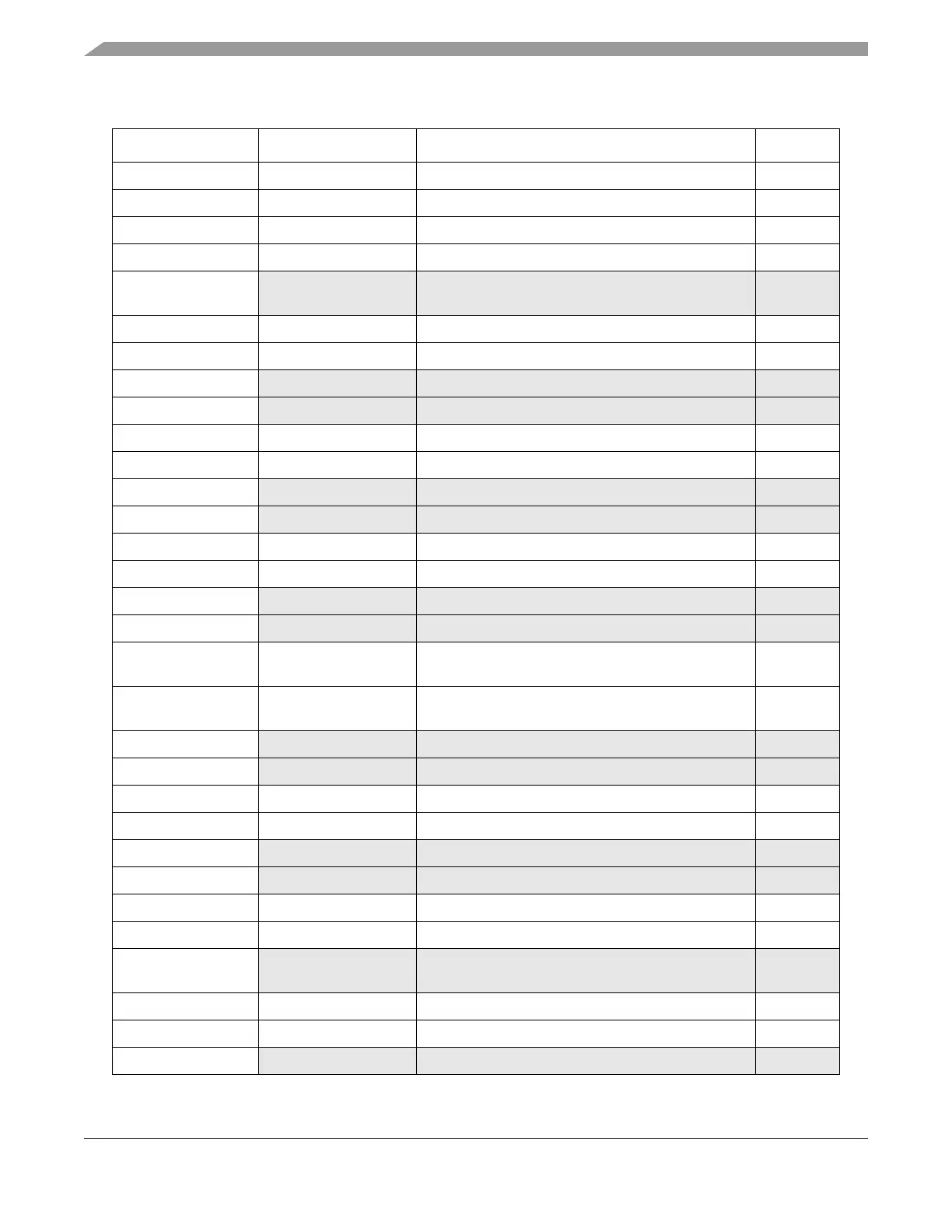

Base + 0x0_0040 ETPU_TBCR_B

1

eTPU B time base configuration register 32

Base + 0x0_0044 ETPU_TB1R_B

1

eTPU B time base 1 32

Base + 0x0_0048 ETPU_TB2R_B

1

eTPU B time base 2 32

Base + 0x0_004C ETPU_REDCR_B

1

eTPU B STAC bus interface configuration register 32

Base + 0x0_0050–

Base + 0x0_01FF

— Reserved —

Base + 0x0_0200 ETPU_CISR_A eTPU A channel interrupt status register 32

Base + 0x0_0204 ETPU_CISR_B

1

eTPU B channel interrupt status register 32

Base + 0x0_0208

— Reserved —

Base + 0x0_020C

— Reserved —

Base + 0x0_0210 ETPU_CDTRSR_A eTPU A channel data transfer request status register 32

Base + 0x0_0214 ETPU_CDTRSR_B

1

eTPU B channel data transfer request status register 32

Base + 0x0_0218

— Reserved —

Base + 0x0_021C — Reserved —

Base + 0x0_0220 ETPU_CIOSR_A eTPU A channel interrupt overflow status register 32

Base + 0x0_0224 ETPU_CIOSR_B

1

eTPU B channel interrupt overflow status register 32

Base + 0x0_0228 — Reserved —

Base + 0x0_022C

— Reserved —

Base + 0x0_0230 ETPU_CDTROSR_A eTPU A channel data transfer request

overflow status register

32

Base + 0x0_0234 ETPU_CDTROSR_B

1

eTPU B channel data transfer request

overflow status register

32

Base + 0x0_0238

— Reserved —

Base + 0x0_023C — Reserved —

Base + 0x0_0240 ETPU_CIER_A eTPU A channel interrupt enable register 32

Base + 0x0_0244 ETPU_CIER_B

1

eTPU B channel interrupt enable register 32

Base + 0x0_0248 — Reserved —

Base + 0x0_024C

— Reserved —

Base + 0x0_0250 ETPU_CDTRER_A eTPU A channel data transfer request enable register 32

Base + 0x0_0254 ETPU_CDTRER_B

1

eTPU B channel data transfer request enable register 32

Base + 0x0_0258–

Base + 0x0_027F

— Reserved —

Base + 0x0_0280 ETPU_CPSSR_A eTPU A channel pending service status register 32

Base + 0x0_0284 ETPU_CPSSR_B

1

eTPU B channel pending service status register 32

Base + 0x0_0288

— Reserved —

Table 18-6. Detailed Memory Map (Continued)

Address Register Name Register Description Size (bits)

Loading...

Loading...