MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-17

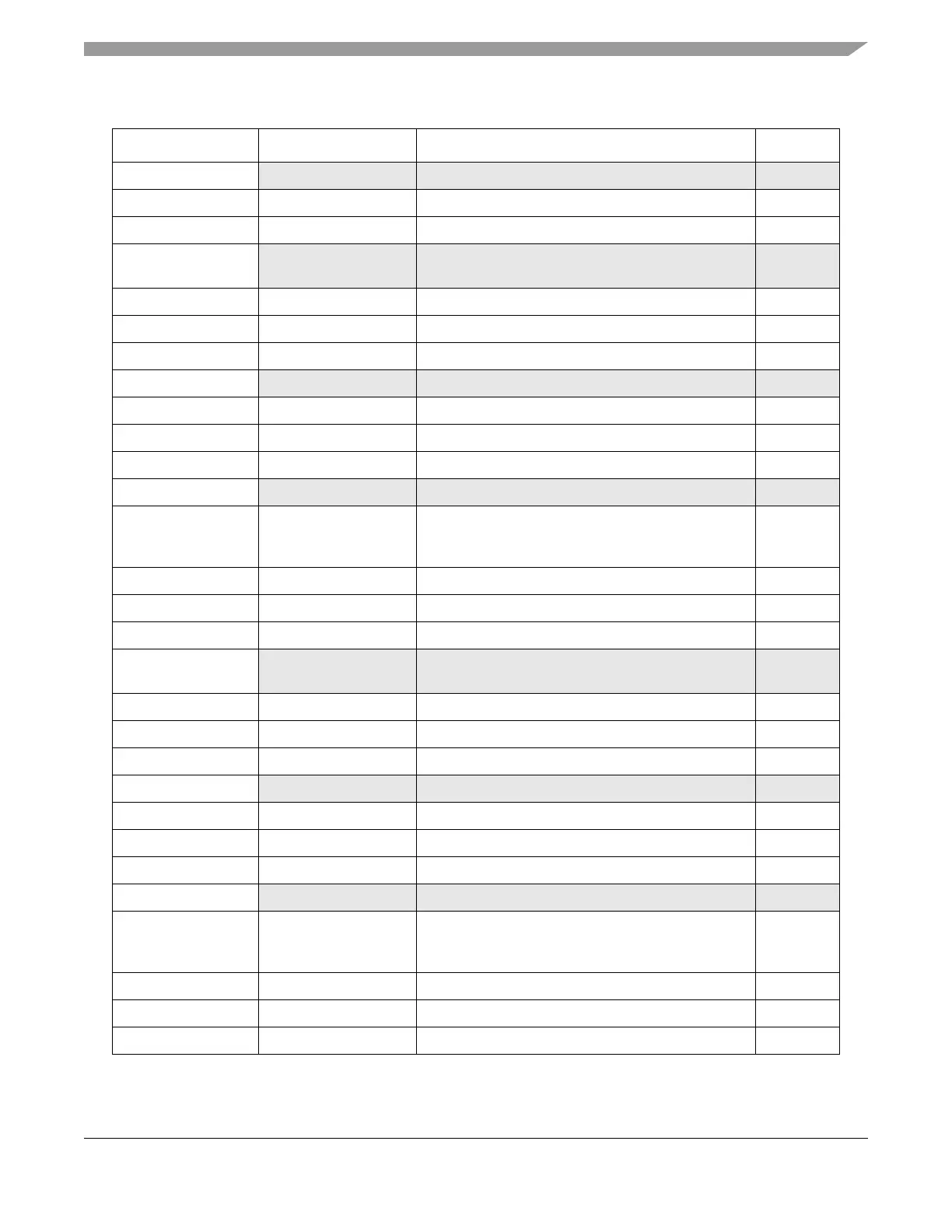

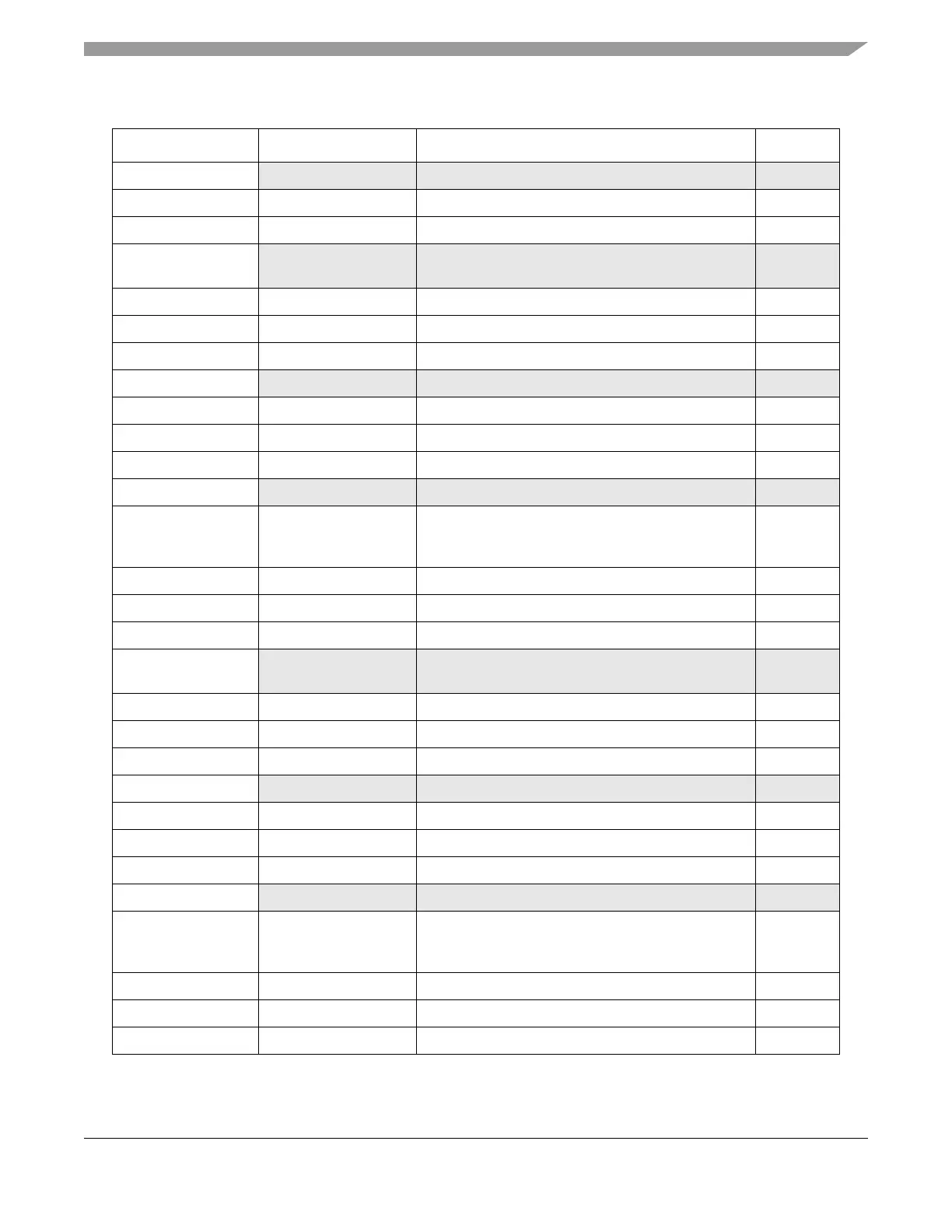

Base + 0x0_028C

— Reserved —

Base + 0x0_0290 ETPU_CSSR_A eTPU A channel service status register 32

Base + 0x0_0294 ETPU_CSSR_B

1

eTPU B channel service status register 32

Base + 0x0_0298–

Base + 0x0_03FF

— Reserved —

Base + 0x0_0400 ETPU_C0CR_A eTPU A channel 0 configuration register 32

Base + 0x0_0404 ETPU_C0SCR_A eTPU A channel 0 status and control register 32

Base + 0x0_0408 ETPU_C0HSRR_A eTPU A channel 0 host service request register 32

Base + 0x0_040C

— Reserved —

Base + 0x0_0410 ETPU_C1CR_A eTPU A channel 1 configuration register 32

Base + 0x0_0414 ETPU_C1SCR_A eTPU A channel 1 status and control register 32

Base + 0x0_0418 ETPU_C1HSRR_A eTPU A channel 1 host service request register 32

Base + 0x0_041C

— Reserved —

.

.

.

.

.

.

.

.

.

.

.

.

Base + 0x0_05F0 ETPU_C31CR_A eTPU A channel 31 configuration register 32

Base + 0x0_05F4 ETPU_C31SCR_A eTPU A channel 31 status and control register 32

Base + 0x0_05F8 ETPU_C31HSRR_A eTPU A channel 31 host service request register 32

Base + 0x0_05FC–

Base + 0x0_07FF

— Reserved —

Base + 0x0_0800 ETPU_C0CR_B

1

eTPU B channel 0 configuration register 32

Base + 0x0_0804 ETPU_C0SCR_B

1

eTPU B channel 0 status and control register 32

Base + 0x0_0808 ETPU_C0HSRR_B

1

eTPU B channel 0 host service request register 32

Base + 0x0_080C

— Reserved —

Base + 0x0_0810 ETPU_C1CR_B

1

eTPU B channel 1 configuration register 32

Base + 0x0_0814 ETPU_C1SCR_B

1

eTPU B channel 1 status and control register 32

Base + 0x0_0818 ETPU_C1HSRR_B

1

eTPU B channel 1 host service request register 32

Base + 0x0_081C

— Reserved —

.

.

.

.

.

.

.

.

.

.

.

.

Base + 0x0_09F0 ETPU_C31CR_B

1

eTPU B channel 31 configuration register 32

Base + 0x0_09F4 ETPU_C31SCR_B

1

eTPU B channel 31 status and control register 32

Base + 0x0_09F8 ETPU_C31HSRR_B

1

eTPU B Channel 31 host service request register 32

Table 18-6. Detailed Memory Map (Continued)

Address Register Name Register Description Size (bits)

Loading...

Loading...