MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

18-18 Freescale Semiconductor

18.4.2.1 System Configuration Registers

18.4.2.1.1 eTPU Module Configuration Register (ETPU_MCR)

This register is global to both eTPU engines, and resides in the shared BIU. ETPU_MCR gathers global

configuration and status in the eTPU system, including global exception. It is also used for configuring the

SCM (shared code memory) operation and test.

Base + 0x0_09FC–

Base + 0x0_7FFF

— Reserved —

Base + 0x0_8000–

Base + 0x0_8BFF

— 3 Kbytes shared data memory (parameter RAM) 3 Kbytes

Base + 0x0_8C00–

Base + 0x0_BFFF

— Reserved —

Base + 0x0_C000–

Base + 0x0_CBFF

— 3 Kbytes SDM PSE mirror

2

3 Kbytes

Base + 0x0_CC00–

Base + 0x0_FFFF

— Reserved —

Base + 0x1_0000–

Base + 0x1_2FFF

SCM Shared code memory

3

12 Kbytes

(MPC5553)

16 Kbytes

(MPC5554)

Base + 0x1_3000–

Base + 0x1_FFFF

— Reserved —

1

The register at this address is available only on the MPC5554, not on the MPC5553.

2

Parameter sign extension access area. See the eTPU reference manual.

3

SCM access is only available under certain conditions when ETPU_MCR[VIS] = 1. The SCM can only be written in

32-bit accesses.

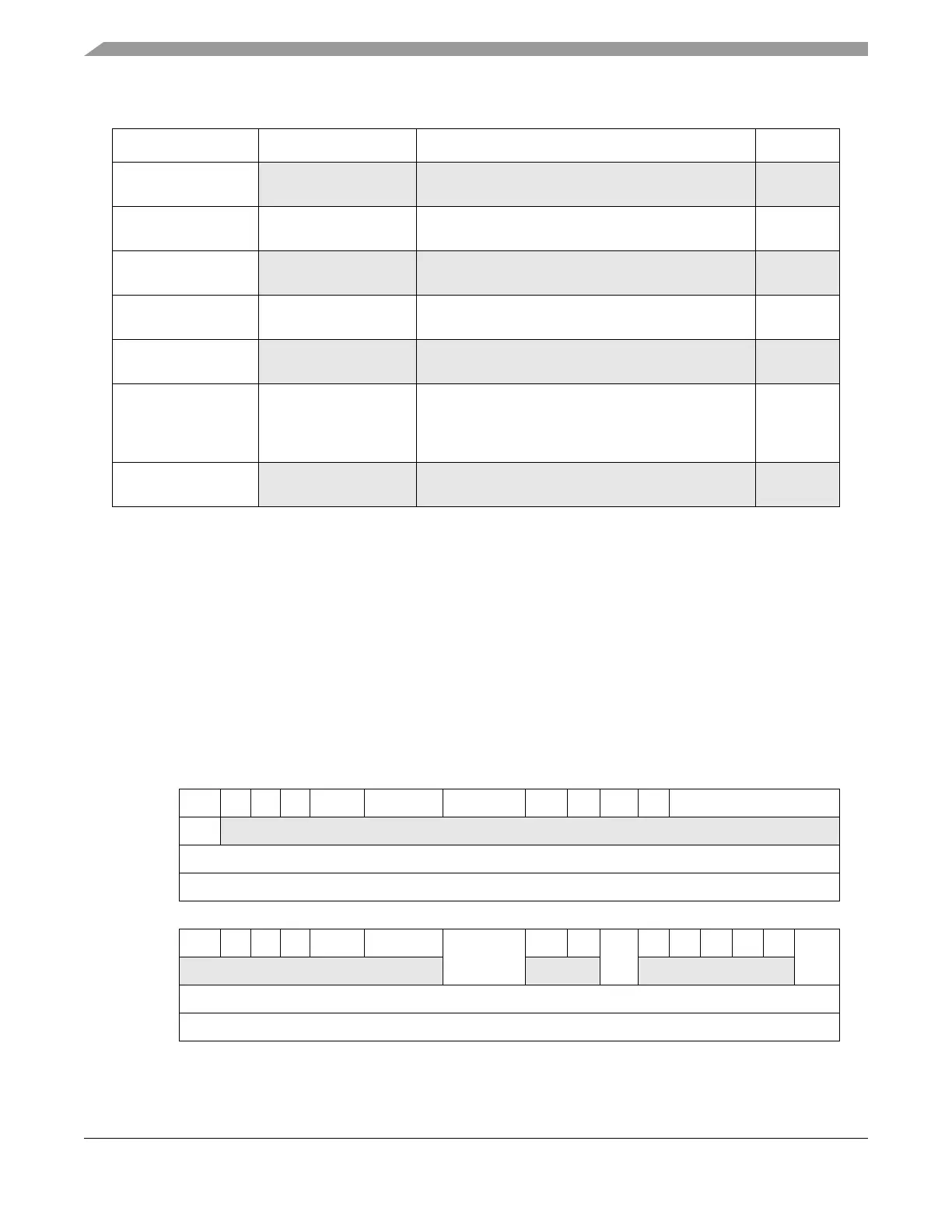

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R 0 0 0 0 MGEA MGEB ILFA ILFB 0 0 0 SCMSIZE

WGEC

Reset 0 0 0 0 0 0 0 0 0 0 0 SCMSIZE

Reg Addr Base + 0x0_0000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R0 000 0 SCMMISFSCMMISEN0 0VIS00000GTBE

W

Reset0 000 0 0 0 0 0 0 00000 0

Reg Addr Base + 0x0_0000

Figure 18-5. ETPU_MCR Register

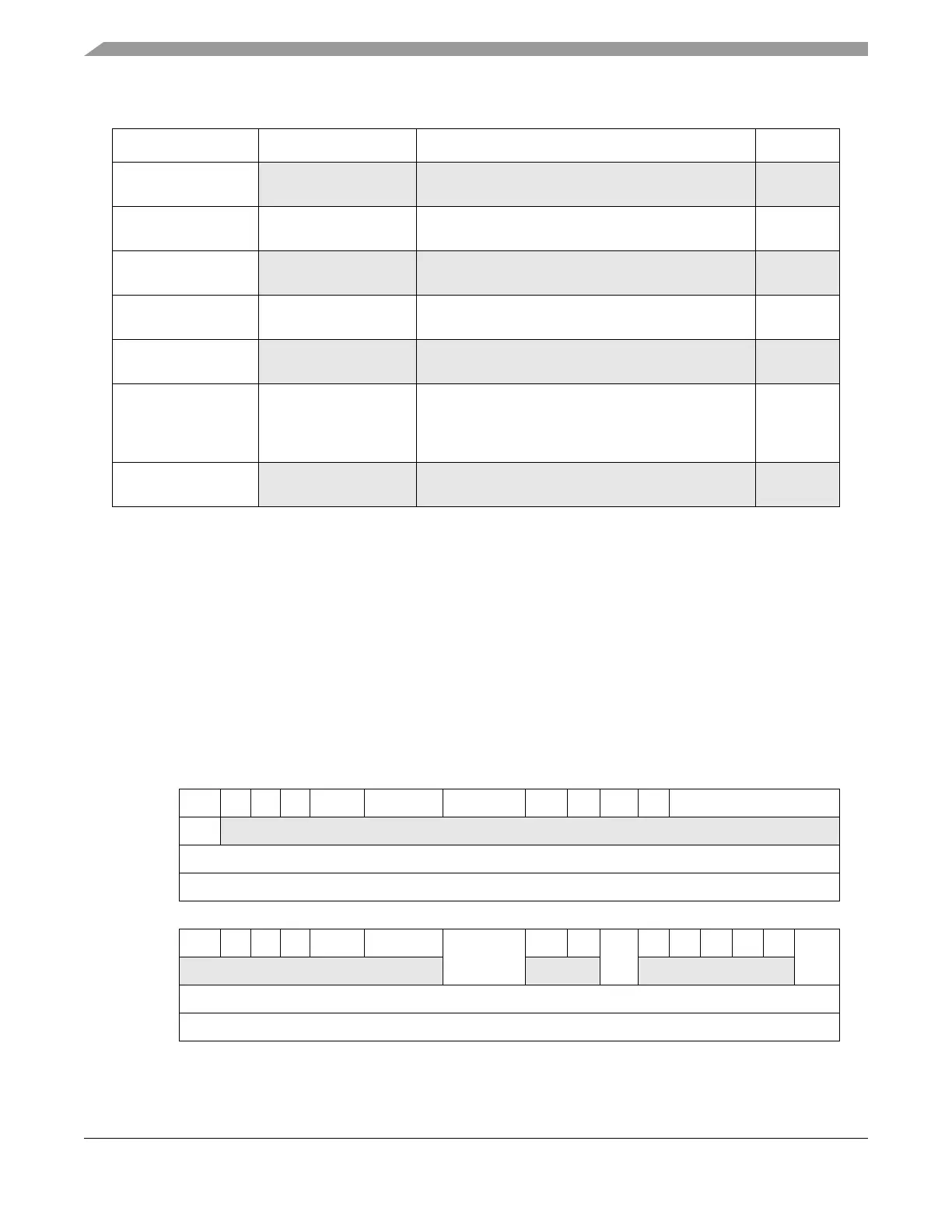

Table 18-6. Detailed Memory Map (Continued)

Address Register Name Register Description Size (bits)

Loading...

Loading...