MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 18-19

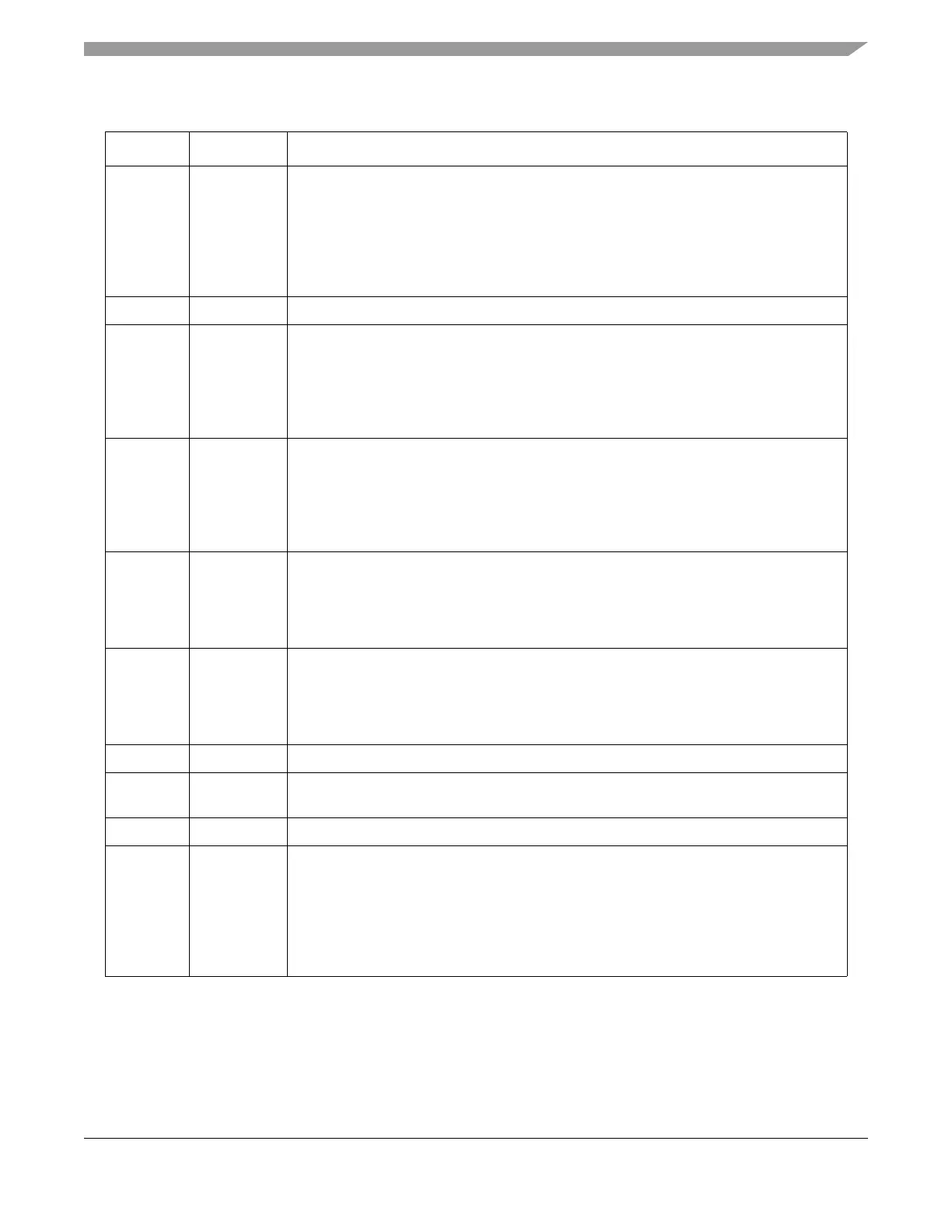

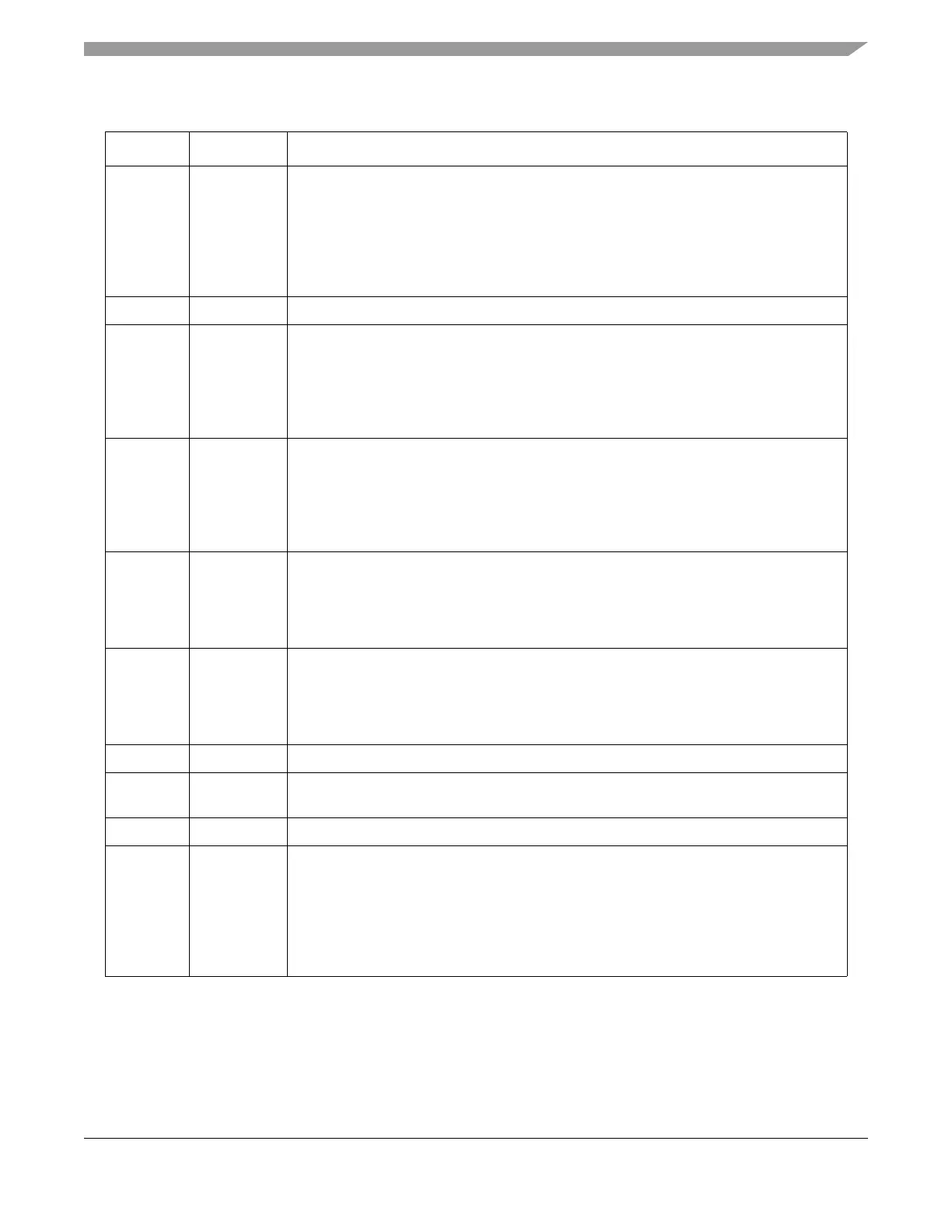

Table 18-7. ETPU_MCR Bit Field Descriptions

Bits Name Description

0 GEC Global exception clear. Negates global exception request and clears global exception

status bits MGEA, MGEB, ILFA, ILFB and SCMMISF. A read will always return 0. Writes

have the following effect:

0 Keep global exception request and status bits ILFA, ILFB, MGEA, MGEB, and

SCMMISF as is.

1 Negate global exception, clear status bits ILFA, ILFB, MGEA, MGEB, and SCMMISF.

GEC works the same way with either one or both engines in stop mode.

1–3 — Reserved.

4 MGEA Microcode global exception engine A. Indicates that a global exception was asserted by

microcode executed on the respective engine. The determination of the reason why the

global exception was asserted is application dependent: it can be coded in an SDM status

parameter, for instance. This bit is cleared by writing 1 to GEC.

0 No microcode-requested global exception pending.

1 Global exception requested by microcode is pending.

5 MGEB Microcode global exception engine B. Indicates that a global exception was asserted by

microcode executed on the respective engine. The determination of the reason why the

global exception was asserted is application dependent: it can be coded in an SDM status

parameter, for instance. This bit is cleared by writing 1 to GEC.

0 No microcode requested global exception pending.

1 Global exception requested by microcode is pending.

6 ILFA Illegal instruction flag eTPU A. Set by the microengine to indicate that an illegal instruction

was decoded in engine A. This bit is cleared by host writing 1 to GEC. For more information

about illegal instructions, see Section 9.6 in the eTPU reference manual.

0 Illegal Instruction not detected.

1 Illegal Instruction detected by eTPU A.

7 ILFB Illegal instruction flag eTPU B. Set by the microengine to indicate that an illegal instruction

was decoded in engine B. This bit is cleared by host writing 1 to GEC. For more details,

refer to the eTPU reference manual.

0 Illegal Instruction not detected.

1 Illegal Instruction detected by eTPU B.

8–10 — Reserved.

11–15 SCMSIZE

[0:4]

SCM size. Holds the number of 2 Kbyte SCM Blocks minus 1. This value is

MCU-dependent.

16–20 — Reserved.

21 SCMMISF SCM MISC Flag. Set by the SCM MISC (multiple input signature calculator) logic to

indicate that the calculated signature does not match the expected value, at the end of a

MISC iteration. For more details, refer to the eTPU reference manual for more details.

0 Signature mismatch not detected.

1 MISC has read entire SCM array and the expected signature in ETPU_MISCCMPR

does not match the value calculated.

This bit is cleared by writing 1 to GEC.

Loading...

Loading...