MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 17-7

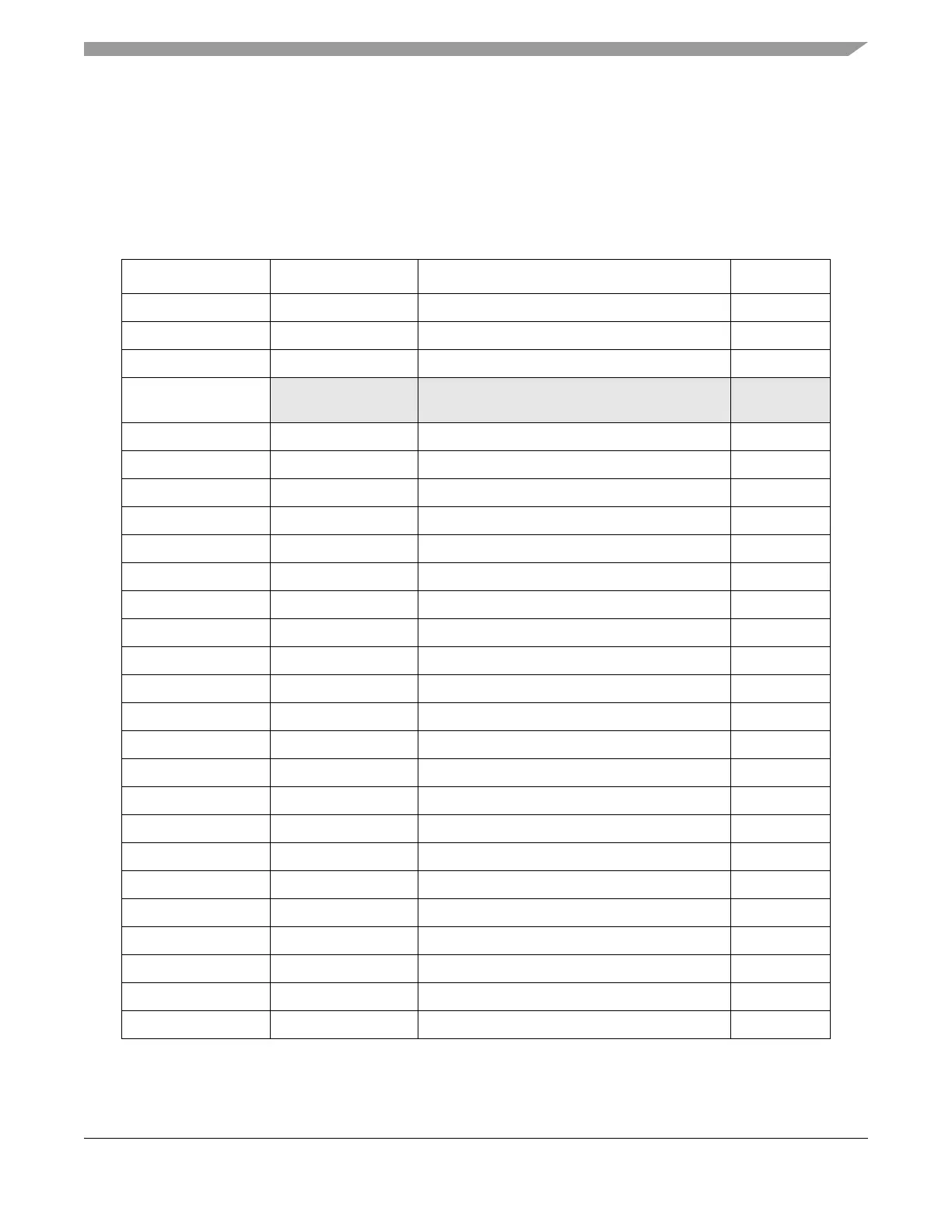

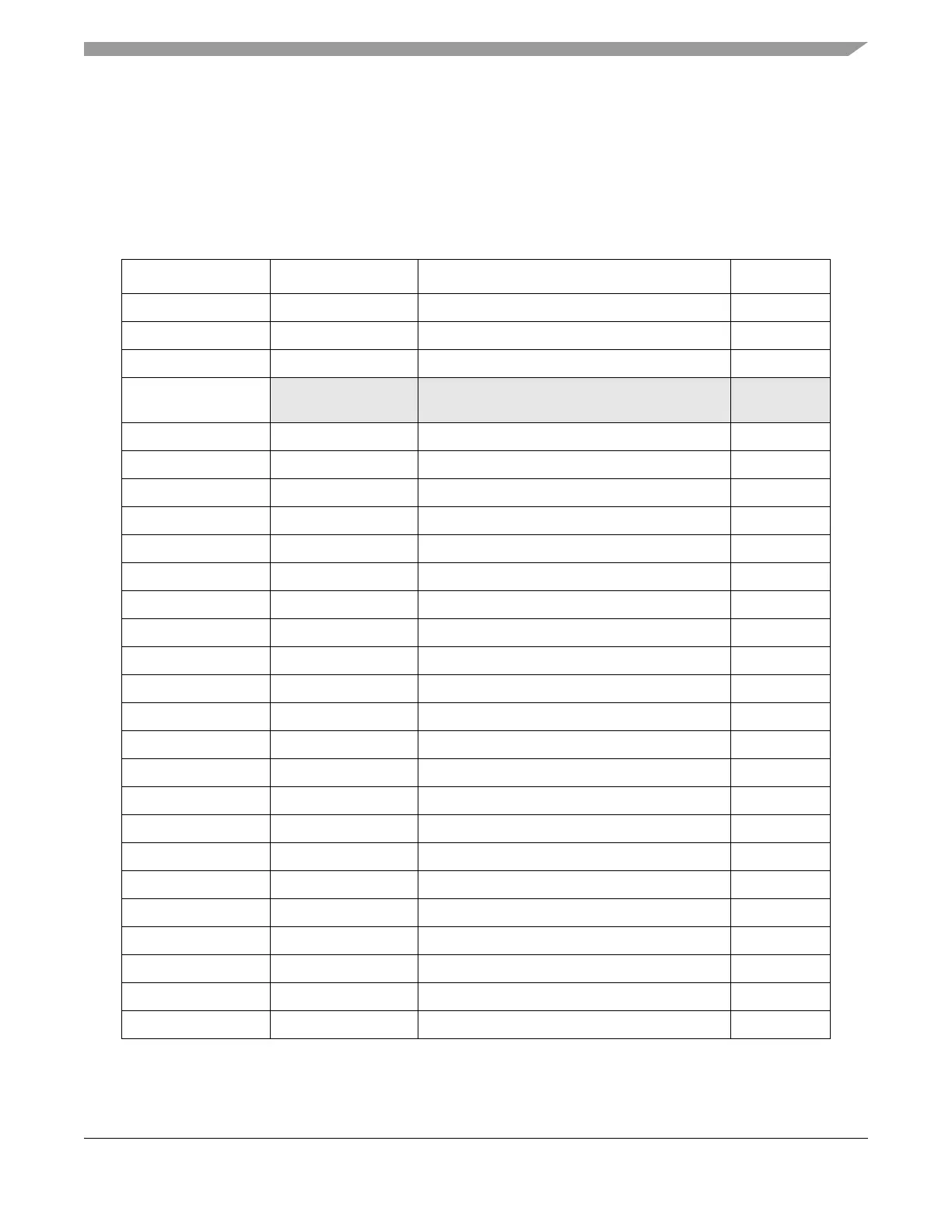

17.3 Memory Map/Register Definition

Addresses of unified channel (UC) registers are specified as offsets from the channel’s base address,

otherwise the eMIOS base address is used as reference.

The overall address map organization is shown in Table 17-4. Table 17-5 describes the unified channel

registers. All registers are cleared on reset.

Table 17-4. eMIOS Memory Map

Address Register Name Register Description Size (bits)

Base (0xC3FA_0000) EMIOS_MCR Module Configuration Register 32

Base + 0x00004 EMIOS_GFR Global Flag Register 32

Base + 0x0008 EMIOS_OUDR Output Update Disable Register 32

Base + 0x000C–

Base + 0x001F

— Reserved —

Base + 0x0020 UC0 Unified Channel 0 Registers 256

Base + 0x0040 UC1 Unified Channel 1 Registers 256

Base + 0x0060 UC2 Unified Channel 2 Registers 256

Base + 0x0080 UC3 Unified Channel 3 Registers 256

Base + 0x00A0 UC4 Unified Channel 4 Registers 256

Base + 0x00C0 UC5 Unified Channel 5 Registers 256

Base + 0x00E0 UC6 Unified Channel 6 Registers 256

Base + 0x0100 UC7 Unified Channel 7 Registers 256

Base + 0x0120 UC8 Unified Channel 8 Registers 256

Base + 0x0140 UC9 Unified Channel 9 Registers 256

Base + 0x0160 UC10 Unified Channel 10 Registers 256

Base + 0x0180 UC11 Unified Channel 11 Registers 256

Base + 0x01A0 UC12 Unified Channel 12 Registers 256

Base + 0x01C0 UC13 Unified Channel 13 Registers 256

Base + 0x01E0 UC14 Unified Channel 14 Registers 256

Base + 0x0200 UC15 Unified Channel 15 Registers 256

Base + 0x0220 UC16 Unified Channel 16 Registers 256

Base + 0x0240 UC17 Unified Channel 17 Registers 256

Base + 0x0260 UC18 Unified Channel 18 Registers 256

Base + 0x0280 UC19 Unified Channel 19 Registers 256

Base + 0x02A0 UC20 Unified Channel 20 Registers 256

Base + 0x02C0 UC21 Unified Channel 21 Registers 256

Loading...

Loading...