MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-24 Freescale Semiconductor

3.3.2.3 Cache Line Replacement Algorithm

On a cache read miss, the cache controller uses a pseudo-round-robin replacement algorithm to determine

which cache line will be selected to be replaced. There is a single replacement counter for the entire cache.

The replacement algorithm acts as follows: On a miss, if the replacement pointer is pointing to a way which

is not enabled for replacement by the type of the miss access (the selected line or way is locked), it is

incremented until an available way is selected (if any). After a cache line is successfully filled without

error, the replacement pointer increments to point to the next cache way.

3.3.3 Interrupt Types

The interrupts implemented in the MPC5553/MPC5554 and the exception conditions that cause them are

listed in Table 3-9.

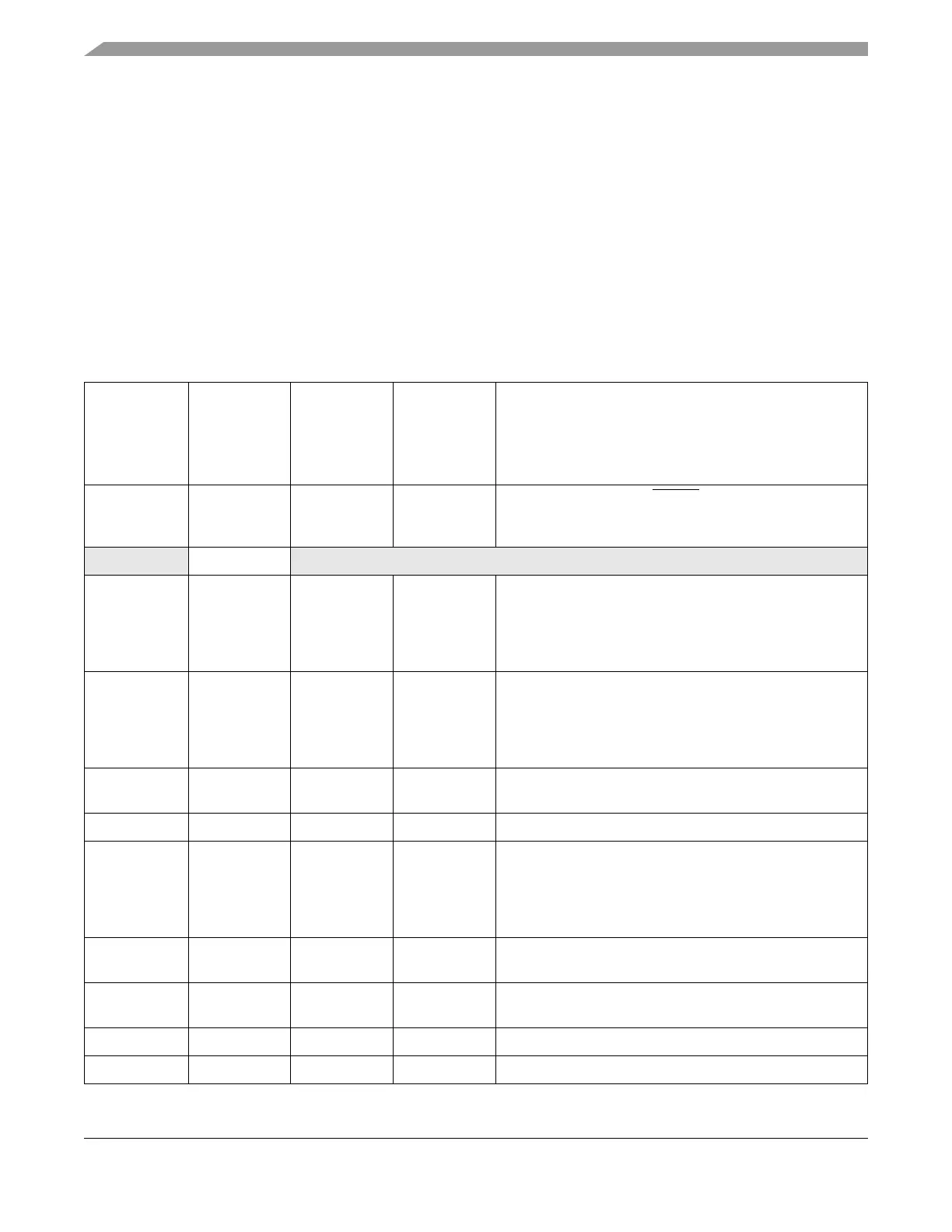

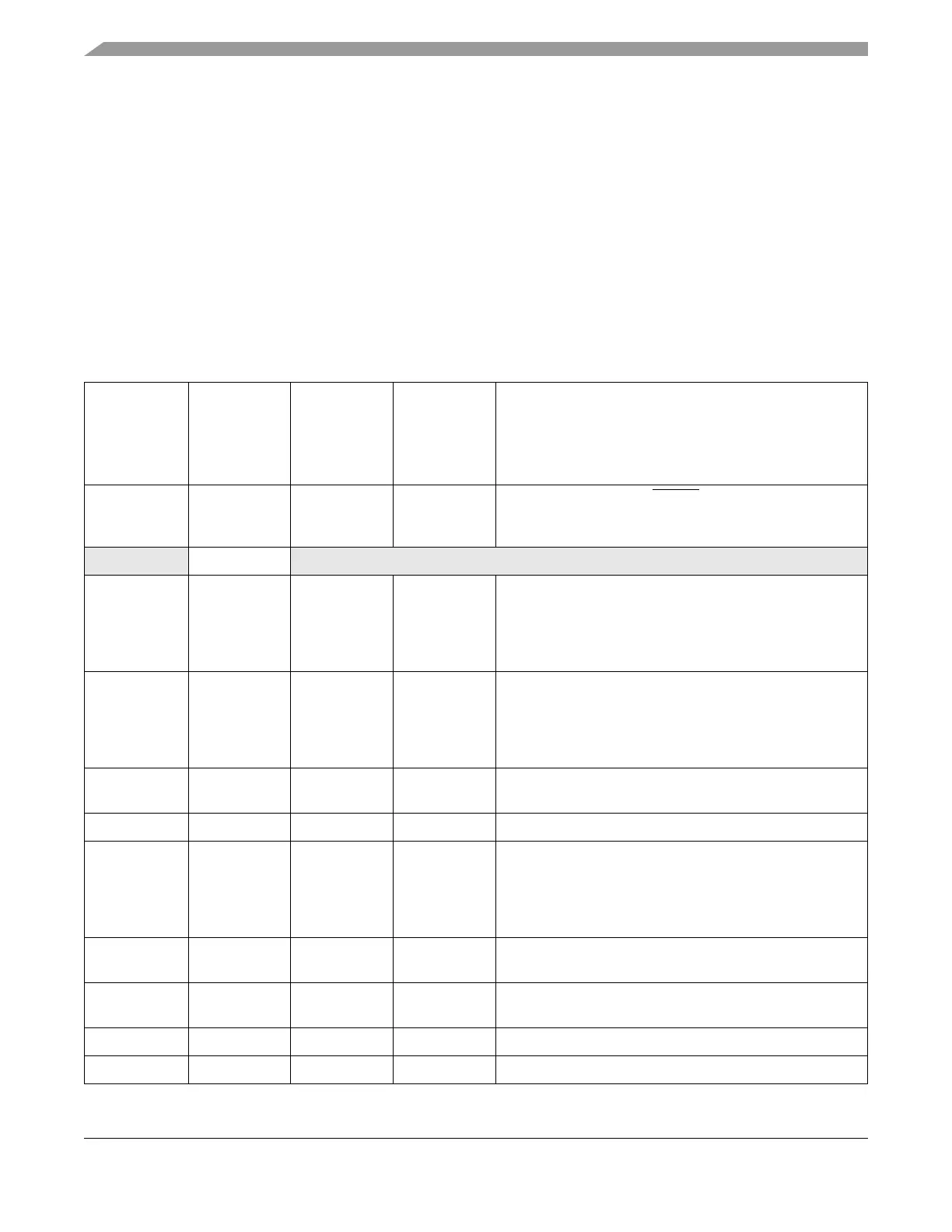

Table 3-9. Interrupts and Conditions

Interrupt Type

Interrupt

Vector Offset

Register

Enables

1

Core Register

in Which

State

Information is

Saved

Causing Conditions

System reset none,

vector to

0xFFFF_FFFC

• Reset by assertion of RESET

• Watchdog timer reset control.

• Debug Reset Control.

Critical input IVOR0 IVOR0 is not supported in the MPC5553/MPC5554

Machine check IVOR 1 ME CSSR[0:1] • Machine check exception and MSR[ME] =1.

• ISI, ITLB Error on first instruction fetch for an exception

handler

• Parity error signaled on cache access

• Write bus error on buffered store or cache line push

Data Storage IVOR 2 — SRR[0:1] • Access control.

• Byte ordering due to misaligned access across page

boundary to pages with mismatched E bits.

• Cache locking exception

• Precise external termination error

Instruction

Storage

IVOR 3 — SRR[0:1] • Access control.

• Precise external termination error

External Input IVOR 4

2

EE, src SRR[0:1] External interrupt is asserted and MSR[EE]=1.

Alignment IVOR 5 — SRR[0:1] • lmw, stmw not word aligned.

• lwarx or stwcx. not word aligned.

• dcbz with disabled cache or no cache present, or to W

or I storage.

• SPE ld and st instructions not properly aligned

Program IVOR 6 — SRR[0:1] Illegal, Privileged, Trap, FP enabled, AP enabled,

Unimplemented Operation.

Floating-point

unavailable

IVOR 7 — SRR[0:1] MSR[FP]=0 and attempt to execute a Book E floating point

operation.

System call IVOR 8 — SRR[0:1] Execution of the System Call (sc) instruction

AP unavailable IVOR 9 — SRR[0:1] Unused by e200z6

Loading...

Loading...