MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 3-23

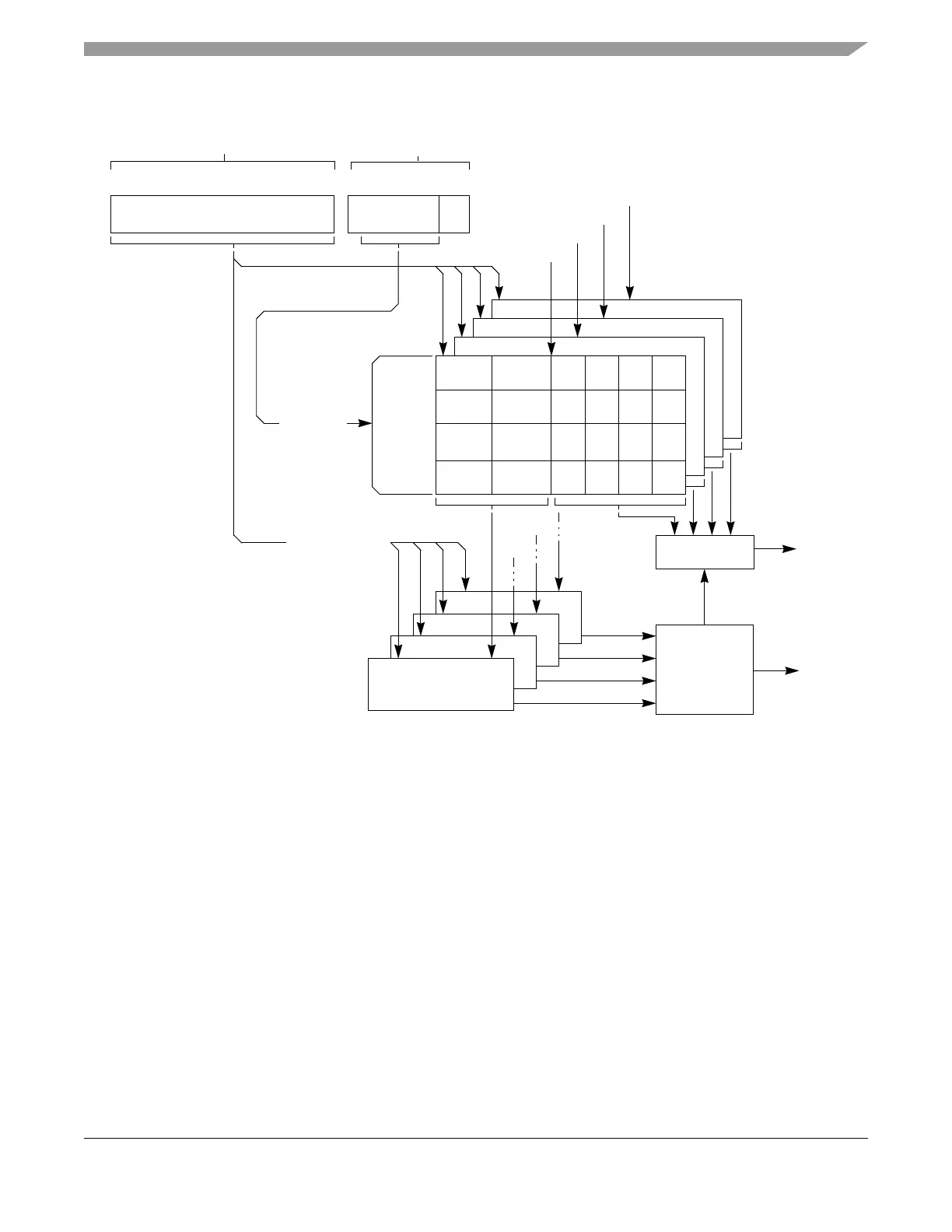

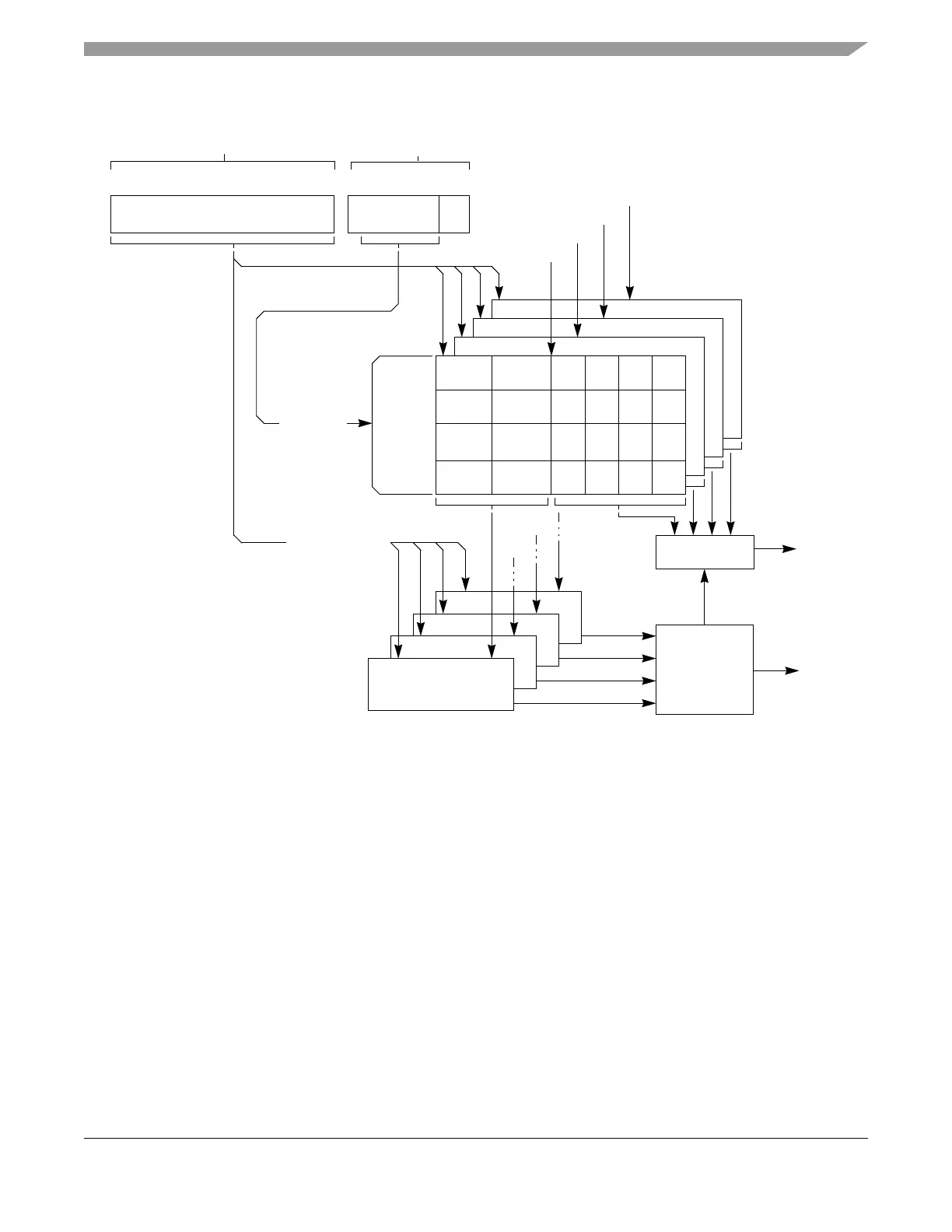

Figure 3-15 illustrates the general flow of cache operation.

Figure 3-15. Cache Lookup Flow

To determine if the address is already allocated in the cache the following steps are taken:

1. The cache set index, virtual address bits A[20:26] are used to select one cache set. A set is defined

as the grouping of eight lines (one from each way), corresponding to the same index into the cache

array.

2. The higher order physical address bits A[0:19] are used as a tag reference or used to update the

cache line tag field.

3. The eight tags from the selected cache set are compared with the tag reference. If any one of the

tags matches the tag reference and the tag status is valid, a cache hit has occurred.

4. Virtual address bits A[27:28] are used to select one of the four doublewords in each line. A cache

hit indicates that the selected doubleword in that cache line contain valid data (for a read access),

or can be written with new data depending on the status of the W access control bit from the

MMU (for a write access).

31

27

26

20

190

Index

Tag Data / Tag Reference

MUX

Comparator

0

1

2

7

Logical OR

HIT 7

HIT 2

HIT 1

HIT 0

Hit

Select

Set 0

Set 1

Set 127

•

•

•

Tag

Reference

A[0:19]

Way 0

Way 1

Way 2

Way 7

Data or

Instruction

Status DW0 DW1 DW2 DW3

Tag

Status DW0 DW1

DW2

DW3

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Virtual Address

Set

Select

A[20:26])

Tag

Physical Address

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

*Ways 2-7 available

only in MPC5554

Loading...

Loading...