MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 4-15

Note that the BOOTCFG[0:1] = 11 is a meaningless configuration for the MPC5553, because the

arbitration pins and TSIZ have been removed.

4.4.4 Reset Configuration Timing

The timing diagram in Figure 4-4 shows the sampling of the BOOTCFG[0:1], WKPCFG, and

PLLCFG[0:1] pins for a power-on reset. The timing diagram is also valid for internal/external resets

assuming that V

DD,

V

DDSYN,

and V

DDEH6

are within valid operating ranges. The values of the

PLLCFG[0:1] pins are latched at the negation of the RSTOUT pin, if the RSTCFG pin is asserted at the

negation of RSTOUT

. The value of the WKPCFG signal is applied at the assertion of the internal reset

signal (as indicated by the assertion of RSTOUT). The values of the WKPCFG and BOOTCFG[0:1] pins

are latched 4 clock cycles before the negation of RSTOUT and stored in the reset status register

(SIU_RSR). BOOTCFG[0:1] are latched only if RSTCFG is asserted. WKPCFG is not dependent on

RSTCFG.

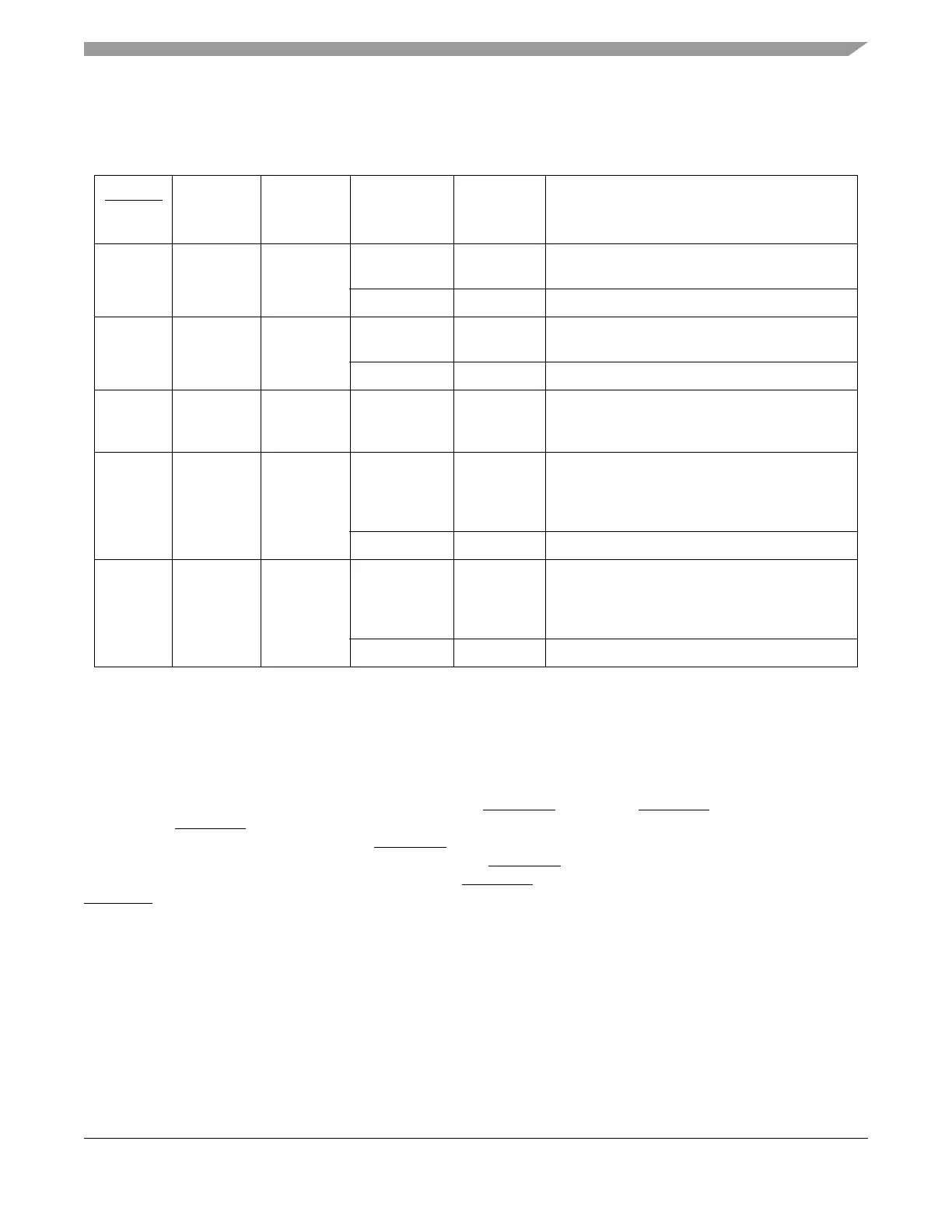

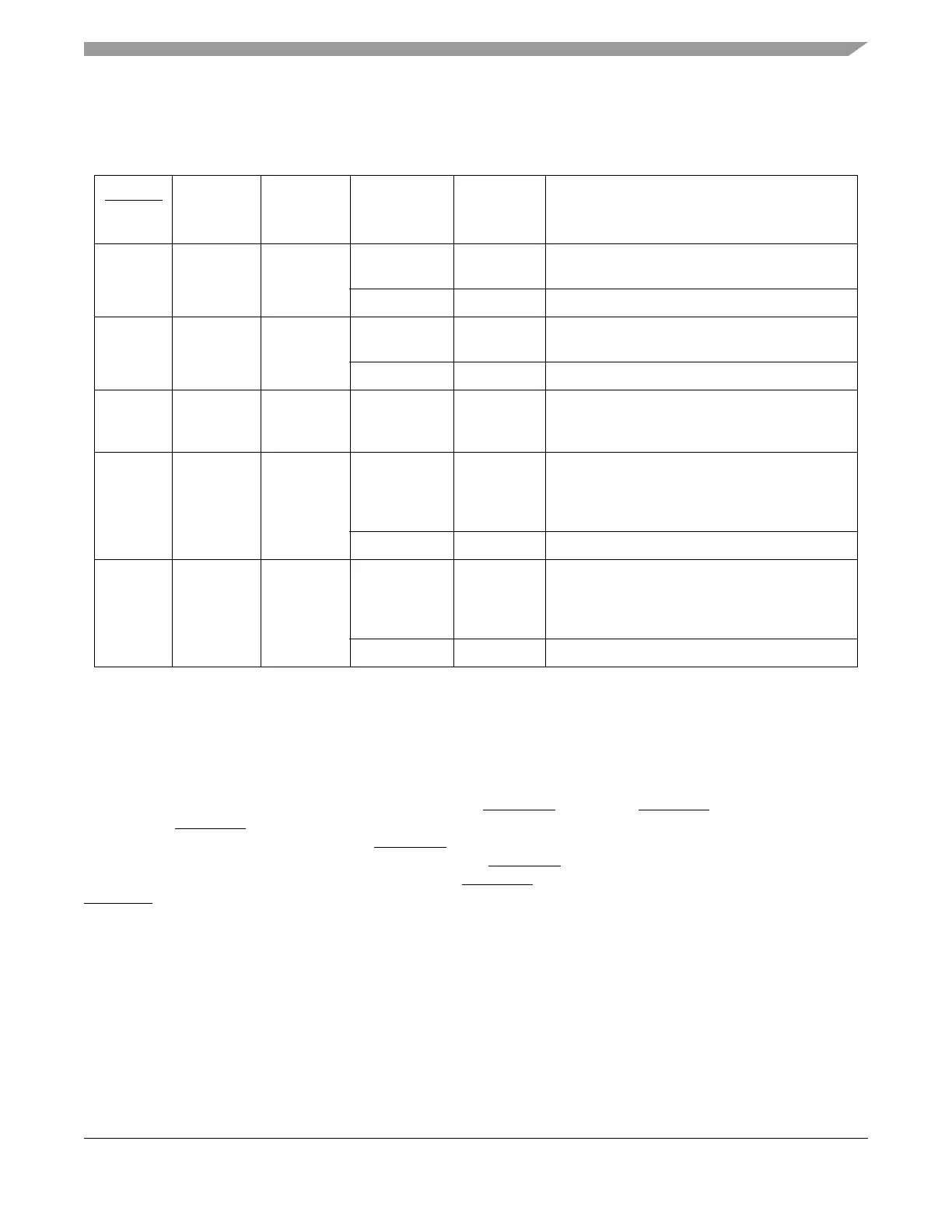

Table 4-11. MPC5553/MPC5554 Reset Configuration Half Word Sources

RSTCFG BOOTCFG0 BOOTCFG1

Boot Identifier

Field

(RCHW)

Boot Mode Configuration Word Source

1——

Valid Internal The lowest address of one of the six low address

spaces (LAS) in internal flash memory.

Invalid Serial Not applicable

00 0

Valid Internal The lowest address of one of the six low address

spaces (LAS) in internal flash memory.

Invalid Serial Not applicable

0 0 1 — Serial Not applicable

01 0

Valid

External

Boot,

No

Arbitration

The lowest address (0x00_0000) of an external

memory device, enabled by chip select CS0 using

either 16- or 32-bit data bus

Invalid Serial Not applicable

01 1

Valid

1

External

1

Boot,

External

Arbitration

1

External boot mode with external arbitration is not supported in the MPC5553.

The lowest address (0x0000_0000) of an external

memory device, enabled by chip select CS0 using

either 16- or 32-bit data bus.

Invalid Serial Not applicable

Loading...

Loading...