MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 14-33

14.3.4.3.4 Receive Buffer Size Register (EMRBR)

The EMRBR is a 32-bit register with one 7-bit field programmed by the user. The EMRBR register dictates

the maximum size of all receive buffers. Note that because receive frames will be truncated at 2K-1 bytes,

only bits 21–27 are used. This value should take into consideration that the receive CRC is always written

into the last receive buffer. To allow one maximum size frame per buffer, EMRBR must be set to

RCR[MAX_FL] or larger. The EMRBR must be evenly divisible by 16. To insure this, bits 28-31 are

forced low. To minimize bus utilization (descriptor fetches) it is recommended that EMRBR be greater

than or equal to 256 bytes.

The EMRBR register does not reset, and must be initialized by the user.

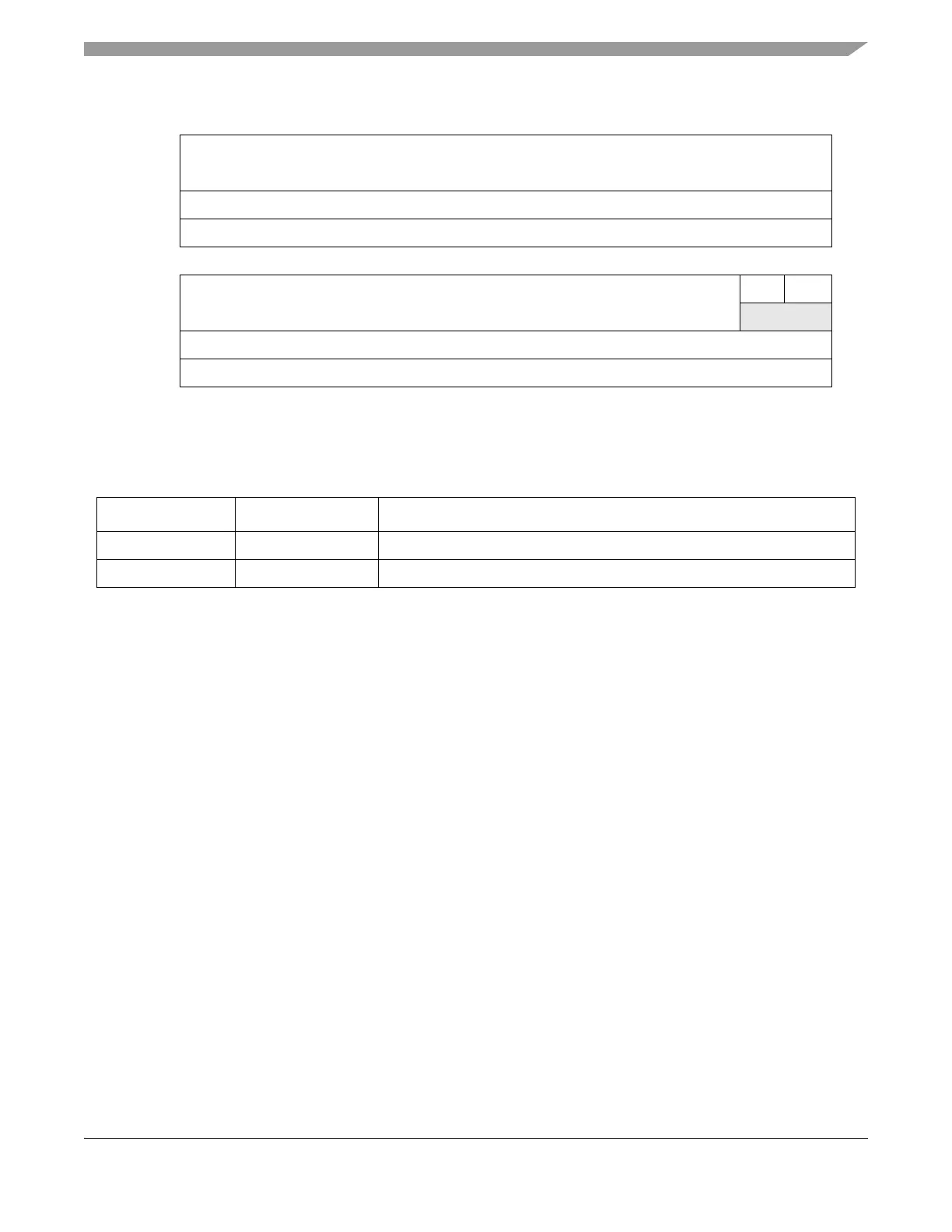

0 1 2 3456 7 8 91011121314 15

R X_DES_START

W

Reset U U U U U U U U U U U U U U U U

Address Base + 0x0184

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R X_DES_START 0 0

W

Reset U U U U U U U U U U U U U U U U

Address Base + 0x0184

1

“U” signifies a bit that is uninitialized.

Figure 14-24. Transmit Buffer Descriptor Ring Start Register (ETDSR)

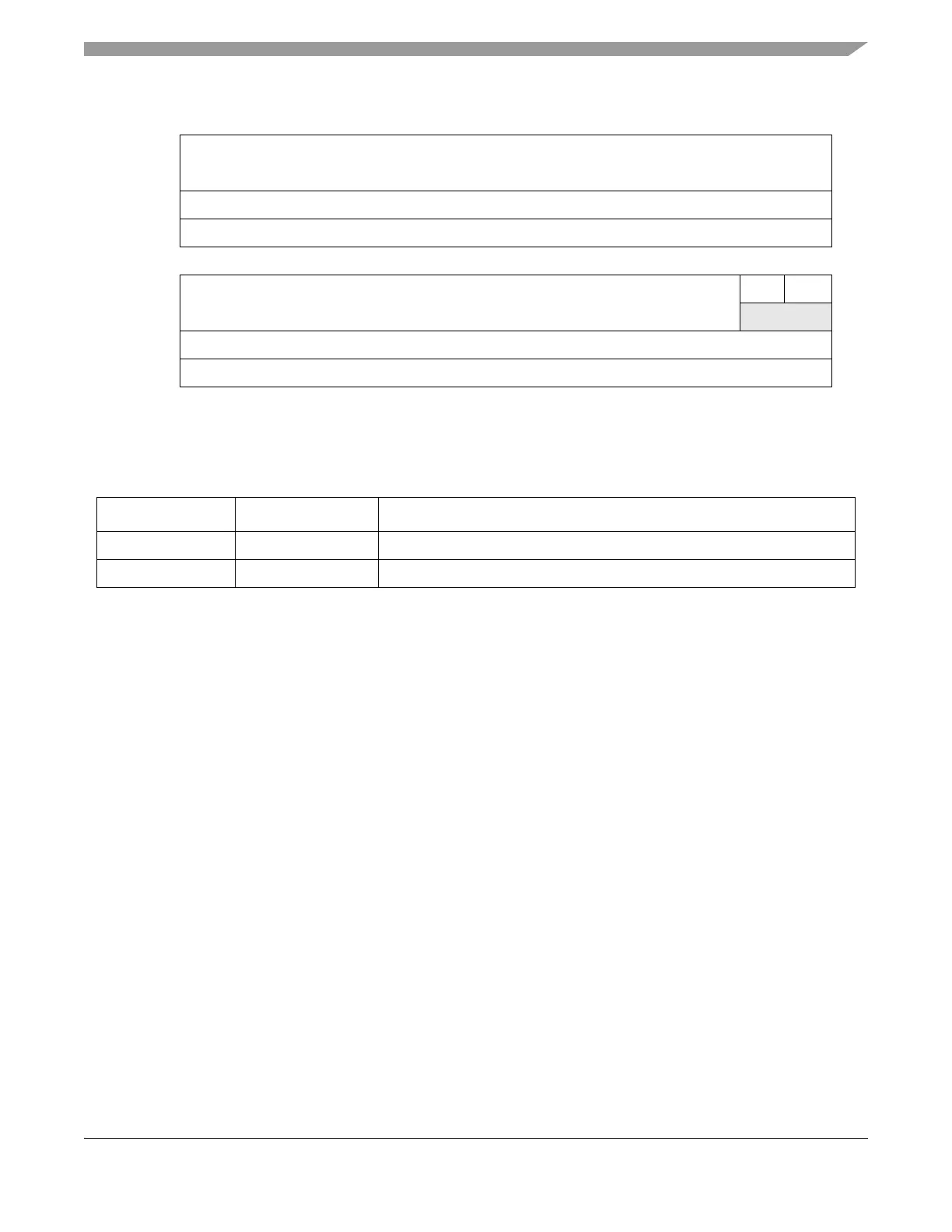

Table 14-27. ETDSR Field Descriptions

Bits Name Descriptions

0–29 X_DES_START Pointer to start of transmit buffer descriptor queue.

30–31 — Reserved, should be cleared.

Loading...

Loading...