MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

13-22 Freescale Semiconductor

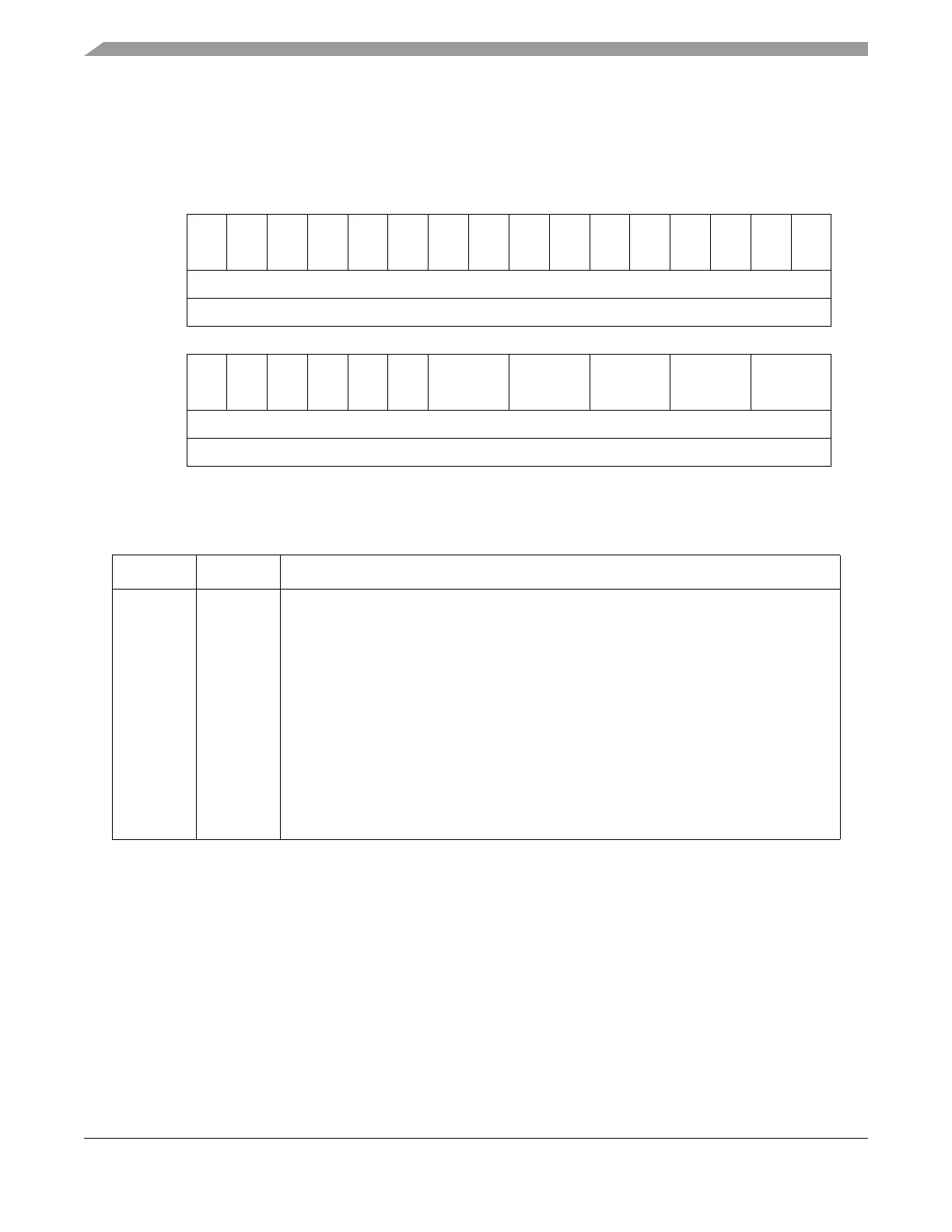

13.3.2.9 Flash Bus Interface Unit Access Protection Register (FLASH_BIUAPR)

The FLASH_BIUAPR controls access protection for the flash from masters on the crossbar switch. This

register should only be written in a 32-bit write operation.

0123456789101112131415

R1111111111111111

W

Reset1111111111111111

Reg Addr Base (0xC3F8_8000) + 0x0020

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R111111M4APM3APM2APM1APM0AP

W

Reset1111111111111111

Reg Addr Base (0xC3F8_8000) + 0x0020

Figure 13-13. Flash Bus Interface Unit Access Protection

Register (FLASH_BIUAPR)

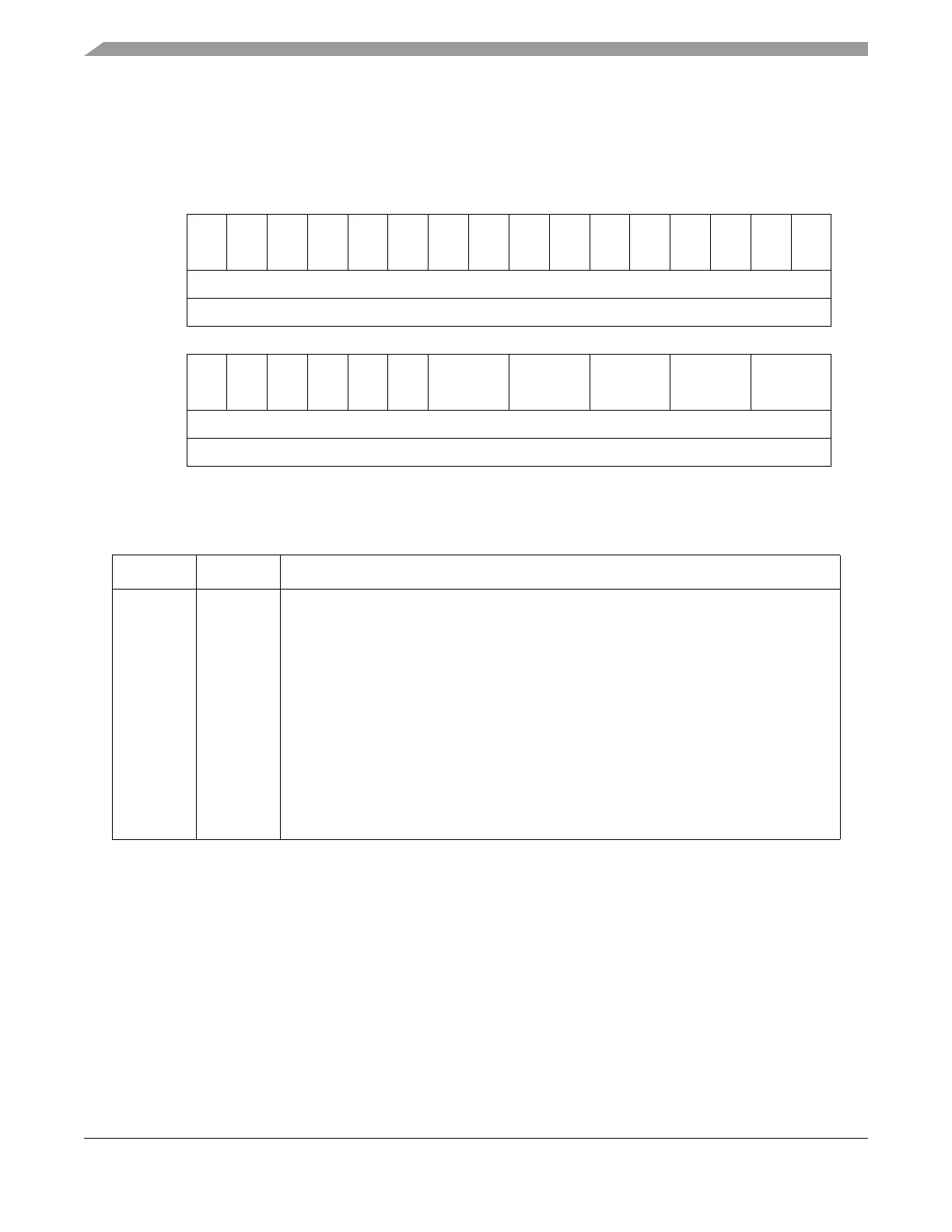

Table 13-16. FLASH_BIUAPR Field Descriptions

Bits Name Description

0–31 MnAP

[0:1]

Master n access protection. Controls whether read and write accesses to the flash are

allowed based on the master ID of a requesting master. These fields are initialized by

hardware reset. Refer to Tabl e 7- 1.

00 No accesses may be performed by this master

01 Only read accesses may be performed by this master

10 Only write accesses may be performed by this master

11 Both read and write accesses may be performed by this master

These fields are identified as follows:

M0AP= e200z6 core

M1AP= Nexus

M2AP= eDMA

M3AP= EBI

M4AP = FEC (implemented in the MPC5553 only)

Loading...

Loading...