MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 13-21

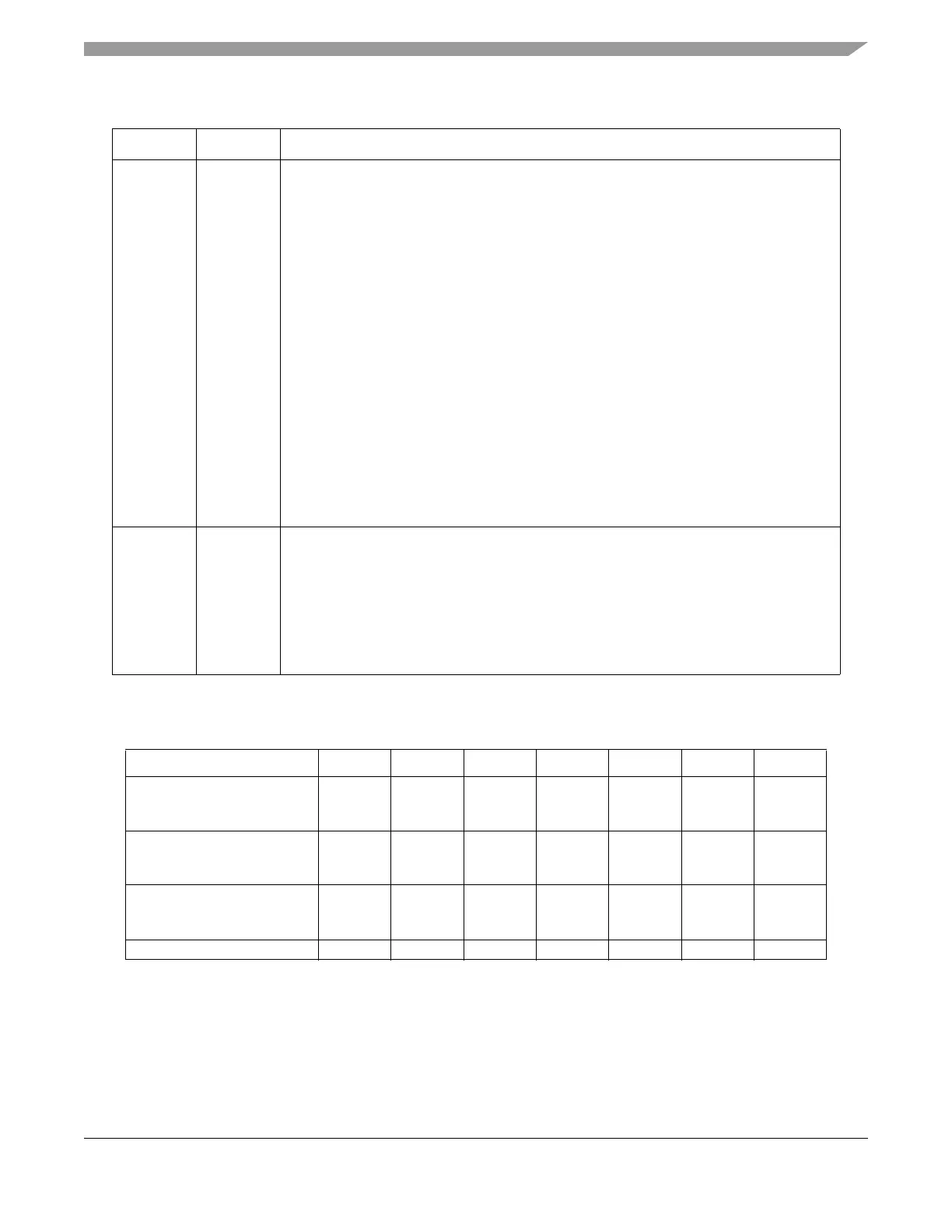

28–30 PFLIM Prefetch limit. Controls the prefetch algorithm used by the FBIU prefetch controller. This

field defines a limit on the maximum number of sequential prefetches which will be

attempted between buffer misses. This field is cleared by hardware reset.

000 No prefetching is performed

001 A single additional line (next sequential) is prefetched on a buffer miss

010 Up to two additional lines may be prefetched following each buffer miss before

prefetching is halted. A single additional line (next sequential) is prefetched on a

buffer miss, and the next sequential line is prefetched on a buffer hit (if not already

present).

011 Up to three additional lines may be prefetched following each buffer miss before

prefetching is halted. Only a single additional prefetch is initiated after each buffer hit

or miss.

100 Up to four additional lines may be prefetched following each buffer miss before

prefetching is halted. Only a single additional prefetch is initiated after each buffer hit

or miss.

101 Up to five additional lines may be prefetched following each buffer miss before

prefetching is halted. Only a single additional prefetch is initiated after each buffer hit

or miss.

110 An unlimited number of additional lines may be prefetched following each buffer miss.

Only a single additional prefetch is initiated on each buffer hit or miss.

111 Reserved

31 BFEN FBIU line read buffers enable. Enables or disables line read buffer hits. It is also used to

invalidate the buffers. These bits are cleared by hardware reset.

0 The line read buffers are disabled from satisfying read requests, and all buffer valid bits

are cleared.

1 The line read buffers are enabled to satisfy read requests on hits. Buffer valid bits may

be set when the buffers are successfully filled.

Note: Disable prefetching before invalidating the buffers. This includes starting a program

or erase operation, or turning on and off the buffers.

1

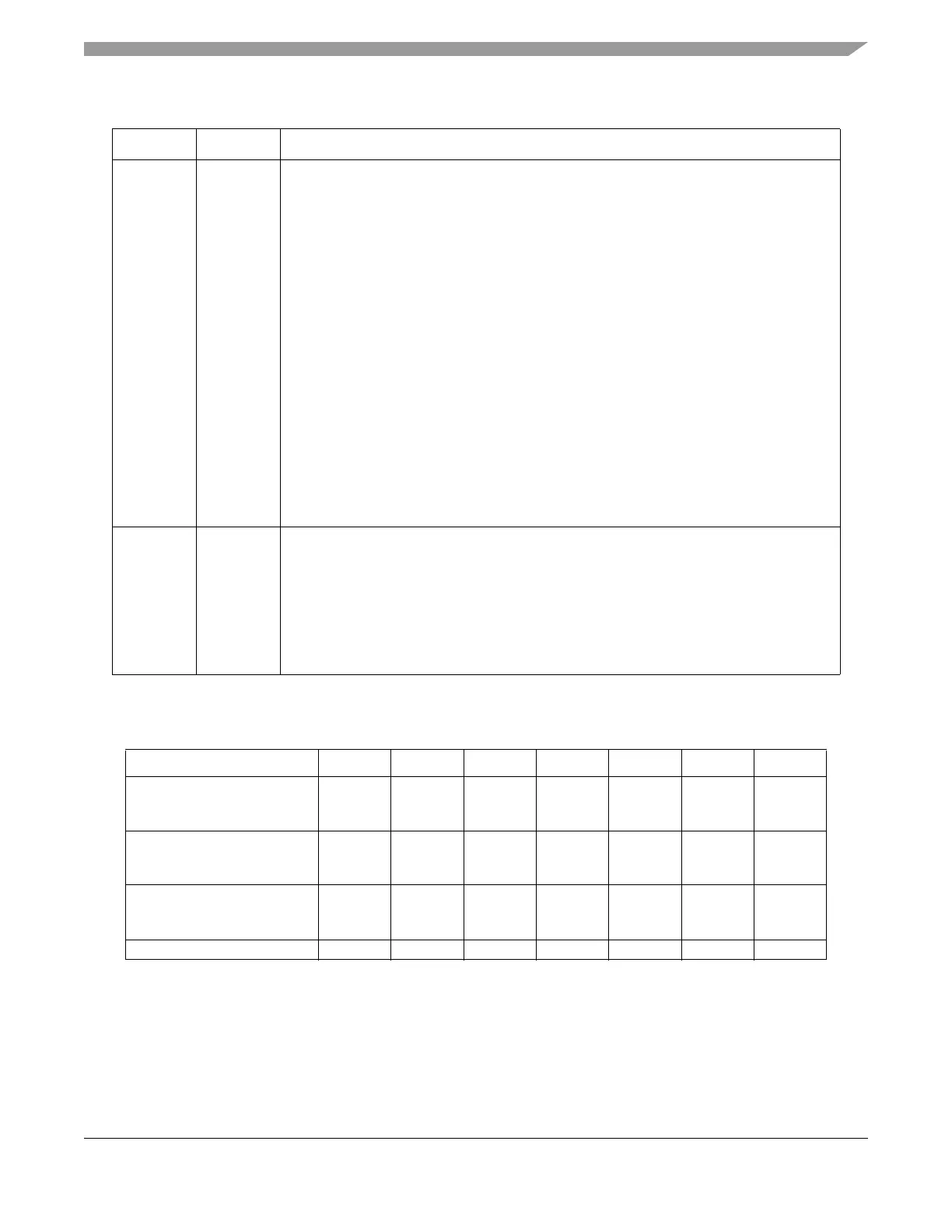

APC, WWSC, and RWSC values are determined by the maximum frequency of operation. See Table 13-15.

Table 13-15. FLASH_BIU Settings vs. Frequency of Operation

Maximum Frequency (MHz) APC RWSC WWSC DPFEN IPFEN PFLIM BFEN

up to and including 82 MHz

1

1

This setting allows for 80 MHz system clock with 2% frequency modulation.

0b001 0b001 0b01 0b00,

0b01, or

0b11

2

2

For maximum flash performance, this should be set to 0b11.

0b00,

0b01, or

0b11

2

0b000-

0b110

3

3

For maximum flash performance, this should be set to 0b110.

0b0, 0b1

4

4

For maximum flash performance, this should be set to 0b1.

up to and including 102 MHz

5

5

This setting allows for 100 MHz system clock with 2% frequency modulation.

0b001 0b010 0b01 0b00,

0b01, or

0b11

2

0b00,

0b01, or

0b11

2

0b000-

0b110

3

0b0, 0b1

4

up to and including132 MHz

6

6

This setting allows for 128 MHz system clock with 2% frequency modulation.

0b010 0b011 0b01 0b00,

0b01, or

0b11

2

0b00,

0b01, or

0b11

2

0b000-

0b110

3

0b0, 0b1

4

Default setting after reset 0b111 0b111 0b11 0b00 0b00 0b000 0b0

Table 13-14. FLASH_BIUCR Field Descriptions (Continued)

Bits Name Description

Loading...

Loading...