MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

13-20 Freescale Semiconductor

1

M4PFE is functional only in the MPC5553.

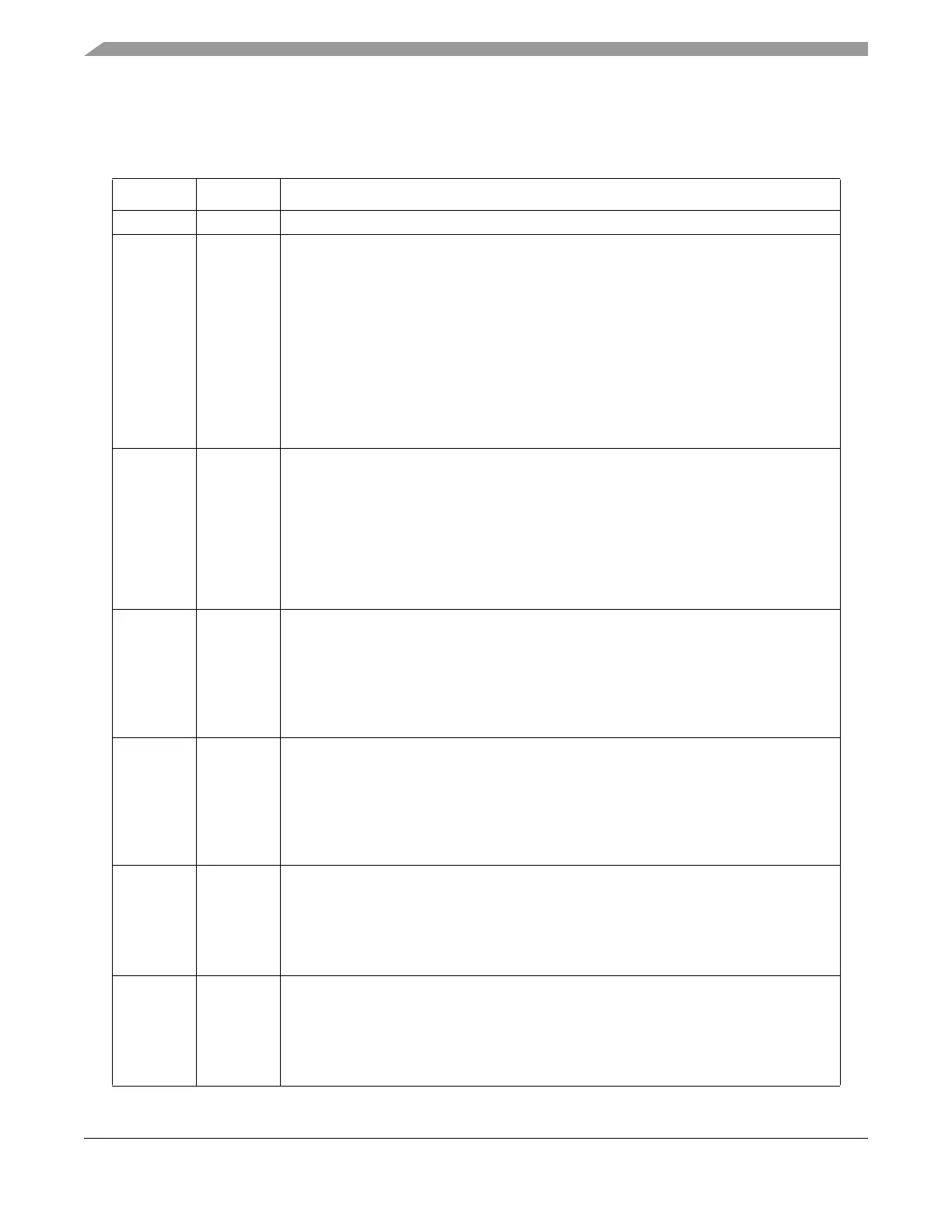

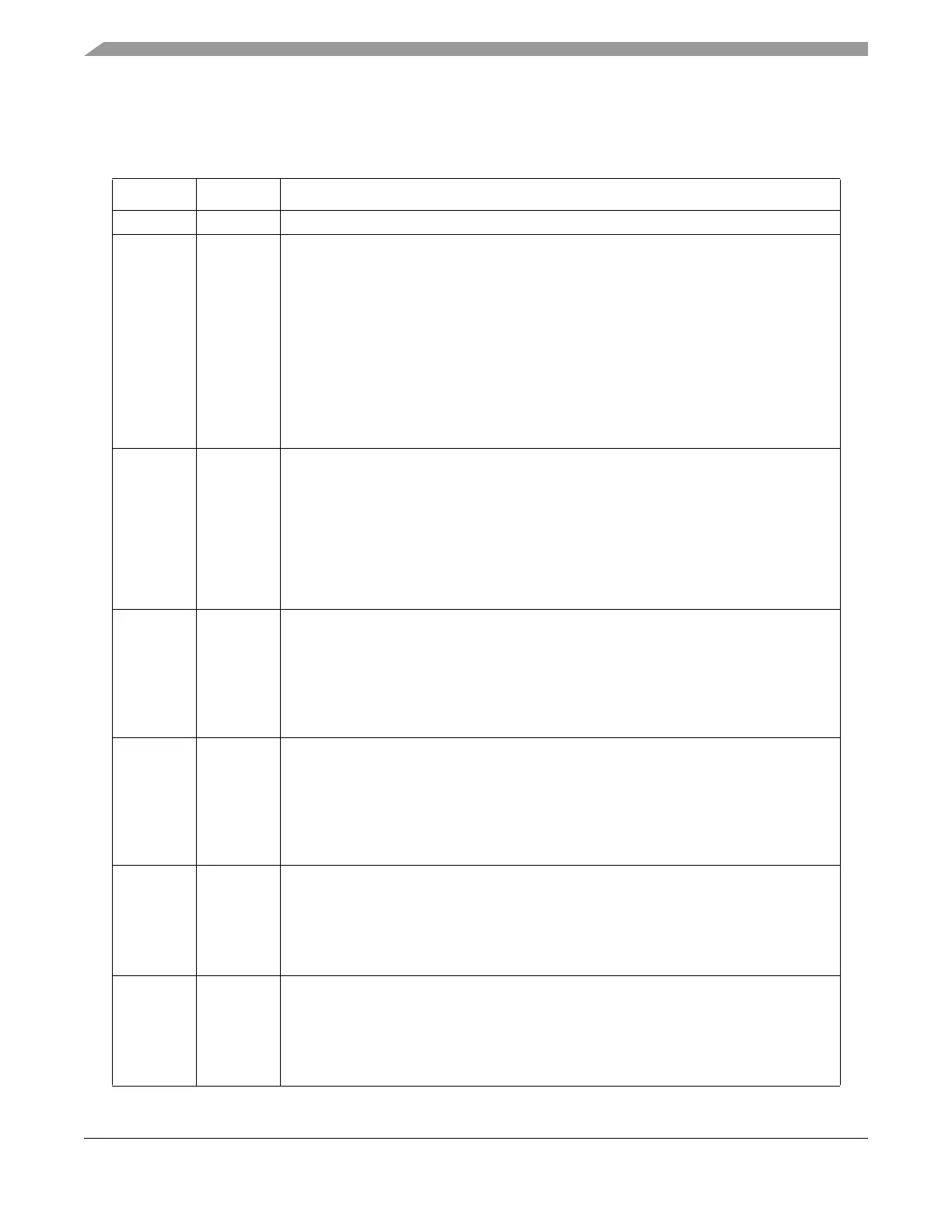

Table 13-14. FLASH_BIUCR Field Descriptions

Bits Name Description

0-11 — Reserved

12–15 MnPFE Master n prefetch enable. Used to control whether prefetching may be triggered based on

the master ID of a requesting master. These bits are cleared by hardware reset. Refer to

Ta bl e 7 -1 .

0 No prefetching may be triggered by this master

1 Prefetching may be triggered by this master

These fields are identified as follows:

M4PFE = FEC (in MPC5553 only)

M3PFE= EBI

M2PFE= eDMA

M1PFE= Nexus

M0PFE= e200z6 core

16–18 APC

1

Address pipelining control. Used to control the number of cycles between pipelined access

requests. This field must be set to a value corresponding to the operating frequency of the

system clock. The required settings are documented in Table 13-15.

000 Reserved

001 Access requests require one hold cycle

010 Access requests require two hold cycles

...

110 Access requests require 6 hold cycles

111 No address pipelining

19–20 WWSC

1

Write wait state control. Used to control the timing for array writes. This field must be set to

a value corresponding to the operating frequency of the system clock. The required

settings are documented in Table 13-15.

00 Reserved

01 One wait state

10 Two wait states

11 Three wait states

21–23 RWSC

1

Read wait state control. Used to control the flash array access time for array reads. This

field must be set to a value corresponding to the operating frequency of the system clock.

The required settings are documented in Ta ble 1 3- 15.

000 Zero wait states

001 One wait state

...

111 Seven wait states

24–25 DPFEN Data prefetch enable. Enables or disables prefetching initiated by a data read access. This

field is cleared by hardware reset.

00 No prefetching is triggered by a data read access

01 Prefetching may be triggered only by a data burst read access

10 Reserved

11 Prefetching may be triggered by any data read access

26–27 IPFEN Instruction prefetch enable. Enables or disables prefetching initiated by an instruction read

access. This field is cleared by hardware reset.

00 No prefetching is triggered by an instruction read access

01 Prefetching may be triggered only by an instruction burst read access

10 Reserved

11 Prefetching may be triggered by any instruction read access

Loading...

Loading...