MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 9-19

9.3.1.12 eDMA Clear DONE Status Bit Register (EDMA_CDSBR)

The EDMA_CDSBR provides a simple memory-mapped mechanism to clear the DONE bit in the TCD

of the given channel. The data value on a register write causes the DONE bit in the corresponding transfer

control descriptor to be cleared. Setting bit 1 (CDSBn) provides a global clear function, forcing all DONE

bits to be cleared. Reads of this register return all zeroes. For the MPC5553, bit 2 (CDSB1) is not used.

9.3.1.13 eDMA Interrupt Request Registers (EDMA_IRQRH, EDMA_IRQRL)

The EDMA_IRQRH and EDMA_IRQRL provide a bit map for the 64 channels signaling the presence of

an interrupt request for each channel. For the MPC5554, EDMA_IRQRH supports channels 63–32, while

EDMA_IRQRL covers channels 31–00. For the MPC5553, EDMA_IRQRL maps to channels 31-0.

EDMA_IRQRH is reserved on the MPC5553 and accessing it will result in a bus error.

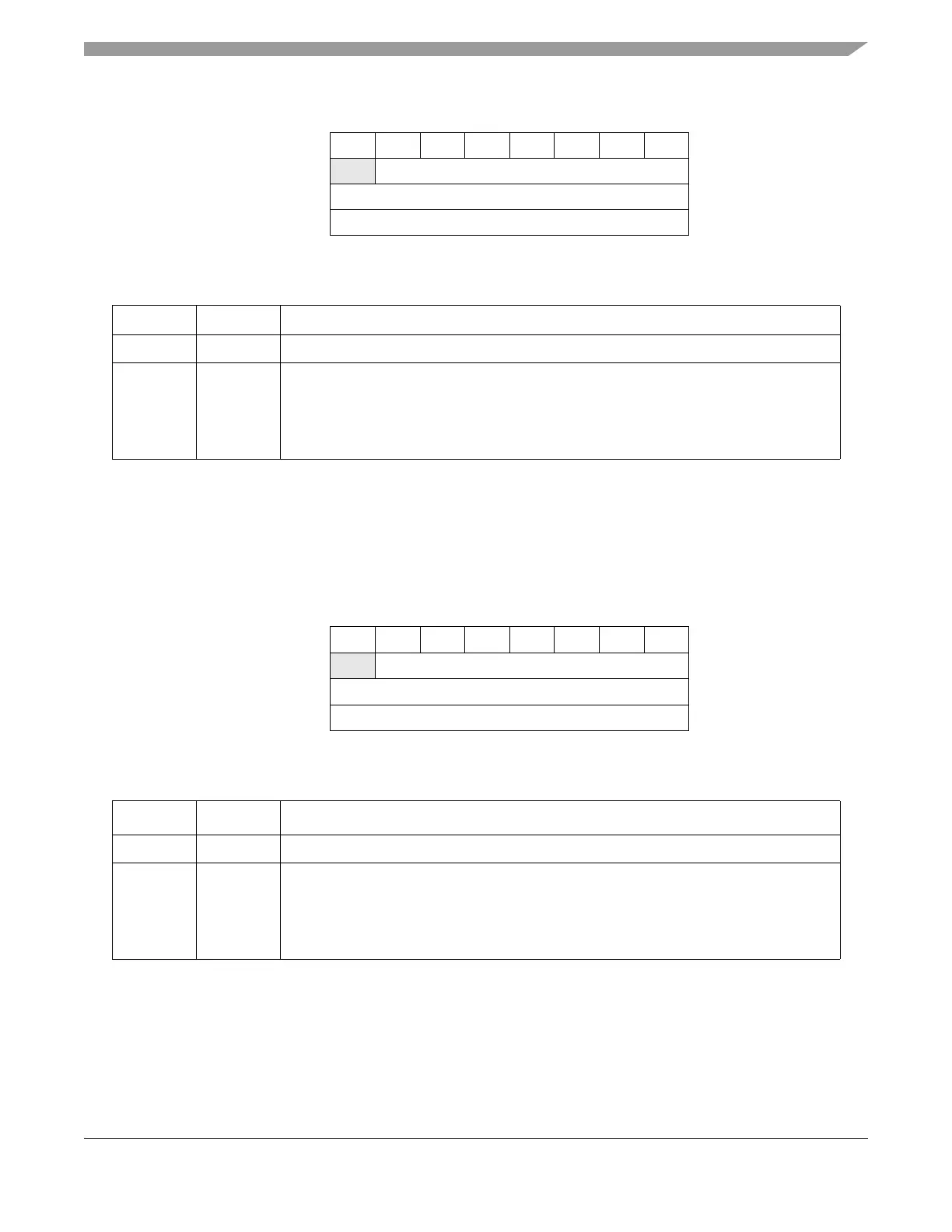

01234567

R00000000

W

SSB[0:6]

Reset00000000

Reg Addr Base + 0X001E

Figure 9-14. eDMA Set START Bit Register (EDMA_SSBR)

Table 9-12. EDMA_SSBR Field Descriptions

Bits Name Description

0 — Reserved.

1–7 SSB

[0:6]

Set START bit (channel service request).

0–63 Set the corresponding channel’s TCD.START

64–127 Set all TCD.START bits

Note: For the MPC5553, the value 32-63 [bit 2 (SSB1)] is reserved.

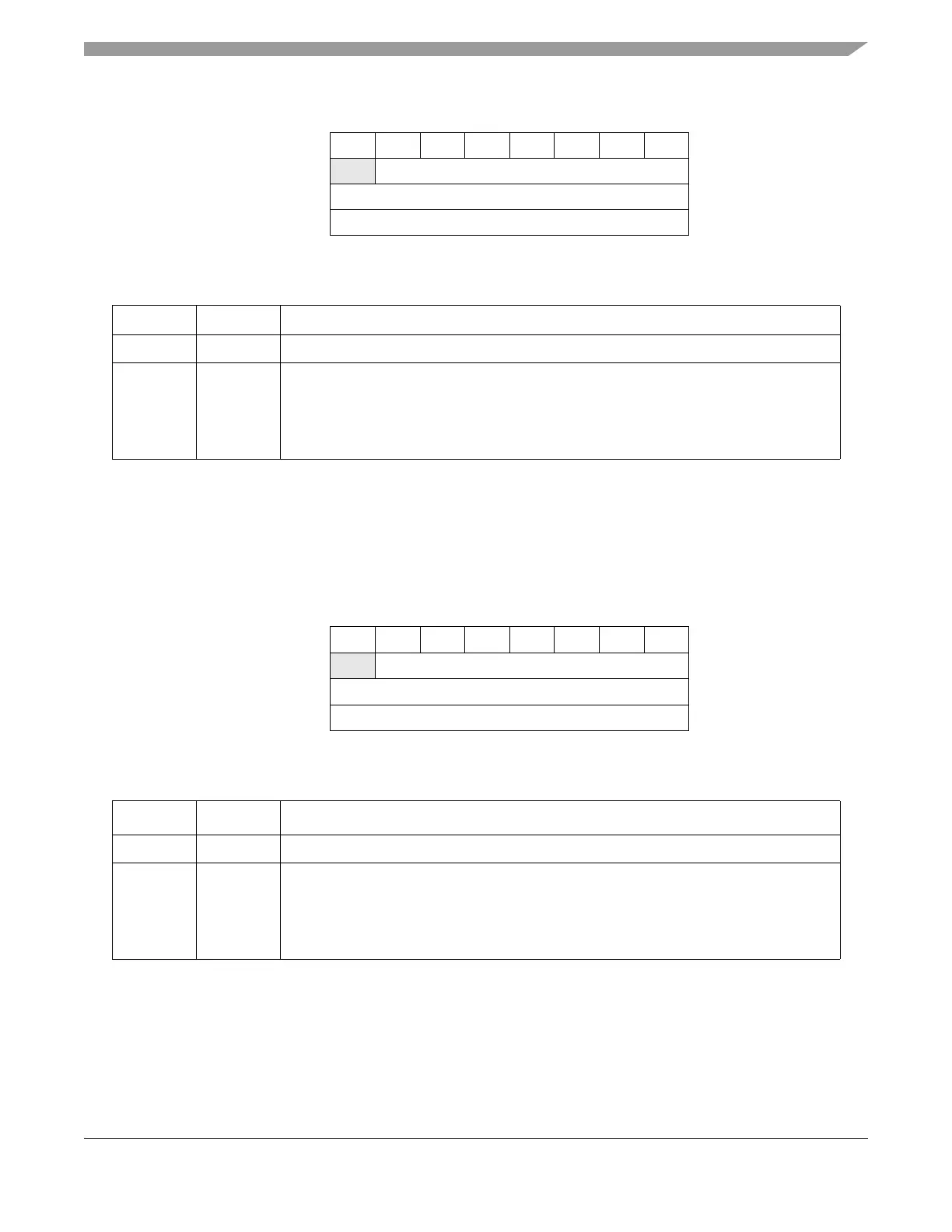

01234567

R00000000

W CDSB[0:6]

Reset00000000

Reg Addr Base + 0X001F

Figure 9-15. eDMA Clear DONE Status Bit Register (EDMA_CDSBR)

Table 9-13. EDMA_CDSBR Field Descriptions

Bits Name Description

0 — Reserved.

1–7 CDSB

[0:6]

Clear DONE status bit.

0–63 Clear the corresponding channel’s DONE bit

64–127 Clear all TCD DONE bits

Note: For the MPC5553, the value 32-63 [bit 2 (CDSB1)] is reserved.

Loading...

Loading...