MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

9-20 Freescale Semiconductor

The eDMA engine signals the occurrence of a programmed interrupt upon the completion of a data transfer

as defined in the transfer control descriptor by setting the appropriate bit in this register. The outputs of

this register are directly routed to the interrupt controller (INTC). During the execution of the interrupt

service routine associated with any given channel, it is software’s responsibility to clear the appropriate

bit, negating the interrupt request. Typically, a write to the EDMA_CIRQR in the interrupt service routine

is used for this purpose.

The state of any given channel’s interrupt request is directly affected by writes to this register; it is also

affected by writes to the EDMA_CIRQR. On writes to the EDMA_IRQRH or EDMA_IRQRL, a 1 in any

bit position clears the corresponding channel’s interrupt request. A 0 in any bit position has no affect on

the corresponding channel’s current interrupt status. The EDMA_CIRQR is provided so the interrupt

request for a single channel can easily be cleared.

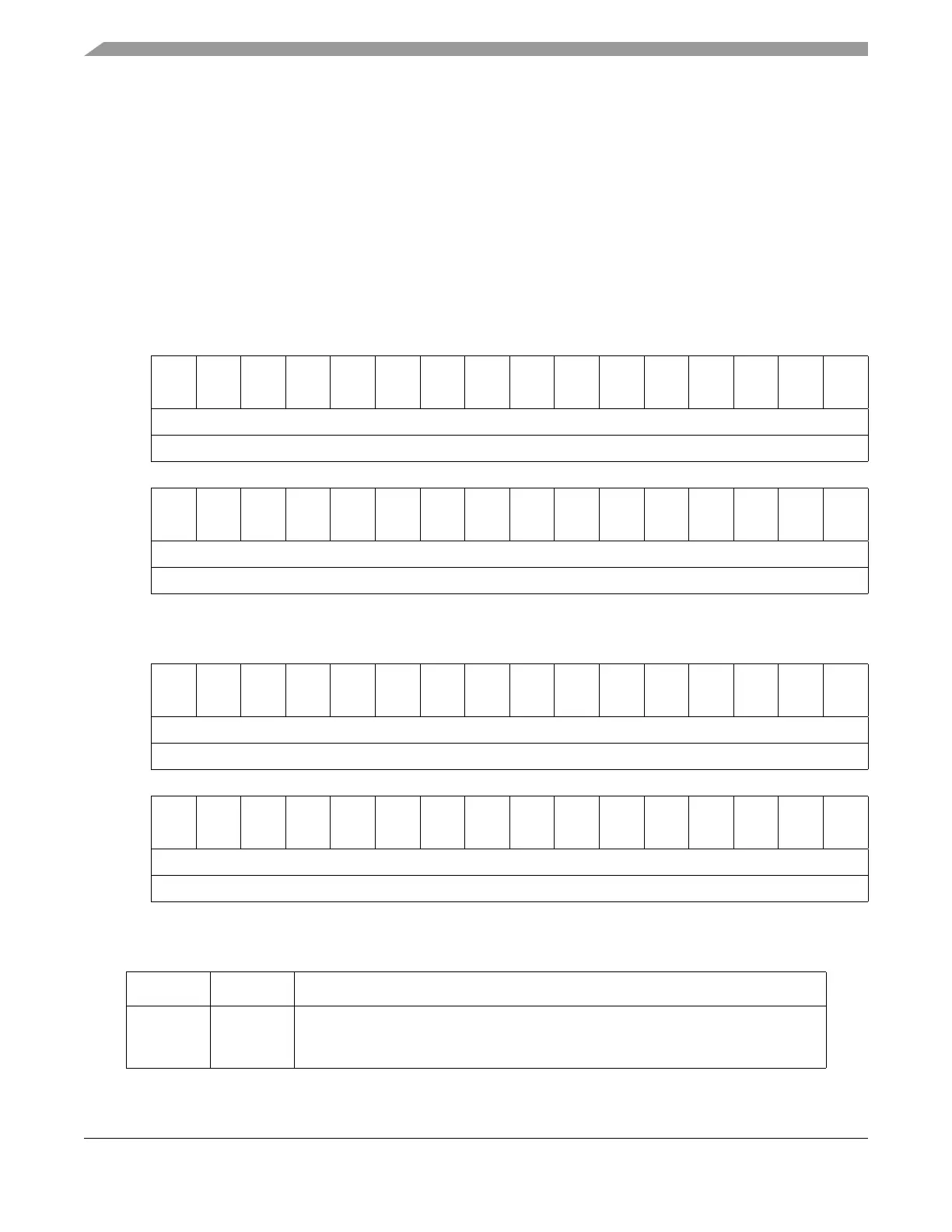

0123456789101112131415

RINT

63

INT

62

INT

61

INT

60

INT

59

INT

58

INT

57

INT

56

INT

55

INT

54

INT

53

INT

52

INT

51

INT

50

INT

49

INT

48

W

Reset0000000000000000

Reg Addr Base + 0x0020

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RINT

47

INT

46

INT

45

INT

44

INT

43

INT

42

INT

41

INT

40

INT

39

INT

38

INT

37

INT

36

INT

35

INT

34

INT

33

INT

32

W

Reset0000000000000000

Reg Addr Base + 0x0020

Figure 9-16. eDMA Interrupt Request High Register (EDMA_IRQRH)—MPC5554 Only

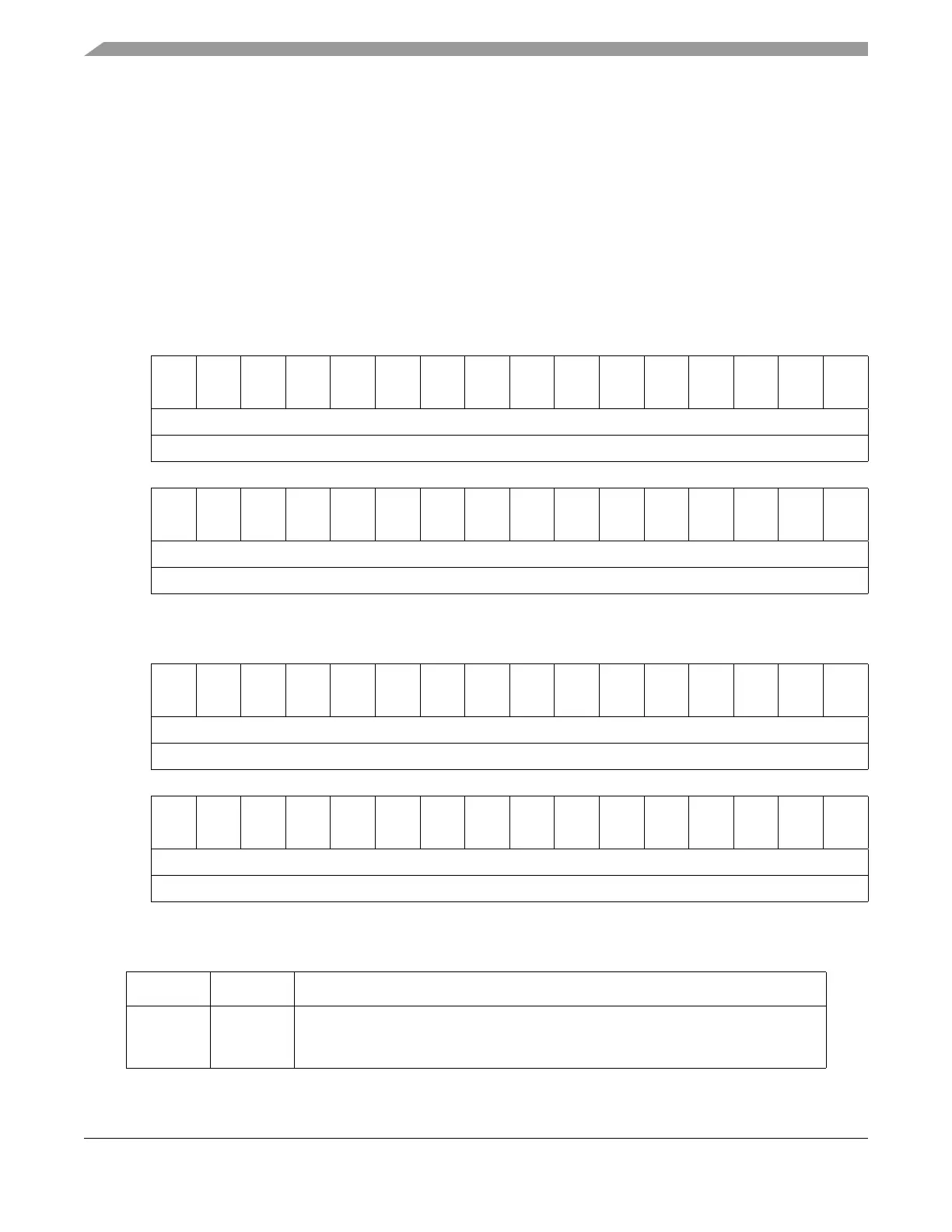

0123456789101112131415

RINT

31

INT

30

INT

29

INT

28

INT

27

INT

26

INT

25

INT

24

INT

23

INT

22

INT

21

INT

20

INT

19

INT

18

INT

17

INT

16

W

Reset0000000000000000

Reg Addr Base + 0x0024

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

RINT

15

INT

14

INT

13

INT

12

INT

11

INT

10

INT

09

INT

08

INT

07

INT

06

INT

05

INT

04

INT

03

INT

02

INT

01

INT

00

W

Reset0000000000000000

Reg Addr Base + 0x0024

Figure 9-17. eDMA Interrupt Request Low Register (EDMA_IRQRL)

Table 9-14. EDMA_IRQRH, EDMA_IRQRL Field Descriptions

Bits Name Description

0–31 INTn eDMA interrupt request n.

0 The interrupt request for channel n is cleared.

1 The interrupt request for channel n is active.

Loading...

Loading...