MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

Freescale Semiconductor 22-29

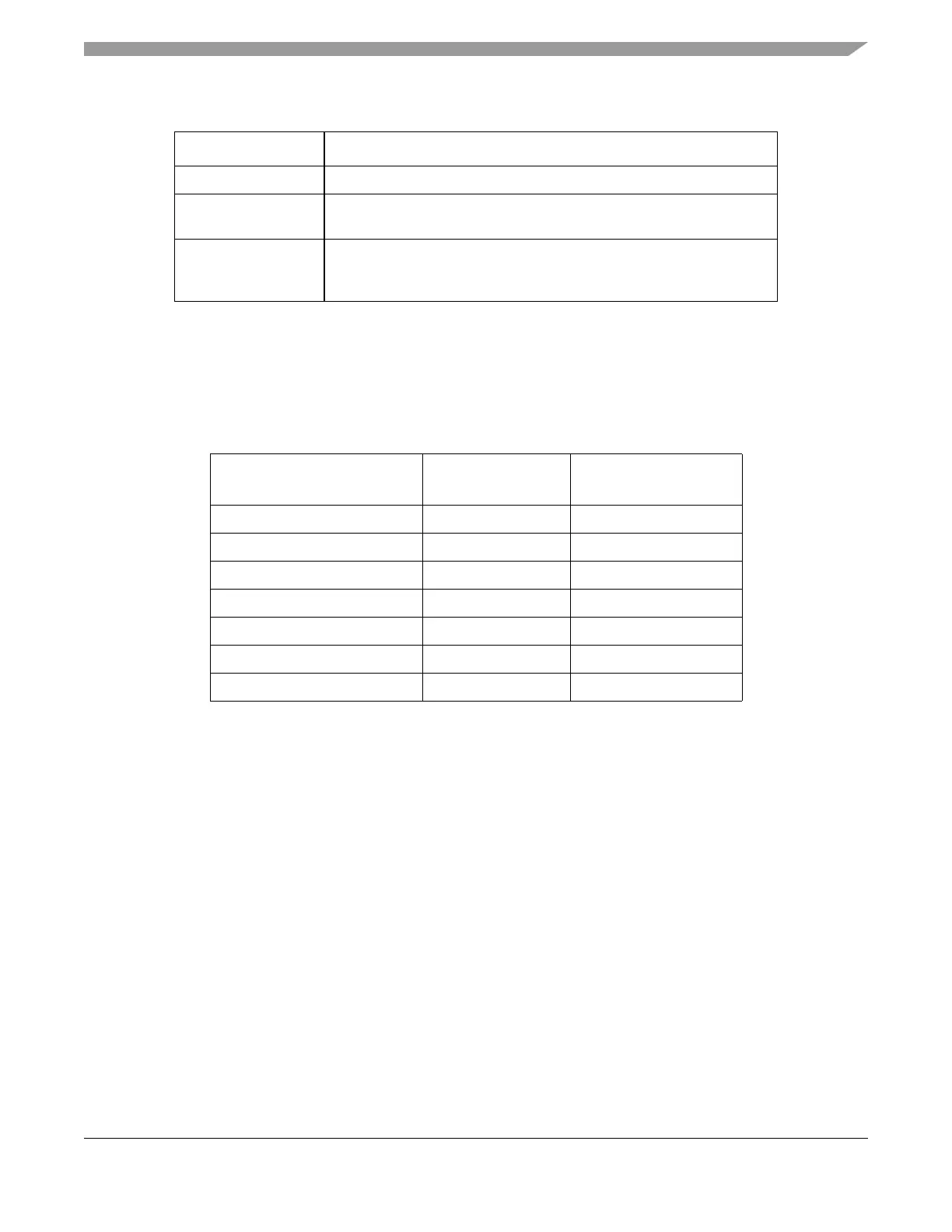

Table 22-17 gives an overview of the CAN compliant segment settings and the related parameter values.

NOTE

It is the user’s responsibility to ensure the bit time settings are in compliance

with the CAN standard.

22.4.5.5 Arbitration and Matching Timing

During normal transmission or reception of frames, the arbitration, match, move in and move out processes

are executed during certain time windows inside the CAN frame, as shown in Figure 22-14. When doing

matching and arbitration, FlexCAN2 needs to span the whole message buffer memory during the available

time slot. In order to have sufficient time to do that, the following restrictions must be observed:

• A valid CAN bit timing must be programmed, as indicated in Figure 22-14.

• The system clock frequency cannot be smaller than the oscillator clock frequency, i.e. the PLL

cannot be programmed to divide down the oscillator clock.

• There must be a minimum ratio of 16 between the system clock frequency and the CAN bit rate.

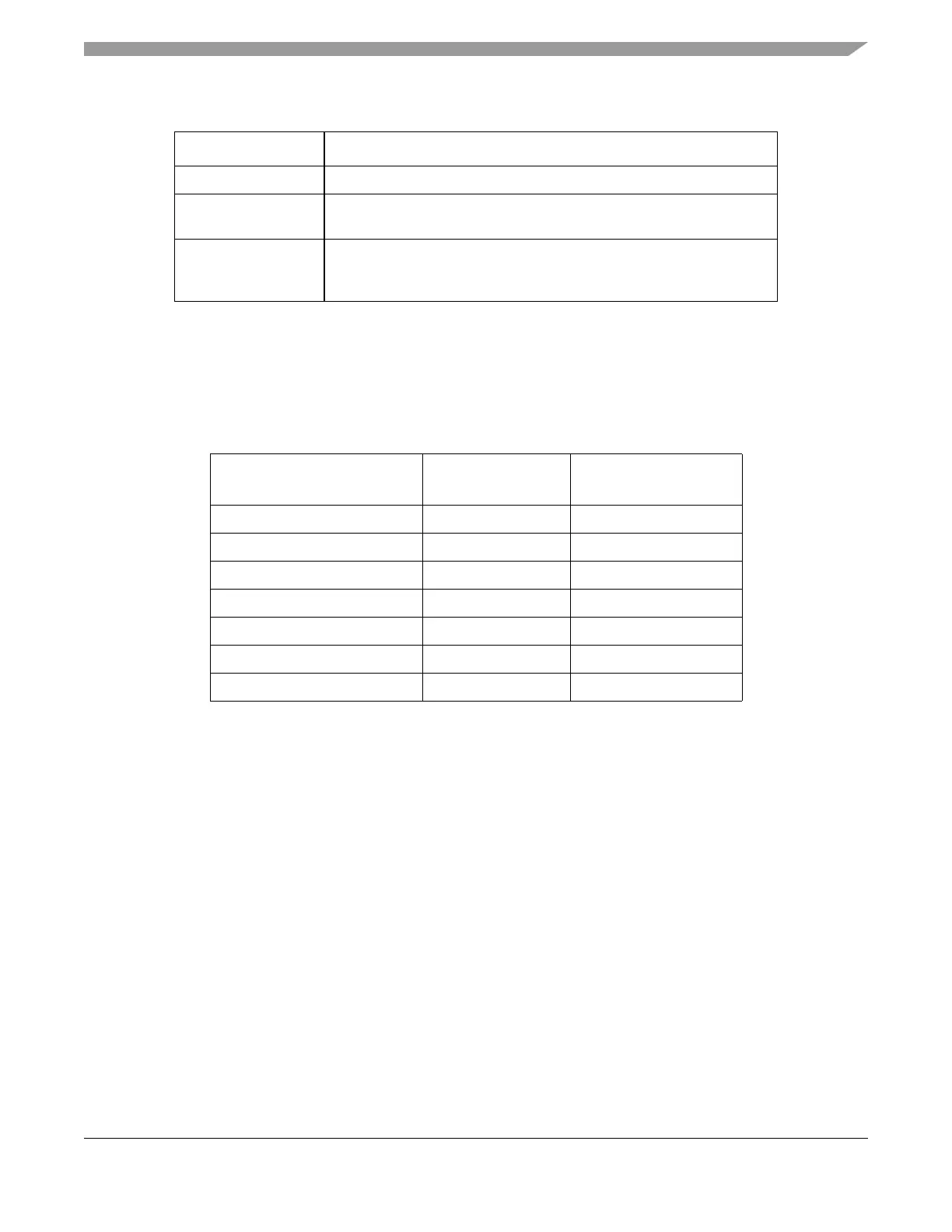

Table 22-16. Time Segment Syntax

Syntax Description

SYNCSEG System expects transitions to occur on the bus during this period.

Transmit Point A node in transmit mode transfers a new value to the CAN bus at this

point.

Sample Point A node in receive mode samples the bus at this point. If the three

samples per bit option is selected, then this point marks the position of

the third sample.

Table 22-17. CAN Standard Compliant Bit Time Segment Settings

Time Segment 1 Time Segment 2

Resynchronization

Jump Width

5 .. 10 2 1 .. 2

4 .. 11 3 1 .. 3

5 .. 12 4 1 .. 4

6 .. 13 5 1 .. 4

7 .. 14 6 1 .. 4

8 .. 15 7 1 .. 4

9 .. 16 8 1 .. 4

Loading...

Loading...