MPC5553/MPC5554 Microcontroller Reference Manual, Rev. 5

3-12 Freescale Semiconductor

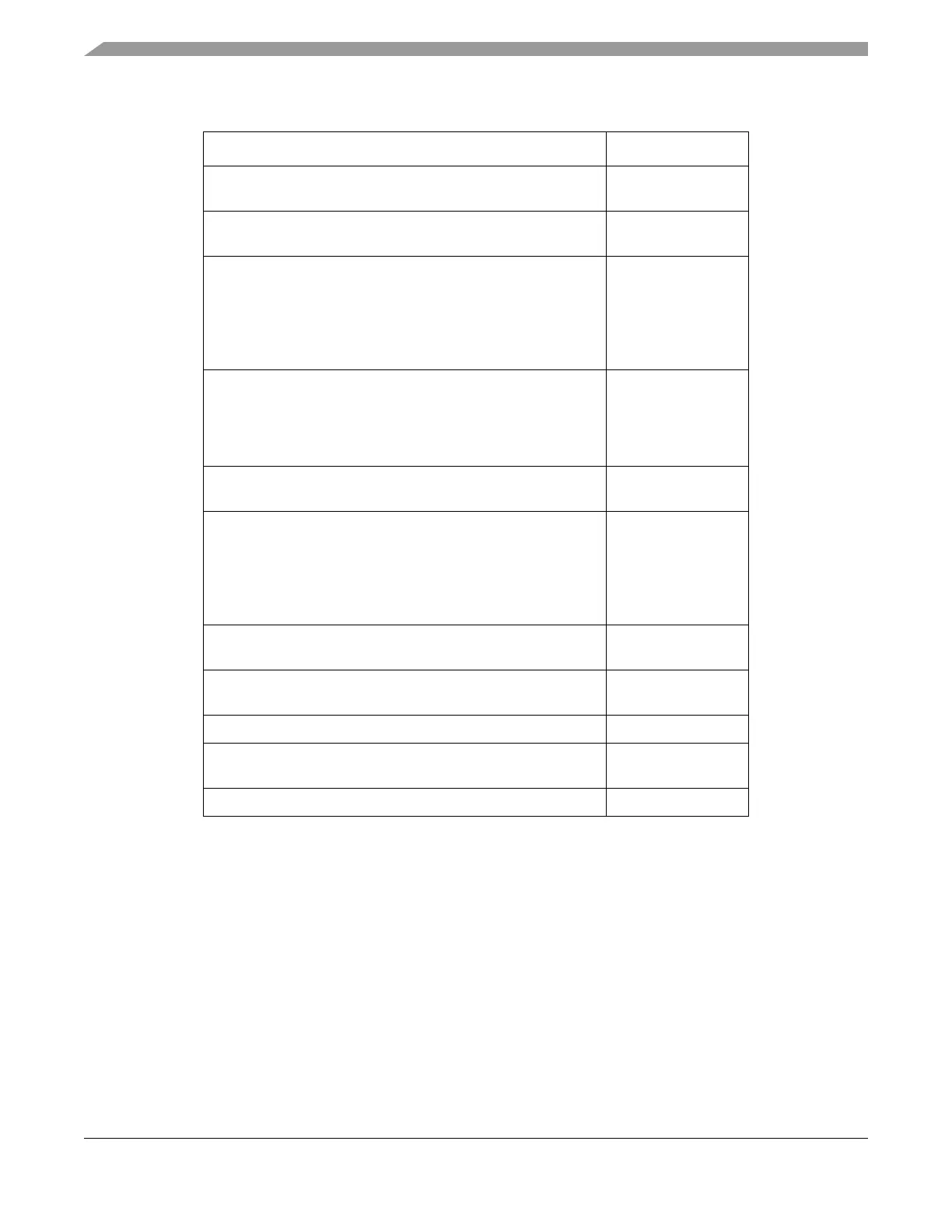

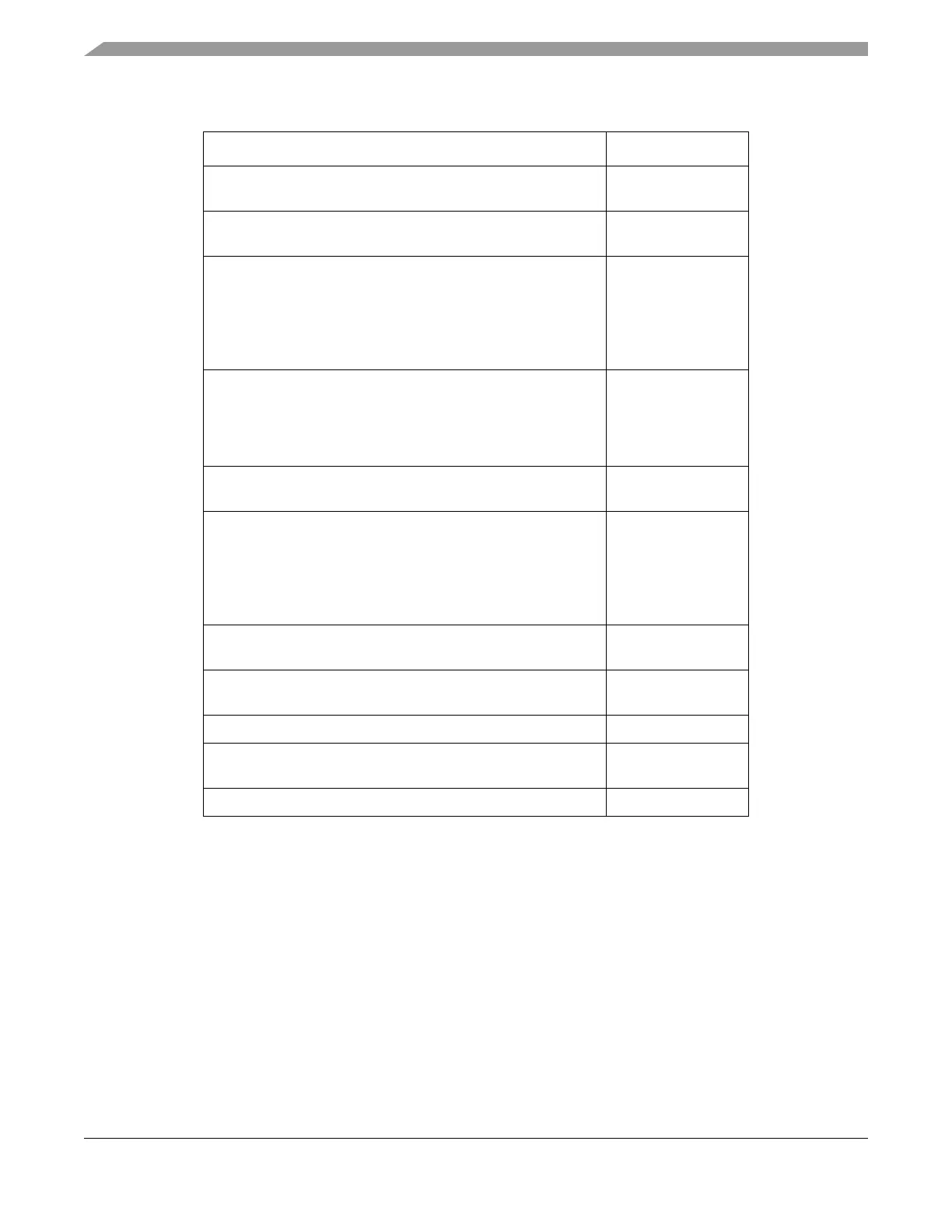

Table 3-1. e200z6 Features Not Supported in the MPC5553/MPC5554 Core

Description Function / Category

These events are disabled: External Debug Event (DEVT2)

Unconditional Debug Event (UDE)

The e200z6 Core Halted State and Stopped State are not

supported.

Power Management

The following low power modes are not supported:

Doze mode

Nap mode

Sleep mode

Time base interrupt wake-up from low power mode is not

supported.

Power Management

Core wake up is not supported.

The MSR[WE] bit in the Machine State Register is not supported.

The OCR[WKUP] bit in the OnCE Control Register (OCR) has no

effect.

Power Management

The machine check input pin is not supported. HID0 [EMCP] has

no effect, and MCSR[MCP] always reads a negated value.

Machine Check

Least significant halfword of Processor Version Register (PVR)

is 0x 0000, which contains these three bitfields:

MBG Use = 0x00

MBG Rev = 0x0

MBG ID = 0x0

The PVR register has two bitfields in the MPC5553/MPC5554.

PVR Value

Reservation Management logic external to the e200z6 is not

implemented.

Reservation

Management

The System Version Register (SVR) of the e200z6 is

0x 0000_0000

Verification

The Decrementer Counters are always enabled in the e200z6 Time Base

Timer External Clock is not connected to any clock and should

therefore never be selected.

Time Base

The CTXCR and ALTCXTCR registers are not supported. Context Control

Loading...

Loading...